- 您现在的位置:买卖IC网 > PDF目录1999 > ICS97ULP877BKLFT (IDT, Integrated Device Technology Inc)IC CLOCK DRIVER 1.8V LP 40VFQFPN PDF资料下载

参数资料

| 型号: | ICS97ULP877BKLFT |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 11/14页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK DRIVER 1.8V LP 40VFQFPN |

| 产品变化通告: | Product Discontinuation 09/Dec/2011 |

| 标准包装: | 1,000 |

| 类型: | 时钟缓冲器/驱动器,零延迟缓冲器,多路复用器 |

| PLL: | 是 |

| 主要目的: | 存储器,DDR2 |

| 输入: | 时钟 |

| 输出: | SSTL-18 |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:10 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 410MHz |

| 电源电压: | 1.7 V ~ 1.9 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 40-VFQFN 裸露焊盘 |

| 供应商设备封装: | 40-VFQFPN(6x6) |

| 包装: | 带卷 (TR) |

| 其它名称: | 97ULP877BKLFT |

6

ICS97ULP877B

0981C—04/05/05

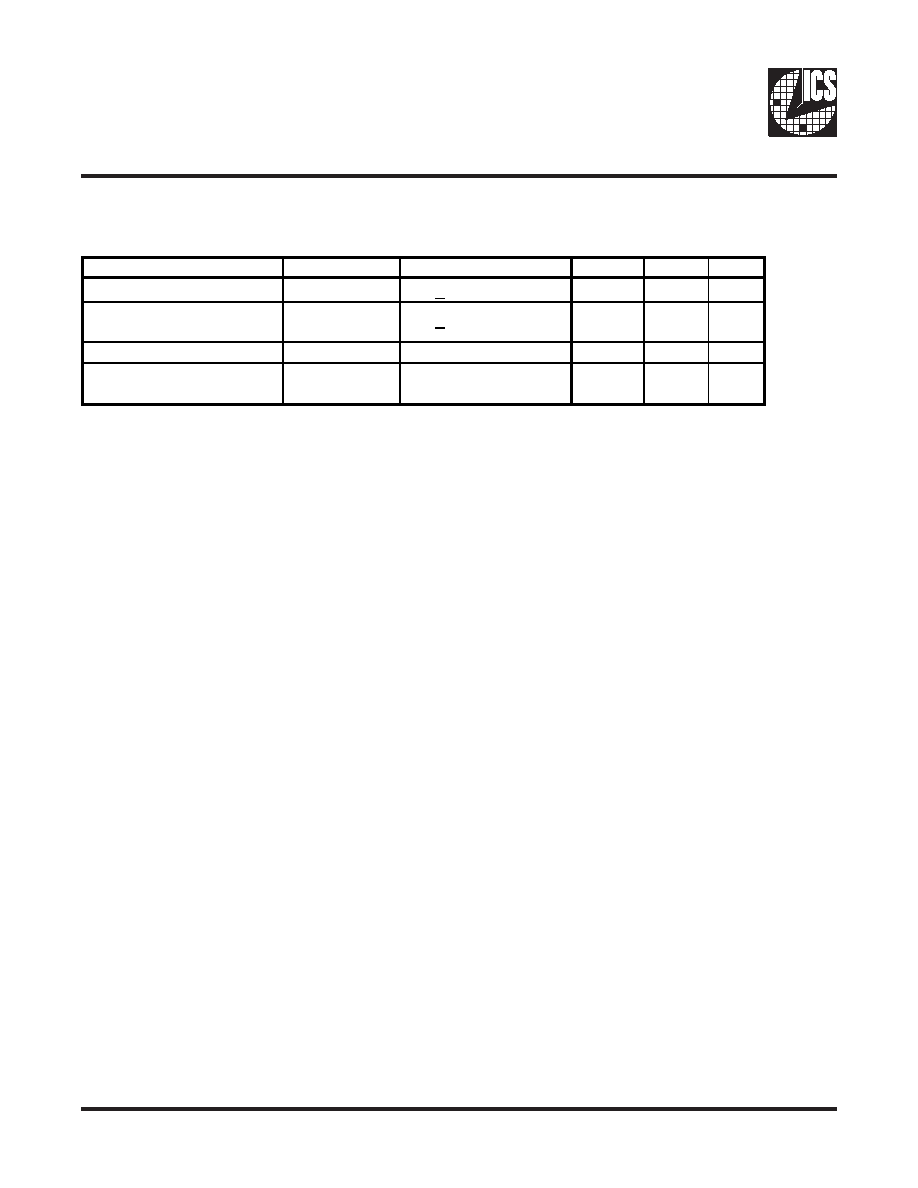

Timing Requirements

TA = 0 - 70°C Supply Voltage AVDD, VDDQ = 1.8 V +/- 0.1V (unless otherwise stated)

PA RA METER

S Y MBOL

CONDITIONS

MIN

MAX

UNITS

Max clock frequency

freqop

1.8V+0.1V @ 25°C

95

410

MHz

Application Frequency

Range

freqApp

1.8V+0.1V @ 25°C

160

410

MHz

Input clock duty cycle

dtin

40

60

%

CLK stabilization

TSTAB

15

s

NOTE: The PLL must be able to handle spread spectrum induced skew.

NOTE: Operating clock frequency indicates a range over which the PLL must be able to lock, but in which it is not

required to meet the other timing parameters. (Used for low speed system debug.)

NOTE: Application clock frequency indicates a range over which the PLL must meet all timing parameters.

NOTE: Stabilization time is the time required for the integrated PLL circuit to obtain phase lock of its feedback

signal to its reference signal, within the value specificied by the Static Phase Offset (

t( ), after power-up. During

normal operation, the stabilization time is also the time required for the integrated PLL circuit to obtain phase lock

of its feedback signal to its reference signal when CK and CK go to a logic low state, enter the power-down mode

and later return to active operation. CK and CK may be left floating after they have been driven low for one

complete clock cycle.

相关PDF资料 |

PDF描述 |

|---|---|

| ICS98UAE877AHLFT | IC CLOCK DRIVER 1.8V LP 52-BGA |

| ICS9DB202CFLF | IC JITTER ATTENUATOR 20-SSOP |

| ICS9DB202CK-01LFT | IC JITTER ATTENUATOR 32-VFQFPN |

| ICS9DB206CLLF | IC JITTER ATTENUATOR 28-TSSOP |

| ICS9DB306BLLFT | IC JITTER ATTENUATOR 28-TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS97ULPA877AHLF | 功能描述:IC CLOCK DRIVER 1.8V LP 52-BGA RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ICS97ULPA877AHLFT | 功能描述:IC CLOCK DRIVER 1.8V LP 52-BGA RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ICS98UAE877AHLF | 功能描述:IC CLOCK DRIVER 1.8V LP 52-BGA RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| ICS98UAE877AHLFT | 功能描述:IC CLOCK DRIVER 1.8V LP 52-BGA RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| ICS98ULPA877AH | 功能描述:IC CLOCK DRIVER 1.8V LP 52-BGA RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。