- 您现在的位置:买卖IC网 > PDF目录79612 > ICS97ULPA877AKLF-T (INTEGRATED DEVICE TECHNOLOGY INC) 97ULP SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC40 PDF资料下载

参数资料

| 型号: | ICS97ULPA877AKLF-T |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 97ULP SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC40 |

| 封装: | ROHS COMPLIANT, PLASTIC, MLF-40 |

| 文件页数: | 13/15页 |

| 文件大小: | 183K |

| 代理商: | ICS97ULPA877AKLF-T |

7

ICS97ULPA877A

1088B—01/18/06

Notes:

1.

Switching characteristics guaranteed for application frequency range.

2.

Static phase offset shifted by design.

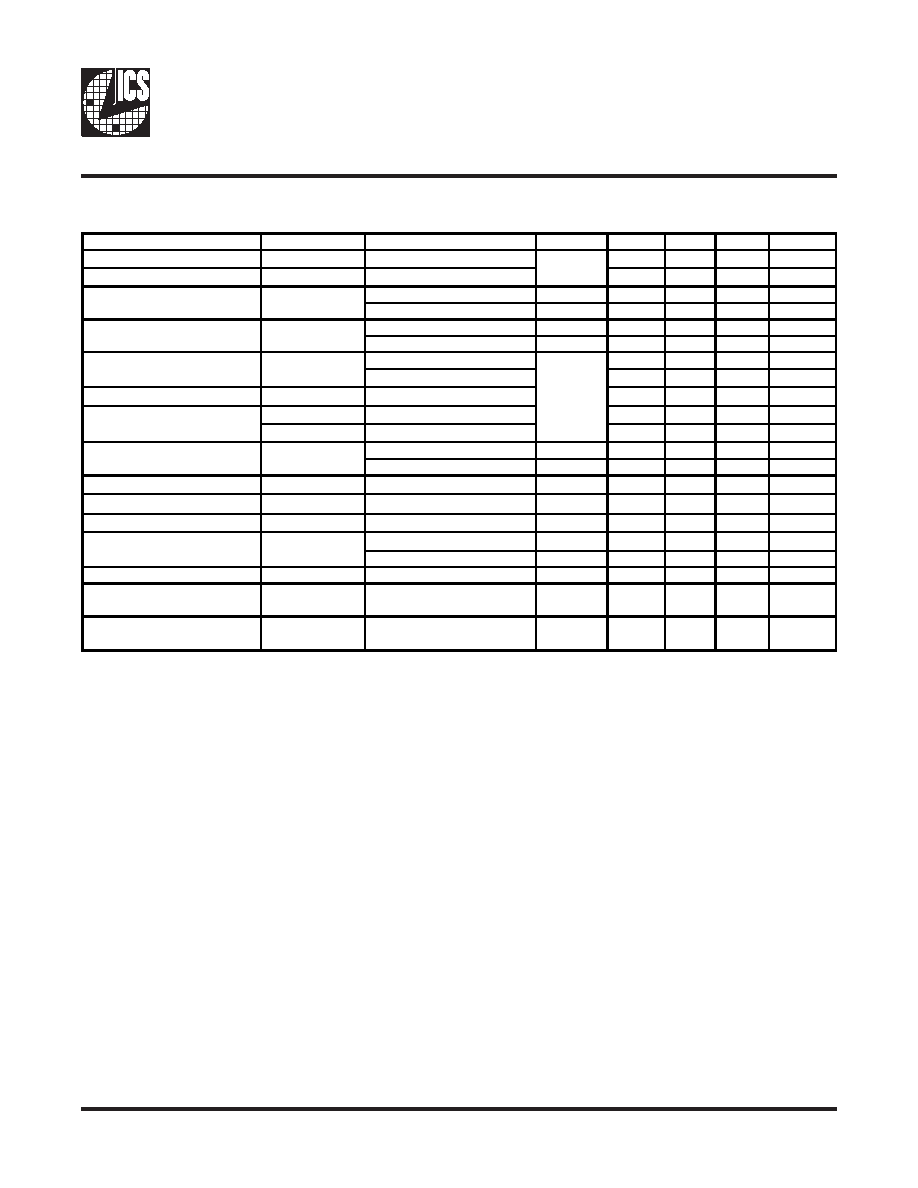

Switching Characteristics

1

TA = 0 - 70°C Supply Voltage AVDD, VDDQ = 1.8 V +/- 0.1V (unless otherwise stated)

PARAMETER

SYMBOL

CONDITION

(MHz)

MIN

TYP

MAX

UNITS

Output enable time

ten

OE to any output

4.73

8

ns

Output disable time

tdis

OE to any output

5.82

8

ns

160 to 270

-40

40

ps

271 to 410

-30

30

ps

160 to 270

-60

60

ps

271 to 410

-50

50

ps

Input Clock

1

2.5

4

v/ns

Output Enable (OE), (OS)

0.5

v/ns

Output clock slew rate

SLr1(o)

1.5

2.5

3

v/ns

tjit(cc+)

040

ps

tjit(cc-)

0

-40

ps

160 to 270

-50

50

ps

271 to 410

-20

20

ps

Static Phase Offset

tSPO

2

271 to 410

-50

0

50

ps

t jit (per) + t ()dyn + t skew(o)

∑(su)

80

ps

t()dyn + tskew(o)

∑

t (h)

60

ps

160 to 270

40

ps

271 to 410

30

ps

SSC modulation frequency

30.00

33

kHz

SSC clock input frequency

deviation

0.00

-0.50

%

PLL Loop bandwidth (-3 dB

from unity gain)

2.0

MHz

Output to Output Skew

tskew

160 to 410

Period jitter

tjit (per)

Input slew rate

SLr1(i)

160 to 410

Cycle-to-cycle period jitter

Dynamic Phase Offset

t()dyn

Half-period jitter

tjit(hper)

相关PDF资料 |

PDF描述 |

|---|---|

| ICS9112AF-17T | 9112 SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS97U877AH | 97U SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA52 |

| ICS91305AMLFT | 91305 SERIES, PLL BASED CLOCK DRIVER, 5 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| ICS97U870AHIT | 97U SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA52 |

| ICS97U877AKI | 97U SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC40 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS98UAE877AHLF | 功能描述:IC CLOCK DRIVER 1.8V LP 52-BGA RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| ICS98UAE877AHLFT | 功能描述:IC CLOCK DRIVER 1.8V LP 52-BGA RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| ICS98ULPA877AH | 功能描述:IC CLOCK DRIVER 1.8V LP 52-BGA RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ICS98ULPA877AHI | 功能描述:IC CLOCK DRIVER 1.8V LP 52-BGA RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ICS98ULPA877AHILF | 制造商:Integrated Device Technology Inc 功能描述:IC CLK DVR DDR-II PLL 52BGA 制造商:Integrated Device Technology Inc 功能描述:IC CLOCK DRIVER 1.8V LP 52-BGA |

发布紧急采购,3分钟左右您将得到回复。