- 您现在的位置:买卖IC网 > PDF目录65536 > ICSSSTVA32852YHLF-T (INTEGRATED DEVICE TECHNOLOGY INC) SSTV SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA114 PDF资料下载

参数资料

| 型号: | ICSSSTVA32852YHLF-T |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 锁存器 |

| 英文描述: | SSTV SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA114 |

| 封装: | LEAD FREE, BGA-114 |

| 文件页数: | 1/7页 |

| 文件大小: | 120K |

| 代理商: | ICSSSTVA32852YHLF-T |

Integrated

Circuit

Systems, Inc.

ICSSSTVA32852

0918A—04/30/04

Recommended Application:

DDR Memory Modules for DDR 266/333/400

Provides complete DDR DIMM logic solution with

ICS93V857 or ICS95V857

SSTL_2 compatible data registers

Product Features:

Differential clock signals

Supports SSTL_2 class II specifications on inputs

and outputs

Low-voltage operation

- VDD = 2.3V to 2.7V

Available in 114 ball BGA package.

Advanced speed feature provides more timing

margin for PC3200 applications

Exceeds SSTVN32852 performance

DDR 24-Bit to 48-Bit Registered Buffer

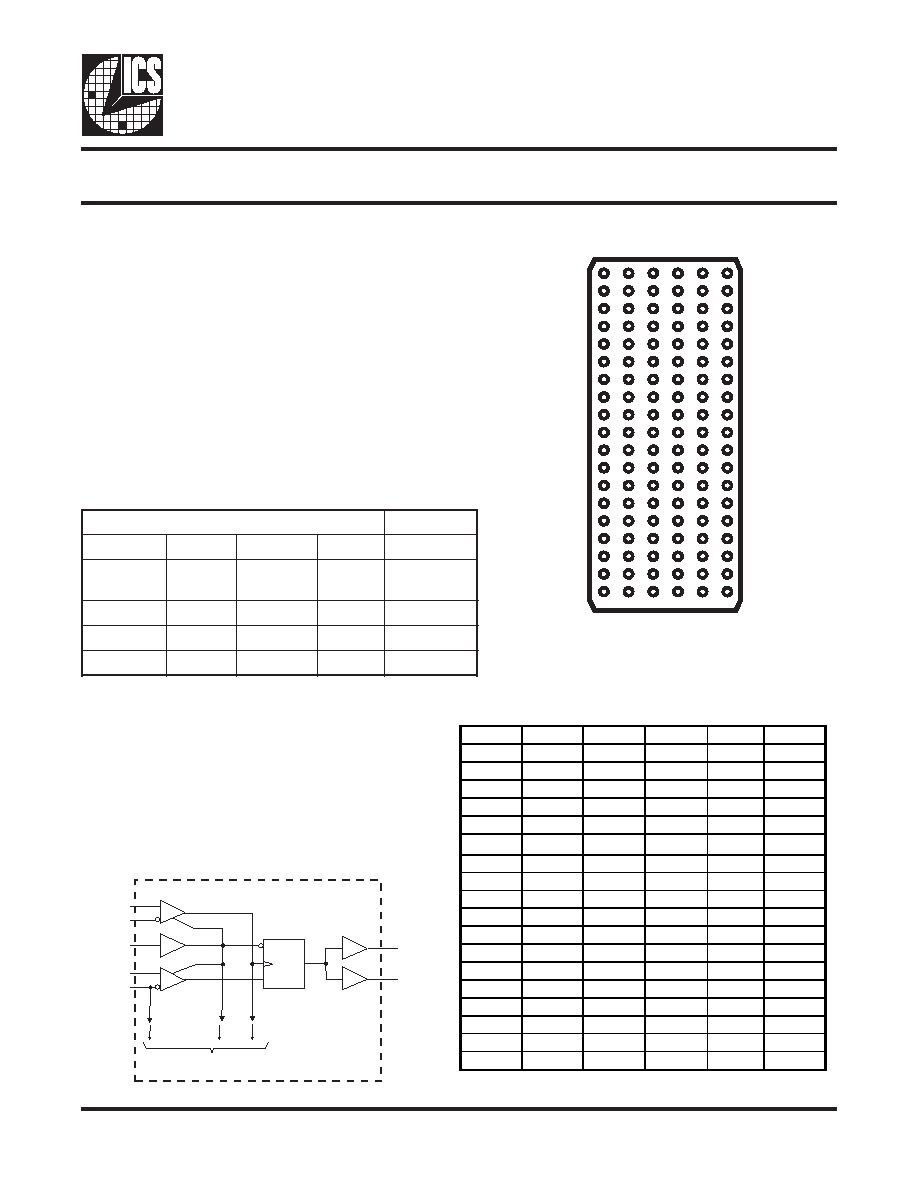

Truth Table

1

Block Diagram

Notes:

1.

H = "High" Signal Level

L = "Low" Signal Level

↑ = Transition "Low"-to-"High"

↓ = Transition "High"-to-"Low"

X = Don't Care

2.

Output level before the indicated

steady state input conditions were

established.

CLK

CLK#

D1

VREF

RESET#

To 23 Other Channels

Q1A

Q1B

CLK

R

D1

A

B

123456

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Pin Configuration

114-Pin Ball BGA

s

t

u

p

n

Is

t

u

p

t

u

O

Q

#

T

E

S

E

RK

L

C#

K

L

CD

Q

L

r

o

X

g

n

i

t

a

o

l

F

r

o

X

g

n

i

t

a

o

l

F

r

o

X

g

n

i

t

a

o

l

F

L

H

↑↓

HH

H

↑↓

LL

HH

r

o

LH

r

o

LX

Q0 )

2

(

Pin Configuration Assignments

1

234

5

6

A

Q2A

Q1A

CLK

CLK#

Q1B

Q2B

B

Q3A

VDDQ

GND

VDDQ

Q3B

C

Q5A

Q4A

VDDQ

Q4B

Q5B

D

Q7A

Q6A

GND

Q6B

Q7B

E

Q8A

GND

VDDQ

GND

Q8B

F

Q10A

Q9A

VDDQ

Q9B

Q10B

G

Q12A

Q11A

GND

Q11B

Q12B

H

Q13A

VDD

VDDQ

VDD

Q13B

J

Q14A

Q15A

GND

Q15B

Q14B

K

Q17A

Q16A

VDDQ

Q16B

Q17B

L

Q18A

Q19A

GND

Q19B

Q18B

M

Q20A

VDDQ

GND

VDDQ

Q20B

N

Q22A

Q21A

VDDQ

Q21B

Q22B

P

Q23A

VDDQ

GND

VDDQ

Q23B

R

Q24A

VDD

RESET#

VREF

VDD

Q24B

T

D2

D1

D6

D18

D13

D14

U

D4

D3

D10

D22

D15

D16

V

D5

D7

D11

D23

D19

D17

W

D8

D9

D12

D24

D21

D20

相关PDF资料 |

PDF描述 |

|---|---|

| ICSSSTVF16859AYKLF-T | SSTV SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, QCC56 |

| ICSSSTVF16859AYGLF-T | SSTV SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PDSO64 |

| ICSSSTVF16859YGLF-T | SSTV SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PDSO64 |

| ICSSSTVF16859YKLF | SSTV SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, QCC56 |

| ICSVF2509BGLN | 2509 SERIES, PLL BASED CLOCK DRIVER, 9 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO24 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICSSSTVF16859 | 制造商:ICS 制造商全称:ICS 功能描述:DDR 13-Bit to 26-Bit Registered Buffer |

| ICSSSTVF16859BKLFT | 制造商:ICS 功能描述: |

| ICSSSTVF16859BKT | 制造商:ICS 功能描述: |

| ICSSSTVF16859YK | 制造商:ICS 制造商全称:ICS 功能描述:DDR 13-Bit to 26-Bit Registered Buffer |

| ICSS-VE-PU-N | 制造商:Black Box Corporation 功能描述:iCOMPEL S Series VESA Publisher |

发布紧急采购,3分钟左右您将得到回复。