- 您现在的位置:买卖IC网 > PDF目录131792 > IDT54FCT162511CTEB (INTEGRATED DEVICE TECHNOLOGY INC) FAST CMOS 16-BIT REGISTERED/LATCHED TRANSCEIVER WITH PARITY PDF资料下载

参数资料

| 型号: | IDT54FCT162511CTEB |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 总线收发器 |

| 英文描述: | FAST CMOS 16-BIT REGISTERED/LATCHED TRANSCEIVER WITH PARITY |

| 中文描述: | FCT SERIES, 16-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, CDFP56 |

| 封装: | CERPACK-56 |

| 文件页数: | 1/10页 |

| 文件大小: | 122K |

| 代理商: | IDT54FCT162511CTEB |

1

IDT54/74FCT162511AT/CT

FASTCMOS16-BITREGISTERED/LATCHEDTRANSCEIVER

MILITARYANDINDUSTRIALTEMPERATURERANGES

MAY 2001

IDT54/74FCT162511AT/CT

MILITARY AND INDUSTRIAL TEMPERATURE RANGES

FAST CMOS 16-BIT

REGISTERED/LATCHED

TRANSCEIVER WITH PARITY

DESCRIPTION:

The FCT162511T 16-bit registered/latched transceiver with parity is built

using advanced dual metal CMOS technology. This high-speed, low-power

transceiver combines D-type latches and D-type flip-flops to allow data flow in

transparent, latched, or clocked modes. The device has a parity generator/

checkerintheA-to-BdirectionandaparitycheckerintheB-to-Adirection. Error

checkingisdoneatthebytelevelwithseparateparitybitsforeachbyte. Separate

error flags exits for each direction with a single error flag indicating an error for

either byte in the A-to-B direction and a second error flag indicating an error for

either byte in the B-to-A direction. The parity error flags are open drain outputs

whichcanbetiedtogetherand/ortiedwithflagsfromotherdevicestoformasingle

error flag or interrupt. The parity error flags are enabled by the

OExx control

pins allowing the designer to disable the error flag during combinational

transitions.

The control pins LEAB, CLKAB, and

OEAB control operation in the A-to-B

direction while LEBA, CLKBA, and

OEBA control the B-to-A direction. GEN/

CHK is only for the selection of A-to-B operation. The B-to-A direction is always

incheckingmode. TheODD/

EVENselectiscommonbetweenthetwodirections.

Except for the ODD/

EVEN control, independent operation can be achieved

between the two directions by using the corresponding control lines.

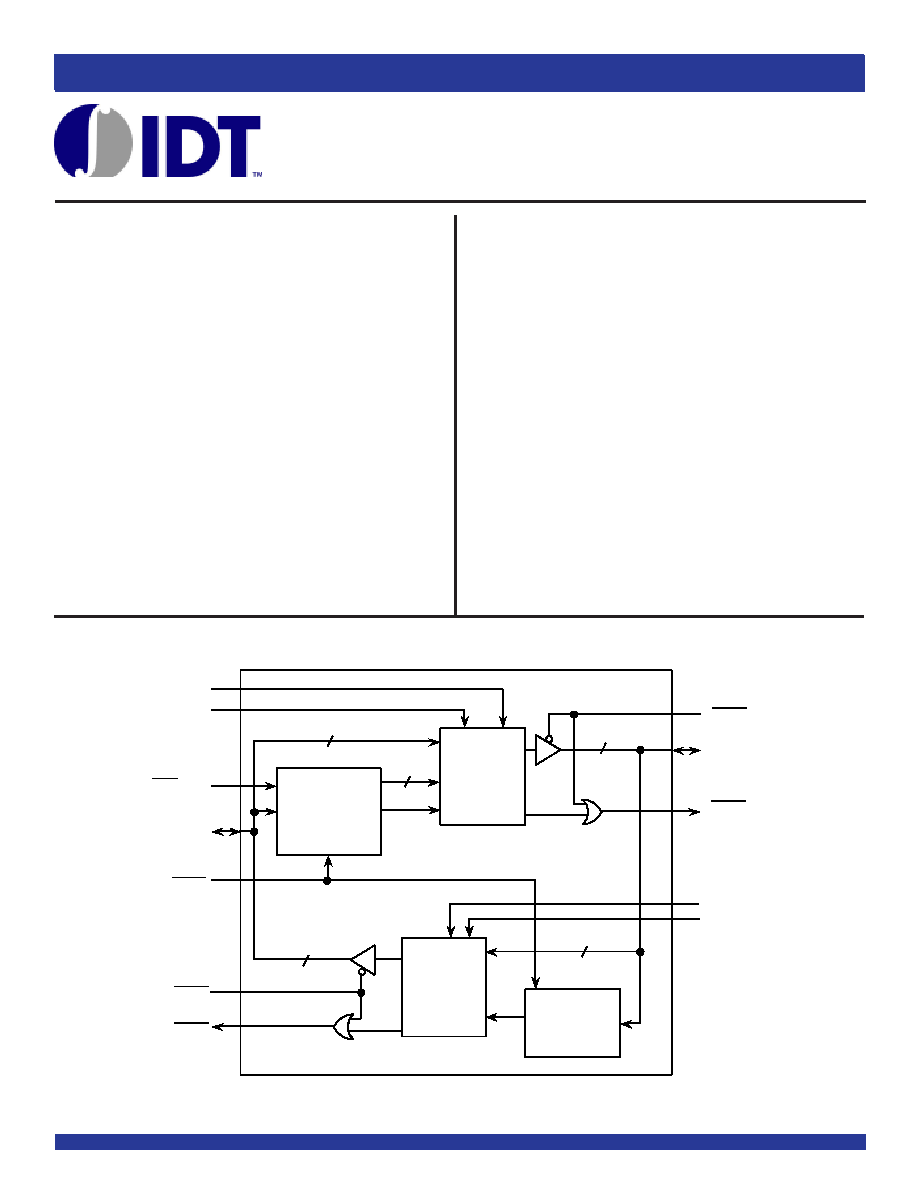

GEN/CHK

Latch/

R egister

Byte

Parity

Generator/

Checker

Latch/

Register

Byte

Parity

Checking

B0-15

A0-15

PA1,2

PB1,2

PER B

LEA B

CLKAB

OEAB

OEBA

PER A

LEB A

CLKB A

Parity, data

Parity, Data

Data

(Open D rain)

(Open Drain)

Parity

ODD/EVEN

16

18

2

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

2001 Integrated Device Technology, Inc.

DSC-2916/2

FEATURES:

0.5 MICRON CMOS Technology

Typical tsk(o) (Output Skew) < 250ps, clocked mode

Low input and output leakage

≤≤≤≤≤1A (max)

ESD > 2000V per MIL-STD-883, Method 3015; > 200V using

machine model (C = 200pF, R = 0)

VCC = 5V ±10%

Balanced Output Drivers:

– ±24mA (industrial)

– ±16mA (military)

Series current limiting resistors

Generate/Check, Check/Check modes

Open drain parity error allows wire-OR

Available in the following packages:

– Industrial: SSOP, TSSOP

– Military: CERPACK

FUNCTIONAL BLOCK DIAGRAM

相关PDF资料 |

PDF描述 |

|---|---|

| ILD255-X019T | 2 CHANNEL AC INPUT-TRANSISTOR OUTPUT OPTOCOUPLER |

| ILD615-3X007 | 2 CHANNEL TRANSISTOR OUTPUT OPTOCOUPLER |

| IL217AT | 1 CHANNEL TRANSISTOR OUTPUT OPTOCOUPLER |

| ILD615-2-X017T | 2 CHANNEL TRANSISTOR OUTPUT OPTOCOUPLER |

| ILD615-4-X007T | 2 CHANNEL TRANSISTOR OUTPUT OPTOCOUPLER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT54FCT162511CTPA | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:FAST CMOS 16-BIT REGISTERED/LATCHED TRANSCEIVER WITH PARITY |

| IDT54FCT162511CTPAB | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:FAST CMOS 16-BIT REGISTERED/LATCHED TRANSCEIVER WITH PARITY |

| IDT54FCT162511CTPF | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:FAST CMOS 16-BIT REGISTERED/LATCHED TRANSCEIVER WITH PARITY |

| IDT54FCT162511CTPFB | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:FAST CMOS 16-BIT REGISTERED/LATCHED TRANSCEIVER WITH PARITY |

| IDT54FCT162511CTPV | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:FAST CMOS 16-BIT REGISTERED/LATCHED TRANSCEIVER WITH PARITY |

发布紧急采购,3分钟左右您将得到回复。