- 您现在的位置:买卖IC网 > PDF目录65576 > IDT5V9352PFI8 (INTEGRATED DEVICE TECHNOLOGY INC) 5V SERIES, PLL BASED CLOCK DRIVER, 11 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 PDF资料下载

参数资料

| 型号: | IDT5V9352PFI8 |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 5V SERIES, PLL BASED CLOCK DRIVER, 11 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 |

| 封装: | TQFP-32 |

| 文件页数: | 1/10页 |

| 文件大小: | 95K |

| 代理商: | IDT5V9352PFI8 |

1

INDUSTRIALTEMPERATURERANGE

IDT5V9352

3.3V/2.5V PHASE-LOCK LOOP CLOCK DRIVER ZERO DELAY BUFFER

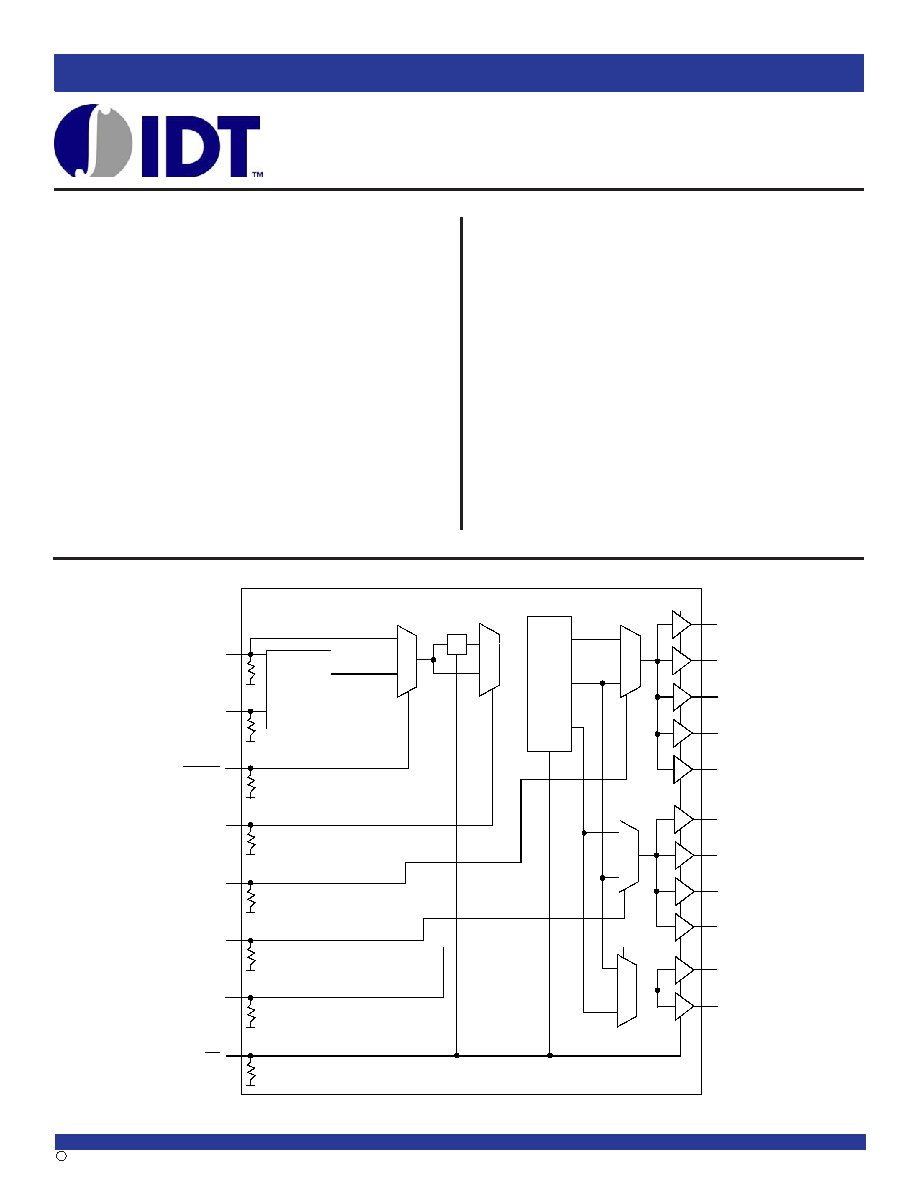

÷6

÷4

÷2

VCO

1

0

1

0

CCLK

QB3

QB0

QB1

QB2

QA0

QA1

QA2

QA3

QA4

QC1

QC0

1

0

BANK A

BANK B

BANK C

1

0

1

0

PLL_En

REFCLK

FBIN

VCO_SEL

fSELA

fSELB

MR/OE

fSELC

PLL

REF

FB

AUGUST 2003

2003

Integrated Device Technology, Inc.

DSC 5973/19

c

IDT5V9352

INDUSTRIAL TEMPERATURE RANGE

3.3V/2.5V PHASE-LOCK

LOOP CLOCK DRIVER

ZERO DELAY BUFFER

The 5V9352 is a low-skew, low-jitter, phase-lock loop (PLL) clock driver

targeted for high performance clock tree applications. It uses a PLL to

precisely align, in both frequency and phase. The 5V9352 operates at 2.5V

and 3.3V.

FUNCTIONAL BLOCK DIAGRAM

DESCRIPTION:

The 5V9352 features three banks of individually configurable outputs.

The banks are configured with five, four, and two outputs. The internal

divide circuitry allows for output frequency ratios of 1:1, 2:1, 3:1, and 3:2:1.

The output frequency relationship is controlled by the fSEL frequency

control pins. The fSEL pins, as well as other inputs, are LVCMOS/LVTTL

compatible inputs

Unlike many products containing PLLs, the 5V9352 does not require

external RC networks. The loop filter for the PLL is included on-chip,

minimizing component count, board space, and cost.

Because it is based on PLL circuitry, the 5V9352 requires a stabilization

time to achieve phase lock of the feedback signal to the reference signal.

This stabilization time is required, following power up and application of a

fixed-frequency, fixed-phase signal at REFCLK, as well as following any

changes to the PLL reference or feedback signals. The PLL can be

bypassed for test purposes by setting the

PLL_EN to high.

The 5V9352 is available in Industrial temperature range (-40°C to

+85°C).

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

FEATURES:

Phase-lock loop clock distribution for high performance clock

tree applications

Output enable bank control

External feedback (FBIN) pin is used to synchronize the

outputs to the clock input signal

No external RC network required for PLL loop stability

Operates at 3.3V/2.5V VCC

Spread Spectrum Compatible

Operating frequency up to 200MHz

Compatible with Motorola MPC9352

Available in 32-pin TQFP package

相关PDF资料 |

PDF描述 |

|---|---|

| IDT5V9910A-5SOG | 5V SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO24 |

| IDT5V9910A-5SOGI | 5V SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO24 |

| IDT5V991A-2JRC | PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC32 |

| IDT5V993A-5QGI8 | PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| IDT5V993A-7QI8 | 5V SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT5V9855-003PFI | 制造商:INT_DEV_TECH 功能描述: |

| IDT5V9885ANLGI | 制造商:Integrated Device Technology Inc 功能描述: |

| IDT5V9885BNLGI | 功能描述:IC CLK GEN 3.3V EEPROM 28-VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

| IDT5V9885BNLGI8 | 功能描述:IC CLK GEN 3.3V EEPROM 28-VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

| IDT5V9885BPFGI | 功能描述:IC CLK GEN 3.3V EEPROM 32TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

发布紧急采购,3分钟左右您将得到回复。