- 您现在的位置:买卖IC网 > PDF目录4063 > IDT7006S35PF8 (IDT, Integrated Device Technology Inc)IC SRAM 128KBIT 35NS 64TQFP PDF资料下载

参数资料

| 型号: | IDT7006S35PF8 |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 13/20页 |

| 文件大小: | 0K |

| 描述: | IC SRAM 128KBIT 35NS 64TQFP |

| 标准包装: | 750 |

| 格式 - 存储器: | RAM |

| 存储器类型: | SRAM - 双端口,异步 |

| 存储容量: | 128K (16K x 8) |

| 速度: | 35ns |

| 接口: | 并联 |

| 电源电压: | 4.5 V ~ 5.5 V |

| 工作温度: | 0°C ~ 70°C |

| 封装/外壳: | 64-LQFP |

| 供应商设备封装: | 64-TQFP(14x14) |

| 包装: | 带卷 (TR) |

| 其它名称: | 7006S35PF8 |

�� �

�

�

�IDT7006S/L�

�High-Speed� 16K� x� 8� Dual-Port� Static� RAM�

�Military,� Industrial� and� Commercial� Temperature� Ranges�

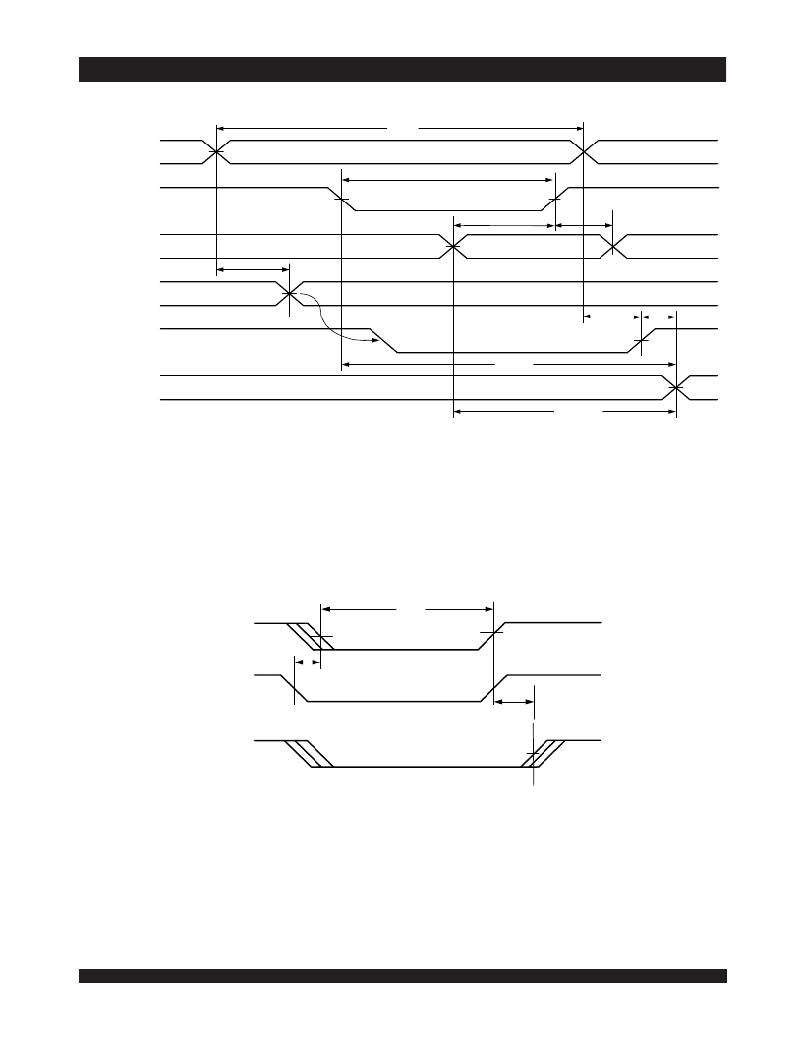

�Timing� Waveform� of� Write� with� Port-to-Port� Read� and� BUSY� (2,5)� (M/� S� =� V� IH� )� (4)�

�t� WC�

�ADDR� "A"�

�MATCH�

�t� WP�

�R/� W� "A"�

�t� APS�

�DATA� IN� "A"�

�(1)�

�t� DW�

�VALID�

�t� DH�

�ADDR� "B"�

�MATCH�

�BUSY� "B"�

�t� WDD�

�DATA� OUT� "B"�

�t� DDD� (3)�

�NOTES:�

�1.� To� ensure� that� the� earlier� of� the� two� ports� wins.� t� APS� is� ignored� for� M/S� =� V� IL� (SLAVE).�

�2.� CE� L� =� CE� R� =� V� IL�

�3.� OE� =� V� IL� for� the� reading� port.�

�4.� If� M/� S� =� V� IL� (slave)� then� BUSY� is� input� (� BUSY� "A"� =� V� IH� )� and� BUSY� "B"� =� "don't� care",� for� this� example.�

�5.� All� timing� is� the� same� for� left� and� right� port.� Port� "A'� may� be� either� left� or� right� port.� Port� "B"� is� the� port� opposite� from� Port� "A".�

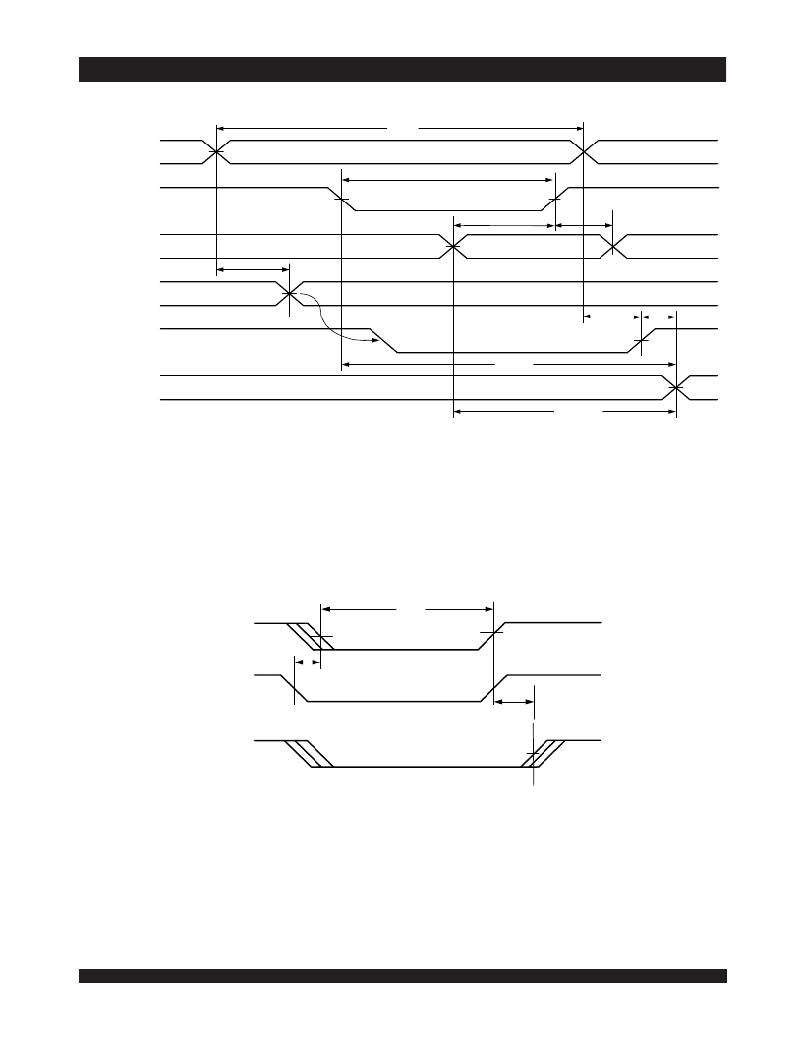

�Timing� Waveform� of� Write� with� BUSY�

�t� WP�

�R/� W� "A"�

�t� WB� (3)�

�t� BDA�

�t� BDD�

�VALID�

�2739� drw� 13�

�BUSY� "B"�

�R/� W� "B"�

�(2)�

�t� WH� (1)�

�2739� drw� 14�

�NOTES:�

�1.� t� WH� must� be� met� for� both� BUSY� input� (slave)� and� output� (master).�

�2.� BUSY� is� asserted� on� Port� "B",� blocking� R/� W� "B"� ,� until� BUSY� "B"� goes� HIGH.�

�3.� t� WB� is� only� for� the� 'Slave'� Version� .�

�13�

�6.42�

�相关PDF资料 |

PDF描述 |

|---|---|

| MPC8358EZQAGDGA | MPU POWERQUICC II PRO 668-PBGA |

| IDT7006S25PF8 | IC SRAM 128KBIT 25NS 64TQFP |

| IDT7006S20PF8 | IC SRAM 128KBIT 20NS 64TQFP |

| IDT71V67803S166PFGI | IC SRAM 9MBIT 166MHZ 100TQFP |

| IDT71V67803S166BQG | IC SRAM 9MBIT 166MHZ 165FBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT7006S35PFB | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:HIGH-SPEED 16K x 8 DUAL-PORT STATIC RAM |

| IDT7006S35XL | 制造商:未知厂家 制造商全称:未知厂家 功能描述:x8 Dual-Port SRAM |

| IDT7006S35XLB | 制造商:未知厂家 制造商全称:未知厂家 功能描述:x8 Dual-Port SRAM |

| IDT7006S45F | 制造商:未知厂家 制造商全称:未知厂家 功能描述:x8 Dual-Port SRAM |

| IDT7006S45FB | 制造商:未知厂家 制造商全称:未知厂家 功能描述:x8 Dual-Port SRAM |

发布紧急采购,3分钟左右您将得到回复。