- 您现在的位置:买卖IC网 > Datasheet目录328 > IDT7052L20G (IDT, Integrated Device Technology Inc)IC SRAM 16KBIT 20NS 108PGA Datasheet资料下载

参数资料

| 型号: | IDT7052L20G |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 8/11页 |

| 文件大小: | 0K |

| 描述: | IC SRAM 16KBIT 20NS 108PGA |

| 标准包装: | 3 |

| 格式 - 存储器: | RAM |

| 存储器类型: | SRAM - 四端口,异步 |

| 存储容量: | 16K (2K x 8) |

| 速度: | 20ns |

| 接口: | 并联 |

| 电源电压: | 4.5 V ~ 5.5 V |

| 工作温度: | 0°C ~ 70°C |

| 封装/外壳: | 108-BSPGA |

| 供应商设备封装: | 108-PGA(30.48x30.48) |

| 包装: | 托盘 |

| 其它名称: | 7052L20G |

�� �

�

�

�IDT7052S/L�

�High-Speed� 2K� x� 8� FourPort?� Static� RAM�

�Military,� Industrial� and� Commercial� Temperature� Ranges�

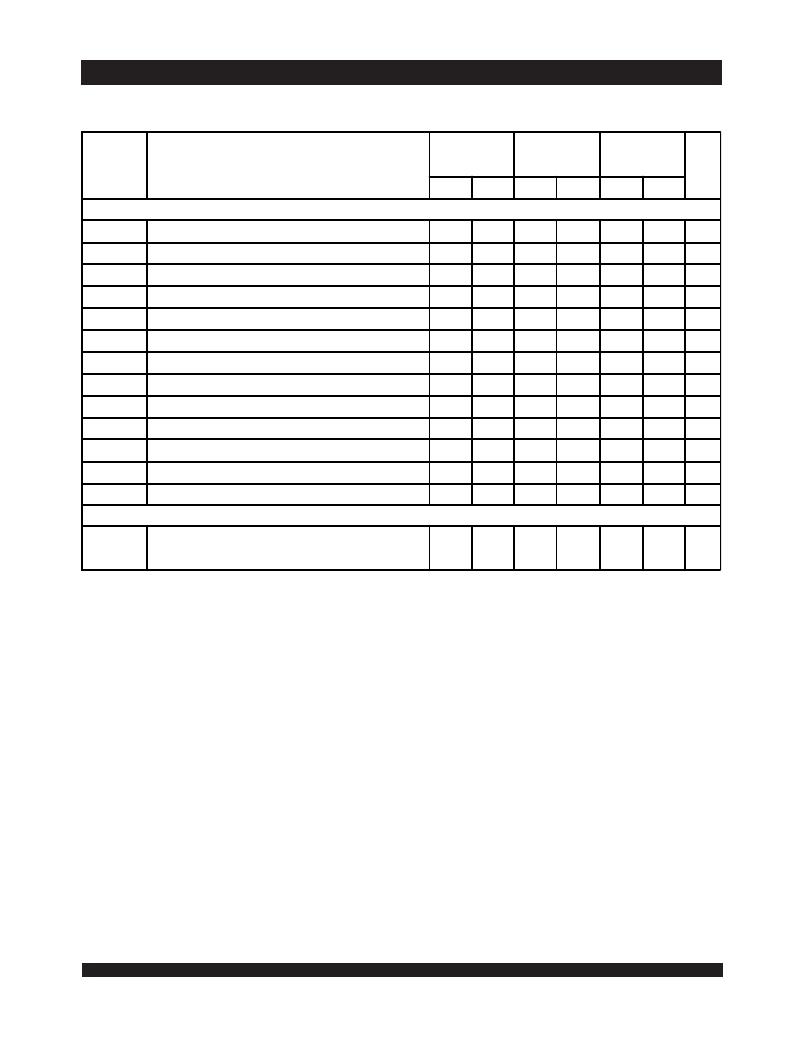

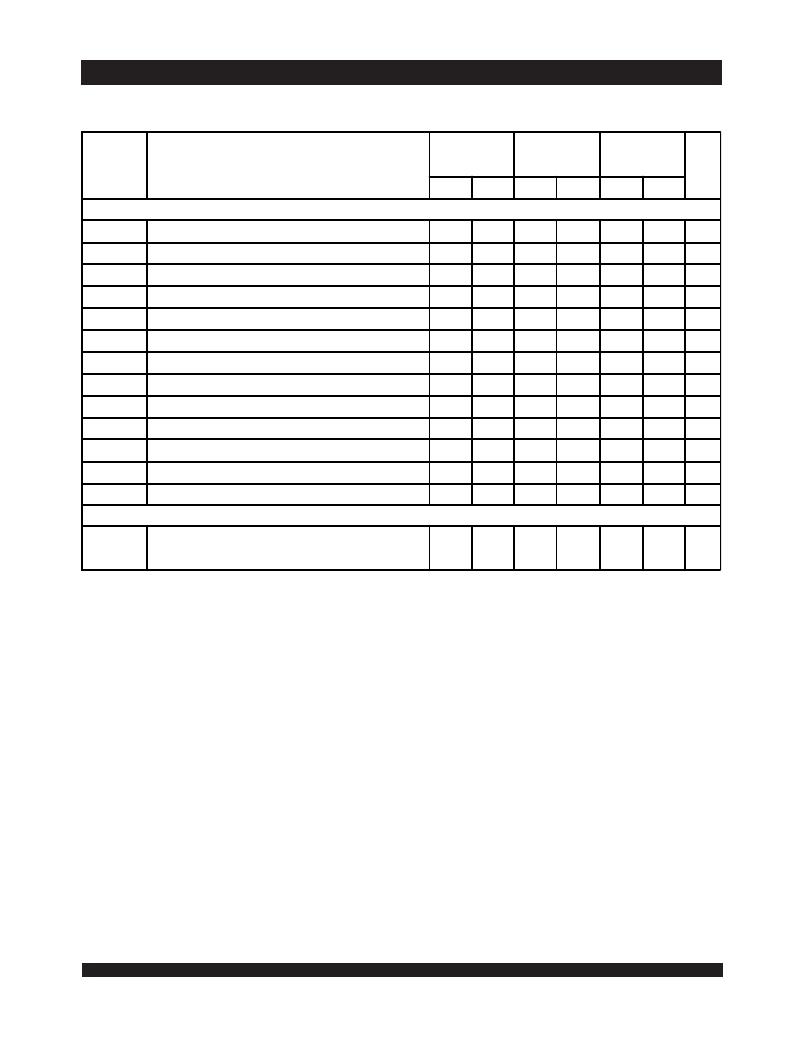

�AC� Electrical� Characteristics� Over� the�

�Operating� Temperature� and� Supply� Voltage� (7)�

�7052X20�

�Com'l� Only�

�7052X25�

�Com'l� &�

�Military�

�7052X35�

�Com'l� &�

�Military�

�Symbol�

�Parameter�

�Min.�

�Max.�

�Min.�

�Max.�

�Min.�

�Max.�

�Unit�

�WRITE� CYCLE�

�Write� Pulse� Width�

�Write� Enable� to� Output� in� High-Z�

�t� WC�

�t� EW�

�t� AW�

�t� AS�

�t� WP�

�t� WR�

�t� DW�

�t� HZ�

�t� DH�

�t� WZ�

�Write� Cycle� Time�

�Chip� Enable� to� End-of-Write� (3)�

�Address� Valid� to� End-of-Write�

�Address� Set-up� Time�

�(3)�

�Write� Recovery� Time�

�Data� Valid� to� End-of-Write�

�Output� High-Z� Time� (1,2)�

�Data� Hold� Time�

�(1,2)�

�20�

�15�

�15�

�0�

�15�

�0�

�15�

�____�

�0�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�15�

�____�

�12�

�25�

�20�

�20�

�0�

�20�

�0�

�15�

�____�

�0�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�15�

�____�

�15�

�35�

�30�

�30�

�0�

�30�

�0�

�20�

�____�

�0�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�15�

�____�

�15�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�t� OW�

�Output� Active� from� End-of-Write�

�(1,2)�

�0�

�____�

�0�

�____�

�0�

�____�

�ns�

�t� WDD�

�t� WDD�

�Write� Pulse� to� Data� Delay� (4)�

�Write� Data� Valid� to� Read� Data� Delay� (4)�

�____�

�____�

�35�

�30�

�____�

�____�

�45�

�35�

�____�

�____�

�55�

�45�

�ns�

�ns�

�BUSY� INPUT� TIMING�

�Write� Hold� After� BUSY�

�t� WB�

�t� WH�

�Write� to� BUSY� (5)�

�(6)�

�0�

�15�

�____�

�____�

�0�

�15�

�____�

�____�

�0�

�20�

�____�

�____�

�ns�

�ns�

�NOTES:�

�2674� tbl� 10�

�1.� Transition� is� measured� 0mV� from� Low� or� High-impedance� voltage� with� the� Output� Test� Load� (Figure� 2).�

�2.� This� parameter� is� guaranteed� by� device� characterization� but� is� not� production� tested.�

�3.� If� OE� =� V� IL� during� a� R/� W� controlled� write� cycle,� the� write� pulse� width� must� be� the� larger� of� t� WP� or� (t� WZ� +� t� DW� )� to� allow� the� I/O� drivers�

�to� turn� off� data� to� be� placed� on� the� bus� for� the� required� t� DW� .� If� OE� =� V� IH� during� an� R/W� controlled� write� cycle,� this� requirement�

�does� not� apply� and� the� write� pulse� can� be� as� short� as� the� specified� t� WP� .� Specified� for� OE� =� V� IH� (refer� to� “Timing� Waveform� of� Write� Cycle”,� Note� 8).�

�4.� Port-to-port� delay� through� RAM� cells� from� writing� port� to� reading� port,� refer� to� “Timing� Waveform� of� Write� with� Port-to-Port� Read”.�

�5.� To� ensure� that� the� write� cycle� is� inhibited� on� port� "A"� during� contention� from� Port� "B".� Port� "A"� may� be� any� of� the� four� ports� and� Port� "B"� is� any� other� port.�

�6.� To� ensure� that� a� write� cycle� is� completed� on� port� "A"� after� contention� from� Port� "B".� Port� "A"� may� be� any� of� the� four� ports� and� Port� "B"� is� any� other� port.�

�7.� 'X'� in� part� number� indicates� power� rating.�

�8�

�6.42�

�相关PDF资料 |

PDF描述 |

|---|---|

| IDT7054L20G | IC SRAM 32KBIT 20NS 108PGA |

| IDT709089L9PF | IC SRAM 512KBIT 9NS 100TQFP |

| IDT709099L9PFI | IC SRAM 1MBIT 9NS 100TQFP |

| IDT709149S10PFI | IC SRAM 36KBIT 10NS 80TQFP |

| IDT70914S12PF | IC SRAM 36KBIT 12NS 80TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT7052L20PF | 功能描述:IC SRAM 16KBIT 20NS 120TQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:1,000 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,同步 存储容量:1.125M(32K x 36) 速度:5ns 接口:并联 电源电压:3.15 V ~ 3.45 V 工作温度:-40°C ~ 85°C 封装/外壳:256-LBGA 供应商设备封装:256-CABGA(17x17) 包装:带卷 (TR) 其它名称:70V3579S5BCI8 |

| IDT7052L20PF8 | 功能描述:IC SRAM 16KBIT 20NS 120TQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:1,000 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,同步 存储容量:1.125M(32K x 36) 速度:5ns 接口:并联 电源电压:3.15 V ~ 3.45 V 工作温度:-40°C ~ 85°C 封装/外壳:256-LBGA 供应商设备封装:256-CABGA(17x17) 包装:带卷 (TR) 其它名称:70V3579S5BCI8 |

| IDT7052L20PFG | 功能描述:IC SRAM 16KBIT 20NS 120TQFP RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:1,000 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,同步 存储容量:1.125M(32K x 36) 速度:5ns 接口:并联 电源电压:3.15 V ~ 3.45 V 工作温度:-40°C ~ 85°C 封装/外壳:256-LBGA 供应商设备封装:256-CABGA(17x17) 包装:带卷 (TR) 其它名称:70V3579S5BCI8 |

| IDT7052L20PFG8 | 制造商:Integrated Device Technology Inc 功能描述:IC SRAM 16KBIT 20NS 120TQFP |

| IDT7052L20PQF | 功能描述:IC SRAM 16KBIT 20NS 132QFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:1,000 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,同步 存储容量:1.125M(32K x 36) 速度:5ns 接口:并联 电源电压:3.15 V ~ 3.45 V 工作温度:-40°C ~ 85°C 封装/外壳:256-LBGA 供应商设备封装:256-CABGA(17x17) 包装:带卷 (TR) 其它名称:70V3579S5BCI8 |

发布紧急采购,3分钟左右您将得到回复。