- 您现在的位置:买卖IC网 > Datasheet目录328 > IDT70914S12PF (IDT, Integrated Device Technology Inc)IC SRAM 36KBIT 12NS 80TQFP Datasheet资料下载

参数资料

| 型号: | IDT70914S12PF |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 10/11页 |

| 文件大小: | 0K |

| 描述: | IC SRAM 36KBIT 12NS 80TQFP |

| 标准包装: | 45 |

| 格式 - 存储器: | RAM |

| 存储器类型: | SRAM - 双端口,同步 |

| 存储容量: | 36K(4K x 9) |

| 速度: | 12ns |

| 接口: | 并联 |

| 电源电压: | 4.5 V ~ 5.5 V |

| 工作温度: | 0°C ~ 70°C |

| 封装/外壳: | 80-LQFP |

| 供应商设备封装: | 80-TQFP(14x14) |

| 包装: | 托盘 |

| 其它名称: | 70914S12PF |

�� �

�

�

�IDT70914S�

�High-Speed� 36K� (4K� x� 9)� Synchronous� Dual-Port� Static� RAM�

�Functional� Description�

�The� IDT70914� provides� a� true� synchronous� Dual-Port� Static� RAM�

�interface.� Registered� inputs� provide� very� short� set-up� and� hold� times� on�

�address,� data,� and� all� critical� control� inputs.� All� internal� registers� are� clocked�

�on� the� rising� edge� of� the� clock� signal.� An� asynchronous� output� enable� is�

�provided� to� ease� asynchronous� bus� interfacing.�

�The� internal� write� pulse� width� is� dependent� on� the� LOW� to� HIGH�

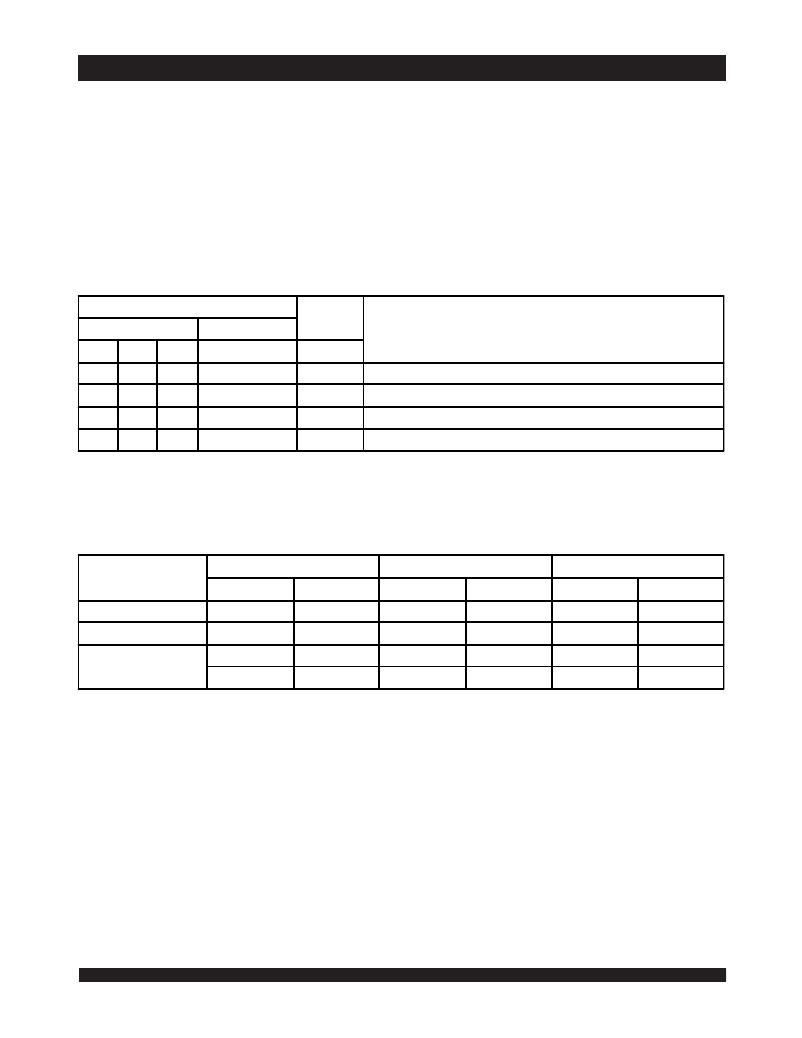

�Truth� Table� I:� Read/Write� Control� (1)�

�Military,� Industrial� and� Commercial� Temperature� Ranges�

�transitions� of� the� clock� signal� allowing� the� shortest� possible� realized� cycle�

�times.� Clock� enable� inputs� are� provided� to� stall� the� operation� of� the� address�

�and� data� input� registers� without� introducing� clock� skew� for� very� fast�

�interleaved� memory� applications.�

�A� HIGH� on� the� CE� input� for� one� clock� cycle� will� power� down� the�

�internal� circuitry� to� reduce� static� power� consumption.�

�Synchronous�

�(3)�

�Inputs�

�Asynchronous�

�Outputs�

�CLK�

�↑�

�↑�

�↑�

�↑�

�CE�

�H�

�L�

�L�

�X�

�R/� W�

�X�

�L�

�H�

�X�

�OE�

�X�

�X�

�L�

�H�

�I/O� 0-8�

�High-Z�

�DATA� IN�

�DATA� OUT�

�High-Z�

�Mode�

�Deselected,� Power-Down�

�Selected� and� Write� Enabled�

�Read� Selected� and� Data� Output� Enable� Read�

�Outputs� Disabled�

�3490� tbl� 09�

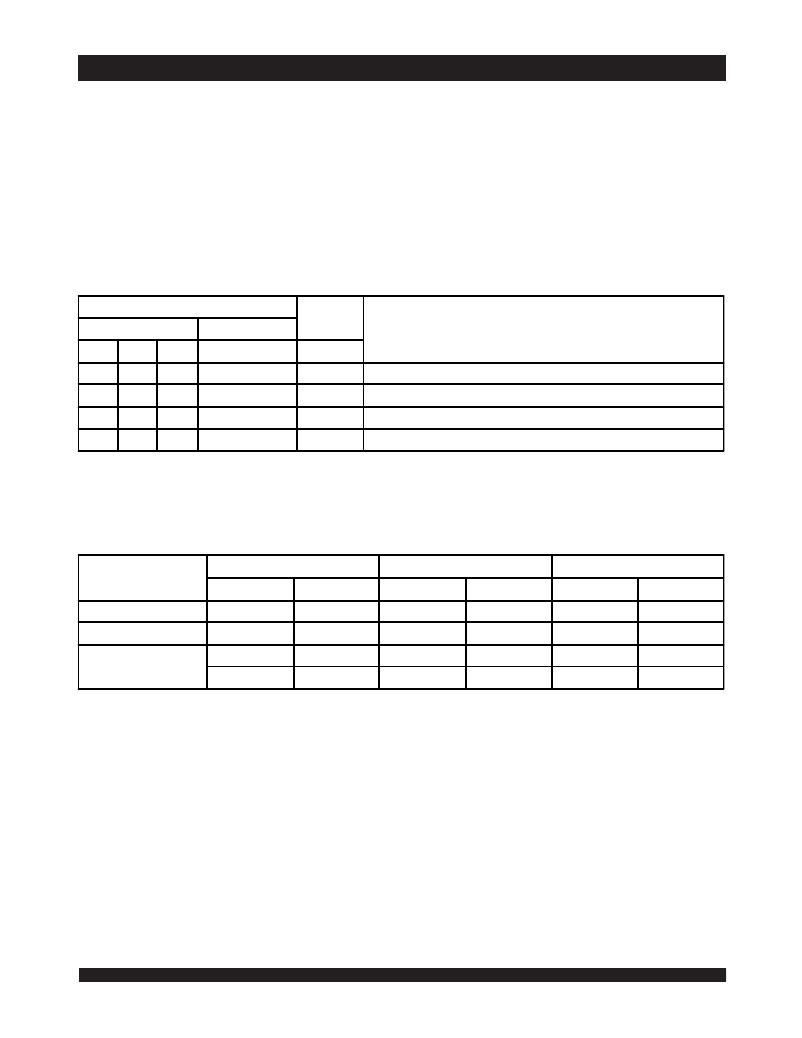

�Truth� Table� II:� Clock� Enable� Function� Table� (1)�

�Inputs�

�Register� Inputs�

�Register� Outputs� (4)�

�Mode�

�Load� "1"�

�Load� "0"�

�Hold� (do� nothing)�

�CLK� (3)�

�↑�

�↑�

�↑�

�X�

�CLKEN� (2)�

�L�

�L�

�H�

�H�

�ADDR�

�H�

�L�

�X�

�X�

�DATAIN�

�H�

�L�

�X�

�X�

�ADDR�

�H�

�L�

�NC�

�NC�

�DATAOUT�

�H�

�L�

�NC�

�NC�

�NOTES:�

�3490� tbl� 10�

�1.� 'H'� =� HIGH� voltage� level� steady� state,� 'h'� =� HIGH� voltage� level� one� set-up� time� prior� to� the� LOW-to-HIGH� clock� transition,� 'L'� =� LOW� voltage� level� steady� state� 'l'� =� LOW�

�voltage� level� one� set-up� time� prior� to� the� LOW-to-HIGH� clock� transition,� 'X'� =� Don't� care,� 'NC'� =� No� change�

�2.� CLKEN� =� V� IL� must� be� clocked� in� during� Power-Up.�

�3.� Control� signals� are� initialted� and� terminated� on� the� rising� edge� of� the� CLK,� depending� on� their� input� level.� When� R/� W� and� CE� are� LOW,� a� write� cycle� is� initiated� on�

�the� LOW-to-HIGH� transition� of� the� CLK.� Termination� of� a� write� cycle� is� done� on� the� next� LOW-to-HIGH� transistion� of� the� CLK.�

�4.� The� register� outputs� are� internal� signals� from� the� register� inputs� being� clocked� in� or� disabled� by� CLKEN� .�

�10�

�6.42�

�相关PDF资料 |

PDF描述 |

|---|---|

| IDT709169L7BFI | IC SRAM 144KBIT 7NS 100FBGA |

| IDT709279L9PFG | IC SRAM 512KBIT 9NS 100TQFP |

| IDT709289L9PFI | IC SRAM 1MBIT 9NS 100TQFP |

| IDT709359L7BFI | IC SRAM 144KBIT 7NS 100FBGA |

| IDT709379L7PFG | IC SRAM 576KBIT 7NS 100TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT70914S12PF8 | 功能描述:IC SRAM 36KBIT 12NS 80TQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:45 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,异步 存储容量:128K(8K x 16) 速度:15ns 接口:并联 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:70V25S15PF |

| IDT70914S15J | 功能描述:IC SRAM 36KBIT 15NS 68PLCC RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:1,000 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,同步 存储容量:1.125M(32K x 36) 速度:5ns 接口:并联 电源电压:3.15 V ~ 3.45 V 工作温度:-40°C ~ 85°C 封装/外壳:256-LBGA 供应商设备封装:256-CABGA(17x17) 包装:带卷 (TR) 其它名称:70V3579S5BCI8 |

| IDT70914S15J8 | 功能描述:IC SRAM 36KBIT 15NS 68PLCC RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:45 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,异步 存储容量:128K(8K x 16) 速度:15ns 接口:并联 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:70V25S15PF |

| IDT70914S15JI | 功能描述:IC SRAM 36KBIT 15NS 68PLCC RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:1,000 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,同步 存储容量:1.125M(32K x 36) 速度:5ns 接口:并联 电源电压:3.15 V ~ 3.45 V 工作温度:-40°C ~ 85°C 封装/外壳:256-LBGA 供应商设备封装:256-CABGA(17x17) 包装:带卷 (TR) 其它名称:70V3579S5BCI8 |

| IDT70914S15JI8 | 功能描述:IC SRAM 36KBIT 15NS 68PLCC RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:45 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,异步 存储容量:128K(8K x 16) 速度:15ns 接口:并联 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:70V25S15PF |

发布紧急采购,3分钟左右您将得到回复。