- 您现在的位置:买卖IC网 > PDF目录4010 > IDT70V37L20PFGI8 (IDT, Integrated Device Technology Inc)IC SRAM 576KBIT 20NS 100TQFP PDF资料下载

参数资料

| 型号: | IDT70V37L20PFGI8 |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 14/17页 |

| 文件大小: | 0K |

| 描述: | IC SRAM 576KBIT 20NS 100TQFP |

| 标准包装: | 750 |

| 格式 - 存储器: | RAM |

| 存储器类型: | SRAM - 双端口,异步 |

| 存储容量: | 576K(32K x 18) |

| 速度: | 20ns |

| 接口: | 并联 |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 100-LQFP |

| 供应商设备封装: | 100-TQFP(14x14) |

| 包装: | 带卷 (TR) |

| 其它名称: | 70V37L20PFGI8 |

�� �

�

�

�IDT70V37L�

�High-Speed� 3.3V� 32K� x� 18� Dual-Port� Static� RAM�

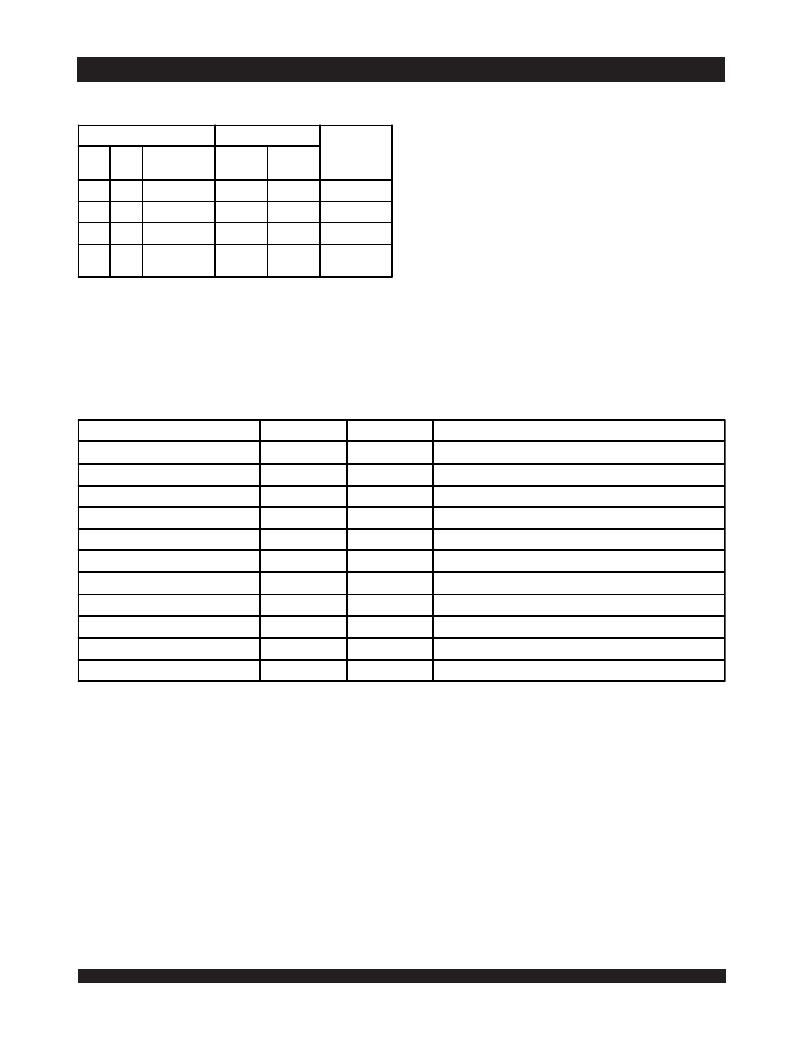

�Truth� Table� V� —�

�Address� BUSY� Arbitration� (4)�

�Industrial� and� Commercial� Temperature� Ranges�

�Inputs�

�Outputs�

�CE� L�

�X�

�H�

�X�

�L�

�CE� R�

�X�

�X�

�H�

�L�

�A� OL� -A� 14L�

�A� OR� -A� 14R�

�NO� MATCH�

�MATCH�

�MATCH�

�MATCH�

�BUSY� L� (1)�

�H�

�H�

�H�

�(2)�

�BUSY� R� (1)�

�H�

�H�

�H�

�(2)�

�Function�

�Normal�

�Normal�

�Normal�

�Write� Inhibit� (3)�

�NOTES:�

�4851� tbl� 17�

�1.� Pins� BUSY� L� and� BUSY� R� are� both� outputs� when� the� part� is� configured� as� a� master.� Both� are� inputs� when� configured� as� a� slave.� BUSY� outputs� on� the� IDT70V37� are�

�push-pull,� not� open� drain� outputs.� On� slaves� the� BUSY� input� internally� inhibits� writes.�

�2.� "L"� if� the� inputs� to� the� opposite� port� were� stable� prior� to� the� address� and� enable� inputs� of� this� port.� "H"� if� the� inputs� to� the� opposite� port� became� stable� after� the� address�

�and� enable� inputs� of� this� port.� If� t� APS� is� not� met,� either� BUSY� L� or� BUSY� R� =� LOW� will� result.� BUSY� L� and� BUSY� R� outputs� can� not� be� LOW� simultaneously.�

�3.� Writes� to� the� left� port� are� internally� ignored� when� BUSY� L� outputs� are� driving� LOW� regardless� of� actual� logic� level� on� the� pin.� Writes� to� the� right� port� are� internally� ignored�

�when� BUSY� R� outputs� are� driving� LOW� regardless� of� actual� logic� level� on� the� pin.�

�4.� Refer� to� Truth� Table� I� -� Chip� Enable.�

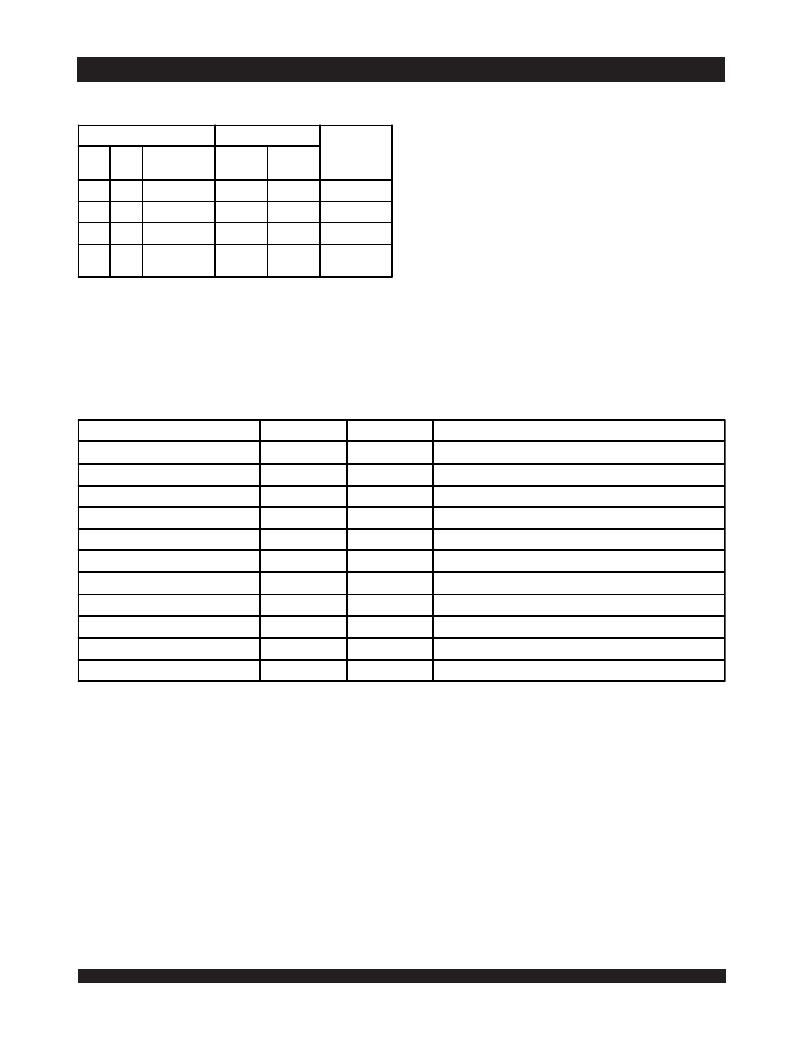

�Truth� Table� VI� —� Example� of� Semaphore� Procurement� Sequence� (1,2,3)�

�Functions�

�No� Action�

�Left� Port� Writes� "0"� to� Semaphore�

�Right� Port� Writes� "0"� to� Semaphore�

�Left� Port� Writes� "1"� to� Semaphore�

�Left� Port� Writes� "0"� to� Semaphore�

�Right� Port� Writes� "1"� to� Semaphore�

�Left� Port� Writes� "1"� to� Semaphore�

�Right� Port� Writes� "0"� to� Semaphore�

�Right� Port� Writes� "1"� to� Semaphore�

�Left� Port� Writes� "0"� to� Semaphore�

�Left� Port� Writes� "1"� to� Semaphore�

�NOTES:�

�D� 0� -� D� 17� Left�

�1�

�0�

�0�

�1�

�1�

�0�

�1�

�1�

�1�

�0�

�1�

�D� 0� -� D� 17� Right�

�1�

�1�

�1�

�0�

�0�

�1�

�1�

�0�

�1�

�1�

�1�

�Status�

�Semaphore� free�

�Left� port� has� semaphore� token�

�No� change.� Right� side� has� no� write� access� to� semaphore�

�Right� port� obtains� semaphore� token�

�No� change.� Left� port� has� no� write� access� to� semaphore�

�Left� port� obtains� semaphore� token�

�Semaphore� free�

�Right� port� has� semaphore� token�

�Semaphore� free�

�Left� port� has� semaphore� token�

�Semaphore� free�

�4851� tbl� 18�

�1.� This� table� denotes� a� sequence� of� events� for� only� one� of� the� eight� semaphores� on� the� IDT70V37.�

�2.� There� are� eight� semaphore� flags� written� to� via� I/O� 0� and� read� from� all� I/O's� (I/O� 0� -I/O� 17� ).� These� eight� semaphores� are� addressed� by� A� 0� -� A� 2� .�

�3.� CE� =� V� IH� ,� SEM� =� V� IL� to� access� the� semaphores.� Refer� to� the� Truth� Table� III� -� Semaphore� Read/Write� Control.�

�Functional� Description�

�The� IDT70V37� provides� two� ports� with� separate� control,� address� and�

�I/O� pins� that� permit� independent� access� for� reads� or� writes� to� any� location�

�in� memory.� The� IDT70V37� has� an� automatic� power� down� feature�

�controlled� by� CE� .� The� CE� 0� and� CE� 1� control� the� on-chip� power� down�

�circuitry� that� permits� the� respective� port� to� go� into� a� standby� mode� when�

�not� selected� (� CE� =� HIGH).� When� a� port� is� enabled,� access� to� the� entire�

�memory� array� is� permitted.�

�Interrupts�

�If� the� user� chooses� the� interrupt� function,� a� memory� location� (mail� box�

�(HEX),� where� a� write� is� defined� as� CE� R� =� R/� W� R� =� V� IL� per� the� Truth� Table.�

�The� left� port� clears� the� interrupt� through� access� of� address� location� 7FFE�

�when� CE� L� =� OE� L� =� V� IL� ,� R/� W� is� a� "don't� care".� Likewise,� the� right� port�

�interrupt� flag� (� INT� R� )� is� asserted� when� the� left� port� writes� to� memory� location�

�7FFF� (HEX)� and� to� clear� the� interrupt� flag� (� INT� R� ),� the� right� port� must� read�

�the� memory� location� 7FFF.� The� message� (18� bits)� at� 7FFE� or� 7FFF� is�

�user-defined� since� it� is� an� addressable� SRAM� location.� If� the� interrupt�

�function� is� not� used,� address� locations� 7FFE� and� 7FFF� are� not� used� as�

�mail� boxes,� but� as� part� of� the� random� access� memory.� Refer� to� Truth� Table�

�IV� for� the� interrupt� operation.�

�or� message� center)� is� assigned� to� each� port.� The� left� port� interrupt� flag�

�(� INT� L� )� is� asserted� when� the� right� port� writes� to� memory� location� 7FFE�

�14�

�6.42�

�相关PDF资料 |

PDF描述 |

|---|---|

| IDT70V37L15PFG8 | IC SRAM 576KBIT 15NS 100TQFP |

| IDT70V37L15PF8 | IC SRAM 576KBIT 15NS 100TQFP |

| IDT70V27S15PF8 | IC SRAM 512KBIT 15NS 100TQFP |

| IDT70V18L20PFI8 | IC SRAM 576KBIT 20NS 100TQFP |

| AMC30DTEI | CONN EDGECARD 60POS .100 EYELET |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT70V37L20PFI | 功能描述:IC SRAM 576KBIT 20NS 100TQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:1,000 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,同步 存储容量:1.125M(32K x 36) 速度:5ns 接口:并联 电源电压:3.15 V ~ 3.45 V 工作温度:-40°C ~ 85°C 封装/外壳:256-LBGA 供应商设备封装:256-CABGA(17x17) 包装:带卷 (TR) 其它名称:70V3579S5BCI8 |

| IDT70V37L20PFI8 | 功能描述:IC SRAM 576KBIT 20NS 100TQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:1,000 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,同步 存储容量:1.125M(32K x 36) 速度:5ns 接口:并联 电源电压:3.15 V ~ 3.45 V 工作温度:-40°C ~ 85°C 封装/外壳:256-LBGA 供应商设备封装:256-CABGA(17x17) 包装:带卷 (TR) 其它名称:70V3579S5BCI8 |

| IDT70V38L15PF | 功能描述:IC SRAM 1.125MBIT 15NS 100TQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

| IDT70V38L15PF8 | 功能描述:IC SRAM 1.125MBIT 15NS 100TQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:1,000 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,同步 存储容量:1.125M(32K x 36) 速度:5ns 接口:并联 电源电压:3.15 V ~ 3.45 V 工作温度:-40°C ~ 85°C 封装/外壳:256-LBGA 供应商设备封装:256-CABGA(17x17) 包装:带卷 (TR) 其它名称:70V3579S5BCI8 |

| IDT70V38L15PFG | 功能描述:IC SRAM 1.125MBIT 15NS 100TQFP RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。