- 您现在的位置:买卖IC网 > PDF目录377311 > IDT7133LA45PFB (INTEGRATED DEVICE TECHNOLOGY INC) HIGH-SPEED 2K x 16 CMOS DUAL-PORT STATIC RAMS PDF资料下载

参数资料

| 型号: | IDT7133LA45PFB |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | DRAM |

| 英文描述: | HIGH-SPEED 2K x 16 CMOS DUAL-PORT STATIC RAMS |

| 中文描述: | 2K X 16 DUAL-PORT SRAM, 45 ns, PQFP100 |

| 封装: | TQFP-100 |

| 文件页数: | 15/16页 |

| 文件大小: | 140K |

| 代理商: | IDT7133LA45PFB |

6.42

IDT7133SA/LA, IDT7143SA/LA

High-Speed 2K x 16 Dual-Port RAM Military, Industrial and Commercial Temperature Ranges

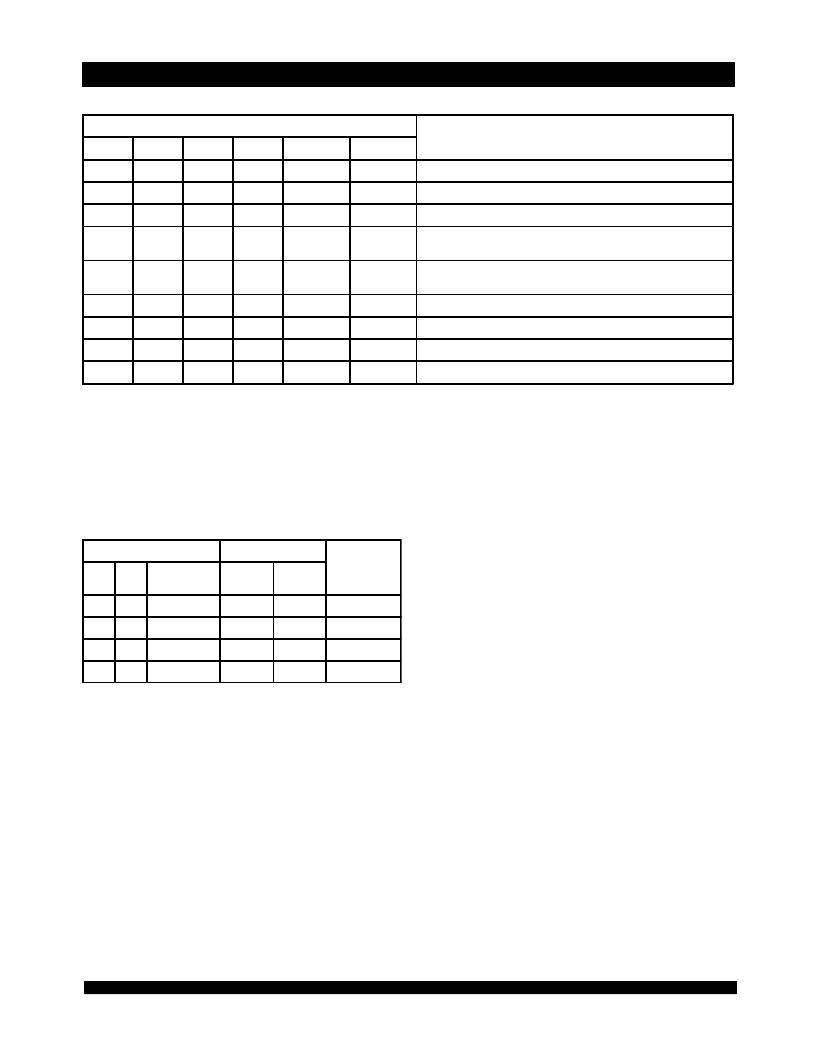

$*$4@A;,-=8

B!

$*$4@@C%--

%4

BUSY

NOTES:

1.

Pins

BUSY

L

and

BUSY

R

are both outputs on the IDT7133 (MASTER). Both are

inputs on the IDT7143 (SLAVE). On Slaves the

BUSY

input internally inhibits

writes.

"L" if the inputs to the opposite port were stable prior to the address and enable

inputs of this port.

“

H

”

if the inputs to the opposite port became stable after the

address and enable inputs of this port. If t

APS

is not met, either

BUSY

L

or

BUSY

R

= V

IL

will result

BUSY

L

and

BUSY

R

outputs can not be LOW simultaneously.

Writes to the left port are internally ignored when

BUSY

L

outputs are driving LOW

regardless of actual logic level on the pin. Writes to the right port are internally

ignored when

BUSY

R

outputs are driving LOW regardless of actual logic level on

the pin.

2.

3.

NOTES:

1.

2.

3.

4.

A

0L

- A

10L

≠

A

0R

- A

10R

If

BUSY

= LOW, data is not written.

If

BUSY

= LOW, data may not be valid, see t

WDD

and t

DDD

timng.

"H" = HIGH, "L" = LOW, "X" = Don

’

t Care, "Z" = High-Impedance, "LB" = Lower Byte, "UB" = Upper Byte

LEFT OR RIGHT PORT

(1)

Function

R/

W

LB

R/

W

UB

CE

OE

I/O

0-7

I/O

8-15

X

X

H

X

Z

Z

Port Disabled and in Power Down Mode, I

SB2

, I

SB4

X

X

H

X

Z

Z

CE

R

= CE

L

= V

IH

, Power Down Mode, I

SB1

or I

SB3

L

L

L

X

DATA

IN

DATA

IN

Data on Lower Byte and Upper Byte Written into Memory

(2)

L

H

L

L

DATA

IN

DATA

OUT

Data on Lower Byte Written into Memory

(2)

, Data in Memory Output on

Upper Byte

(3)

H

L

L

L

DATA

OUT

DATA

IN

Data in Memory Output on Lower Byte

(3)

, Data on Upper Byte Written into

Memory

(2)

L

H

L

H

DATA

IN

Z

Data on Lower Byte Written into Memory

(2)

H

L

L

H

Z

DATA

IN

Data on Upper Byte Written into Memory

(2)

H

H

L

L

DATA

OUT

DATA

OUT

Data in Memory Output on Lower Byte and Upper Byte

H

H

L

H

Z

Z

High Impedance Outputs

2746 tbl 13

Inputs

Outputs

Function

CE

L

CE

R

A

0L

-A

10L

A

0R

-A

10R

BUSY

L

(1)

BUSY

R

(1)

X

X

NO MATCH

H

H

Normal

H

X

MATCH

H

H

Normal

X

H

MATCH

H

H

Normal

L

L

MATCH

(2)

(2)

Write Inhibit

(3)

2746 tbl 14

相关PDF资料 |

PDF描述 |

|---|---|

| IDT7143LA45PFB | HIGH-SPEED 2K x 16 CMOS DUAL-PORT STATIC RAMS |

| IDT7133LA45PFI | HIGH-SPEED 2K x 16 CMOS DUAL-PORT STATIC RAMS |

| IDT7143LA45PFI | HIGH-SPEED 2K x 16 CMOS DUAL-PORT STATIC RAMS |

| IDT7133SA45PFI | HIGH-SPEED 2K x 16 CMOS DUAL-PORT STATIC RAMS |

| IDT7143SA45PFI | HIGH-SPEED 2K x 16 CMOS DUAL-PORT STATIC RAMS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT7133LA55FB | 制造商:Integrated Device Technology Inc 功能描述:IC SRAM 32KBIT 55NS 68FPACK |

| IDT7133LA55G | 功能描述:IC SRAM 32KBIT 55NS 68PGA RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

| IDT7133LA55GB | 制造商:Integrated Device Technology Inc 功能描述:IC SRAM 32KBIT 55NS 68PGA |

| IDT7133LA55J | 功能描述:IC SRAM 32KBIT 55NS 68PLCC RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:72 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 同步 存储容量:9M(256K x 36) 速度:75ns 接口:并联 电源电压:3.135 V ~ 3.465 V 工作温度:-40°C ~ 85°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:71V67703S75PFGI |

| IDT7133LA55J8 | 功能描述:IC SRAM 32KBIT 55NS 68PLCC RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:72 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 同步 存储容量:9M(256K x 36) 速度:75ns 接口:并联 电源电压:3.135 V ~ 3.465 V 工作温度:-40°C ~ 85°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:71V67703S75PFGI |

发布紧急采购,3分钟左右您将得到回复。