- 您现在的位置:买卖IC网 > PDF目录4105 > IDT71342LA20JG8 (IDT, Integrated Device Technology Inc)IC SRAM 32KBIT 20NS 52PLCC PDF资料下载

参数资料

| 型号: | IDT71342LA20JG8 |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 12/14页 |

| 文件大小: | 0K |

| 描述: | IC SRAM 32KBIT 20NS 52PLCC |

| 标准包装: | 400 |

| 格式 - 存储器: | RAM |

| 存储器类型: | SRAM - 双端口,异步 |

| 存储容量: | 32K (4K x 8) |

| 速度: | 20ns |

| 接口: | 并联 |

| 电源电压: | 4.5 V ~ 5.5 V |

| 工作温度: | 0°C ~ 70°C |

| 封装/外壳: | 52-LCC(J 形引线) |

| 供应商设备封装: | 52-PLCC(19x19) |

| 包装: | 带卷 (TR) |

| 其它名称: | 71342LA20JG8 |

�� �

�

�

�IDT71342SA/LA�

�High-Speed� 4K� x� 8� Dual-Port� Static� RAM� with� Semaphore�

�request� latches� feed� into� a� semaphore� flag.� Whichever� latch� is� first� to�

�present� a� zero� to� the� semaphore� flag� will� force� its� side� of� the�

�semaphore� flag� LOW� and� the� other� side� HIGH.� This� condition� will�

�continue� until� a� one� is� written� to� the� same� semaphore� request� latch.�

�Should� the� other� side’s� semaphore� request� latch� have� been� written� to�

�a� zero� in� the� meantime,� the� semaphore� flag� will� now� stay� LOW� until� its�

�semaphore� request� latch� is� written� to� a� one.� From� this� it� is� easy� to�

�understand� that,� if� a� semaphore� is� requested� and� the� processor� which�

�requested� it� no� longer� needs� the� resource,� the� entire� system� can� hang� up�

�until� a� one� is� written� into� that� semaphore� request� latch.�

�The� critical� case� of� semaphore� timing� is� when� both� sides� request�

�a� single� token� by� attempting� to� write� a� zero� into� it� at� the� same� time.� The�

�semaphore� logic� is� specially� designed� to� resolve� this� problem.� If�

�simultaneous� requests� are� made,� the� logic� guarantees� that� only� one�

�Industrial� and� Commercial� Temperature� Ranges�

�side� receives� the� token.� If� one� side� is� earlier� than� the� other� in� making� the�

�request,� the� first� side� to� make� the� request� will� receive� the� token.� If� both�

�requests� arrive� at� the� same� time,� the� assignment� will� be� arbitrarily� made�

�to� one� port� or� the� other.�

�One� caution� that� should� be� noted� when� using� semaphores� is� that�

�semaphores� alone� do� not� guarantee� that� access� to�

�a� resource� is� secure.� As� with� any� powerful� programming� technique,� if�

�semaphores� are� misused� or� misinterpreted,� a� software� error� can�

�easily� happen.� Code� integrity� is� of� the� utmost� importance� when�

�semaphores� are� used� instead� of� slower,� more� restrictive� hardware�

�intensive� schemes.�

�Initialization� of� the� semaphores� is� not� automatic� and� must� be�

�handled� via� the� initialization� program� at� power� up.� Since� any� semaphore�

�request� flag� which� contains� a� zero� must� be� reset� to� a� one,� all�

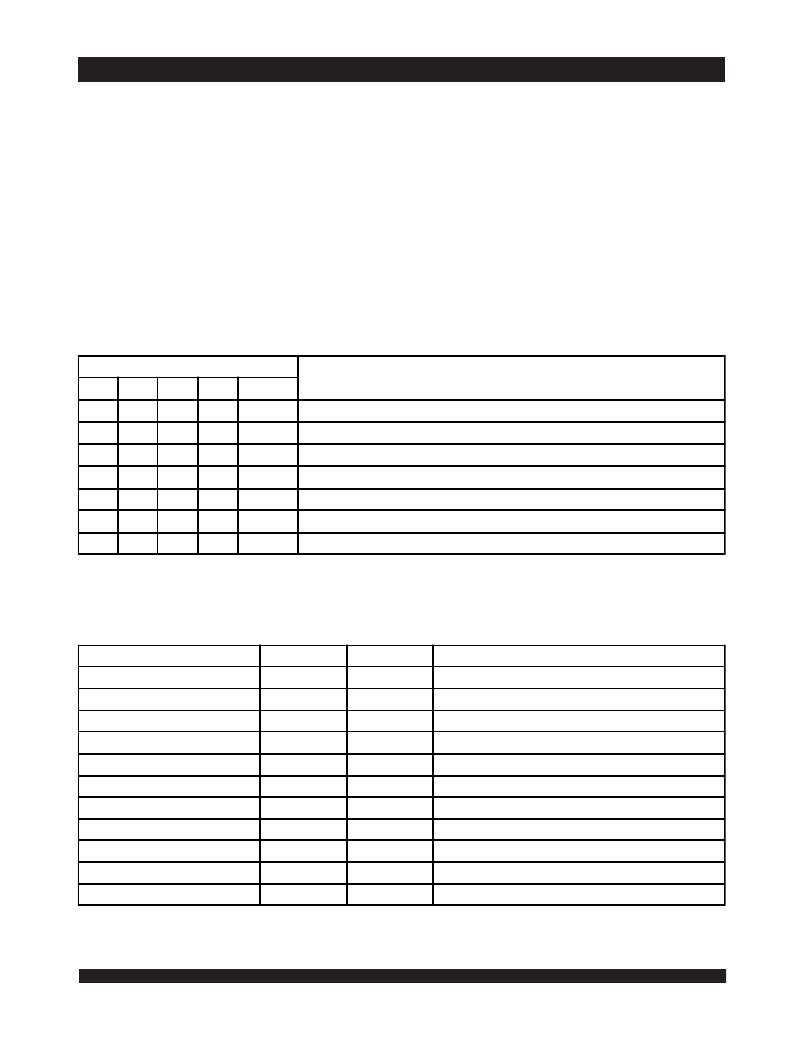

�Truth� Table� I� —� Non-Contention� Read/Write� Control� (2)�

�Left� or� Right� Port� (1)�

�R/� W�

�X�

�H�

�X�

�↑�

�H�

�L�

�X�

�CE�

�H�

�H�

�X�

�H�

�L�

�L�

�L�

�SEM�

�H�

�L�

�X�

�L�

�H�

�H�

�L�

�OE�

�X�

�L�

�H�

�X�

�L�

�X�

�X�

�D� 0-7�

�Z�

�DATA� OUT�

�Z�

�DATA� IN�

�DATA� OUT�

�DATA� IN�

�____�

�Port� Disabled� and� in� Power� Down� Mode�

�Data� in� Semaphore� Flag� Output� on� Port�

�Output� Disabled�

�Port� Data� Bit� D� 0� Written� Into� Semaphore� Flag�

�Data� in� Memory� Output� on� Port�

�Data� on� Port� Written� Into� Memory�

�Not� Allowed�

�Function�

�NOTE:�

�1.� A� OL� -� A� 11L� ≠� A� 0R� -� A� 11R.�

�2.� "H"� =� V� IH� ,� "L"� =� V� IL� ,� "X"� =� Don’t� Care,� "Z"� =� High-Impedance.�

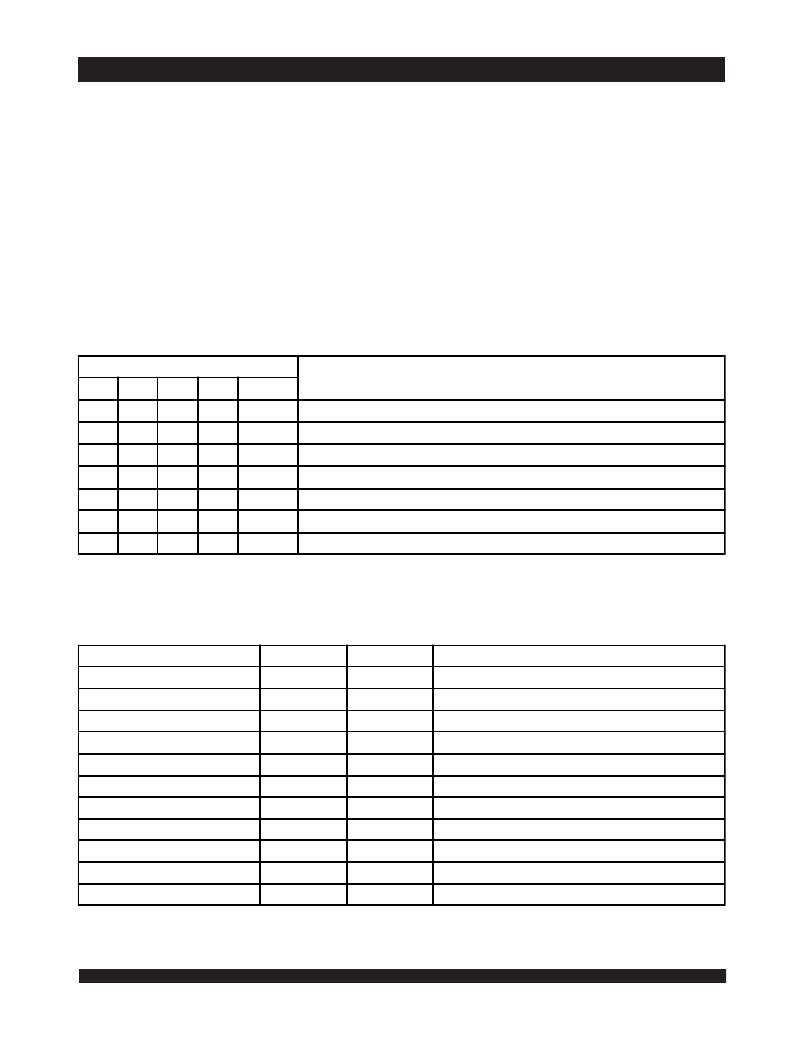

�Truth� Table� II� —� Example� Semaphore� Procurement� Sequence� (1,2,3)�

�2721� tbl� 11�

�Functions�

�No� Action�

�Left� Port� Writes� "0"� to� Semaphore�

�Right� Port� Writes� "0"� to� Semaphore�

�Left� Port� Writes� "1"� to� Semaphore�

�Left� Port� Writes� "0"� to� Semaphore�

�Right� Port� Writes� "1"� to� Semaphore�

�Left� Port� Writes� "1"� to� Semaphore�

�Right� Port� Writes� "0"� to� Semaphore�

�Right� Port� Writes� "1"� to� Semaphore�

�Left� Port� Writes� "0"� to� Semaphore�

�Left� Port� Writes� "1"� to� Semaphore�

�NOTE:�

�D� 0� -� D� 15� Left�

�1�

�0�

�0�

�1�

�1�

�0�

�1�

�1�

�1�

�0�

�1�

�D� 0� -� D� 15� Right�

�1�

�1�

�1�

�0�

�0�

�1�

�1�

�0�

�1�

�1�

�1�

�Status�

�Semaphore� free�

�Left� port� has� semaphore� token�

�No� change.� Right� side� has� no� write� access� to� semaphore�

�Right� port� obtains� semaphore� token�

�No� change.� Left� port� has� no� write� access� to� semaphore�

�Left� port� obtains� semaphore� token�

�Semaphore� free�

�Right� port� has� semaphore� token�

�Semaphore� free�

�Left� port� has� semaphore� token�

�Semaphore� free�

�2721� tbl� 12�

�1.� This� table� denotes� a� sequence� of� events� for� only� one� of� the� eight� semaphores� on� the� IDT71342.�

�2.� There� are� eight� semaphore� flags� written� to� via� I/O� 0� and� read� from� all� I/O's.� These� eight� semaphores� are� addressed� by� A� 0� -A� 2� .�

�3.� CE� =� VIH,� SEM� =� VIL� to� access� the� semaphores.� Refer� to� the� semaphore� Read/Write� Control� Truth� Table.�

�12�

�6.42�

�相关PDF资料 |

PDF描述 |

|---|---|

| MPC8260AZUMHBB | IC MPU POWERQUICC II 480-TBGA |

| IDT71342LA20J8 | IC SRAM 32KBIT 20NS 52PLCC |

| IDT71V321L25TFI8 | IC SRAM 16KBIT 25NS 64STQFP |

| MPC8255ACVVMHBB | IC MPU POWERQUICC II 480-TBGA |

| IDT71V67903S85BG8 | IC SRAM 9MBIT 85NS 119BGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT71342LA20PF | 功能描述:IC SRAM 32KBIT 20NS 64TQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:72 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 同步 存储容量:9M(256K x 36) 速度:75ns 接口:并联 电源电压:3.135 V ~ 3.465 V 工作温度:-40°C ~ 85°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:71V67703S75PFGI |

| IDT71342LA20PF8 | 功能描述:IC SRAM 32KBIT 20NS 64TQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:72 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 同步 存储容量:9M(256K x 36) 速度:75ns 接口:并联 电源电压:3.135 V ~ 3.465 V 工作温度:-40°C ~ 85°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:71V67703S75PFGI |

| IDT71342LA20PFG | 功能描述:IC SRAM 32KBIT 20NS 64TQFP RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:72 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 同步 存储容量:9M(256K x 36) 速度:75ns 接口:并联 电源电压:3.135 V ~ 3.465 V 工作温度:-40°C ~ 85°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:71V67703S75PFGI |

| IDT71342LA20PFG8 | 功能描述:IC SRAM 32KBIT 20NS 64TQFP RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:72 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 同步 存储容量:9M(256K x 36) 速度:75ns 接口:并联 电源电压:3.135 V ~ 3.465 V 工作温度:-40°C ~ 85°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:71V67703S75PFGI |

| IDT71342LA25J | 功能描述:IC SRAM 32KBIT 25NS 52PLCC RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:72 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 同步 存储容量:9M(256K x 36) 速度:75ns 接口:并联 电源电压:3.135 V ~ 3.465 V 工作温度:-40°C ~ 85°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:71V67703S75PFGI |

发布紧急采购,3分钟左右您将得到回复。