- 您现在的位置:买卖IC网 > PDF目录377311 > IDT7143LA45PF (INTEGRATED DEVICE TECHNOLOGY INC) HIGH-SPEED 2K x 16 CMOS DUAL-PORT STATIC RAMS PDF资料下载

参数资料

| 型号: | IDT7143LA45PF |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | DRAM |

| 英文描述: | HIGH-SPEED 2K x 16 CMOS DUAL-PORT STATIC RAMS |

| 中文描述: | 2K X 16 DUAL-PORT SRAM, 45 ns, PQFP100 |

| 封装: | TQFP-100 |

| 文件页数: | 14/16页 |

| 文件大小: | 140K |

| 代理商: | IDT7143LA45PF |

6.42

IDT7133SA/LA, IDT7143SA/LA

High-Speed 2K x 16 Dual-Port RAM Military, Industrial and Commercial Temperature Ranges

The IDT7133/43 provides two ports with separate control, address

and I/O pins that permt independent access for reads or writes to any

location in memory. The IDT7133/43 has an automatic power down

feature controlled by

CE

. The

CE

controls on-chip power down circuitry

that permts the respective port to go into a standby mode when not

selected (

CE

HIGH). When a port is enabled, access to the entire

memory array is permtted. Non-contention READ/WRITE conditions

are illustrated in Truth Table 1.

29

Busy Logic provides a hardware indication that both ports of the

RAMhave accessed the same location at the same time. It also allows

one of the two accesses to proceed and signals the other side that the

RAMis

“

busy

”

. The

BUSY

pin can then be used to stall the access until

the operation on the other side is completed. If a write operation has

been attempted fromthe side that receives a

BUSY

indication, the

write signal is gated internally to prevent the write fromproceeding.

The use of

BUSY

logic is not required or desirable for all applica-

tions. In some cases it may be useful to logically OR the

BUSY

outputs

together and use any

BUSY

indication as an interrupt source to flag the

event of an illegal or illogical operation. If the write inhibit function of

BUSY logic is not desirable, the

BUSY

logic can be disabled by using

the IDT7143 (SLAVE). In the IDT7143, the

BUSY

pin operates solely

as a write inhibit input pin. Normal operation can be programmed by

tying the

BUSY

pins HIGH. If desired, unintended write operations can

be prevented to a port by tying the

BUSY

pin for that port LOW. The

BUSY

outputs on the IDT 7133 RAMare open drain and require pull-

up resistors.

8-* 0*29

/=15%2

When expanding an IDT7133/43 RAMarray in width while using

BUSY

logic, one master part is used to decide which side of the RAM

array will receive a

BUSY

indication, and to output that indication. Any

number of slaves to be addressed in the same address range as the

master, use the

BUSY

signal as a write inhibit signal. Thus on the

IDT7133 RAMthe

BUSY

pin is an output and on the IDT7143 RAM the

BUSY

pin is an input (see Figure 3).

Expanding the data bus width to 32 bits or more in a Dual-Port RAM

systemimplies that several chips will be active at the same time. If each

chip includes a hardware arbitrator, and the addresses for each chip

arrive at the same time, it is possible that one will activate its

BUSY

L

while another activates its

BUSY

R

signal. Both sides are now

BUSY

and the CPUs will await indefinitely for their port to become free.

To avoid the

“

Busy Lock-Out

”

problem IDT has developed a

MASTER/SLAVE approach where only one hardware arbitrator, in the

MASTER, is used. The SLAVE has

BUSY

inputs which allow an

interface to the MASTER with no external components and with a

speed advantage over other systems.

When expanding Dual-Port RAMs in width, the writing of the SLAVE

RAMs must be delayed until after the

BUSY

input has settled.

Otherwise, the SLAVE chip may begin a write cycle during a contention

situation. Conversely, the write pulse must extend a hold time past

BUSY

to ensure that a write cycle takes place after the contention is

resolved. This timng is inherent in all Dual-Port memory systems where

more than one chip is active at the same time.

The write pulse to the SLAVE should be delayed by the maximum

arbitration time of the MASTER. If, then, a contention occurs, the write

to the SLAVE will be inhibited due to

BUSY

fromthe MASTER.

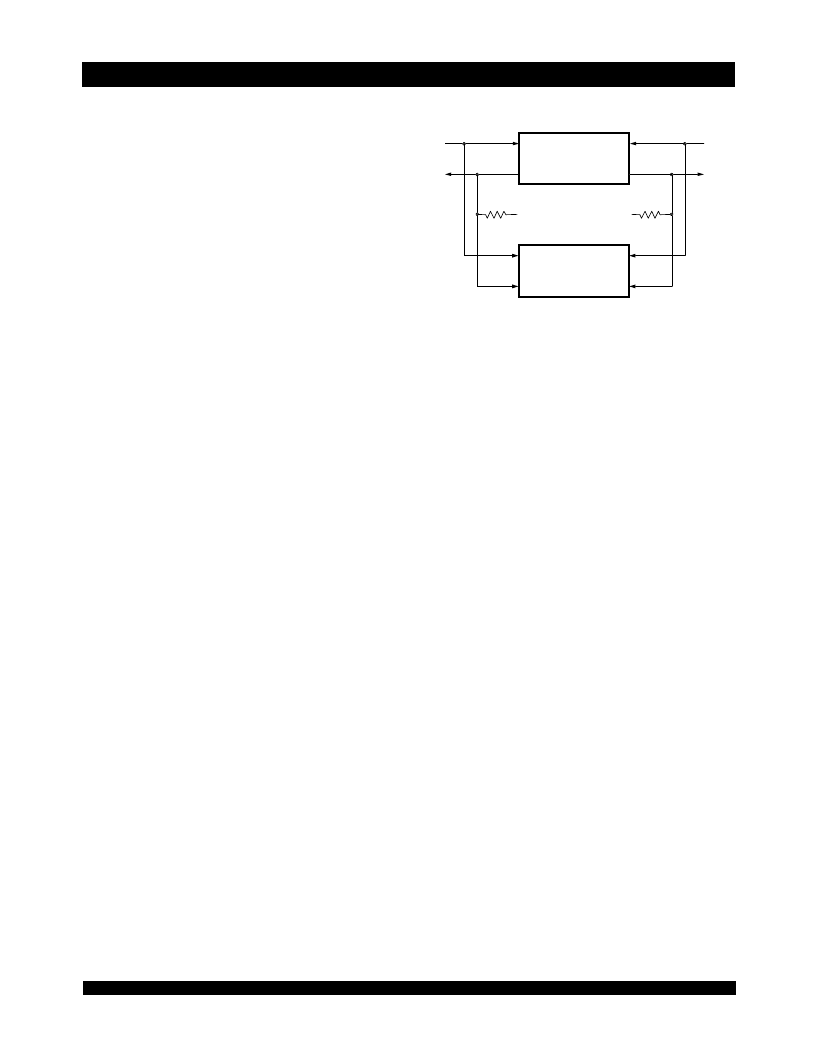

Figure 4

.

Busy and chip enable routing for both width and depth expansion

with the IDT7133 (MASTER) and the IDT7143 (SLAVE).

V

CC

R/

W

BUSY

R/

W

BUSY

IDT7133

MASTER

V

CC

R/

W

BUSY

R/

W

BUSY

R/

W

BUSY

R/

W

BUSY

LEFT

RIGHT

2746drw 15

IDT7143

SLAVE

270

270

相关PDF资料 |

PDF描述 |

|---|---|

| IDT7133SA45PFB | HIGH-SPEED 2K x 16 CMOS DUAL-PORT STATIC RAMS |

| IDT7143SA45PFB | HIGH-SPEED 2K x 16 CMOS DUAL-PORT STATIC RAMS |

| IDT7133LA45PFB | HIGH-SPEED 2K x 16 CMOS DUAL-PORT STATIC RAMS |

| IDT7143LA45PFB | HIGH-SPEED 2K x 16 CMOS DUAL-PORT STATIC RAMS |

| IDT7133LA45PFI | HIGH-SPEED 2K x 16 CMOS DUAL-PORT STATIC RAMS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT7143LA55G | 功能描述:IC SRAM 32KBIT 55NS 68PGA RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

| IDT7143LA55GB | 制造商:Integrated Device Technology Inc 功能描述:IC SRAM 32KBIT 55NS 68PGA |

| IDT7143LA55J | 功能描述:IC SRAM 32KBIT 55NS 68PLCC RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:72 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 同步 存储容量:9M(256K x 36) 速度:75ns 接口:并联 电源电压:3.135 V ~ 3.465 V 工作温度:-40°C ~ 85°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:71V67703S75PFGI |

| IDT7143LA55J8 | 功能描述:IC SRAM 32KBIT 55NS 68PLCC RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:72 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 同步 存储容量:9M(256K x 36) 速度:75ns 接口:并联 电源电压:3.135 V ~ 3.465 V 工作温度:-40°C ~ 85°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:71V67703S75PFGI |

| IDT7143LA55PF | 功能描述:IC SRAM 32KBIT 55NS 100TQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:72 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 同步 存储容量:9M(256K x 36) 速度:75ns 接口:并联 电源电压:3.135 V ~ 3.465 V 工作温度:-40°C ~ 85°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:71V67703S75PFGI |

发布紧急采购,3分钟左右您将得到回复。