- 您现在的位置:买卖IC网 > PDF目录4148 > IDT71V3557S75PFG (IDT, Integrated Device Technology Inc)IC SRAM 4MBIT 75NS 100TQFP PDF资料下载

参数资料

| 型号: | IDT71V3557S75PFG |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 14/28页 |

| 文件大小: | 0K |

| 描述: | IC SRAM 4MBIT 75NS 100TQFP |

| 标准包装: | 72 |

| 格式 - 存储器: | RAM |

| 存储器类型: | SRAM - 同步 ZBT |

| 存储容量: | 4.5M(128K x 36) |

| 速度: | 75ns |

| 接口: | 并联 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | 0°C ~ 70°C |

| 封装/外壳: | 100-LQFP |

| 供应商设备封装: | 100-TQFP(14x14) |

| 包装: | 托盘 |

| 其它名称: | 71V3557S75PFG |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

�� �

�

�

�IDT71V3557,� IDT71V3559,� 128K� x� 36,� 256K� x� 18,� 3.3V� Synchronous� SRAMs� with�

�ZBT?� Feature,� 3.3V� I/O,� Burst� Counter,� and� Flow-Through� Outputs� Commercial� and� Industrial� Temperature� Ranges�

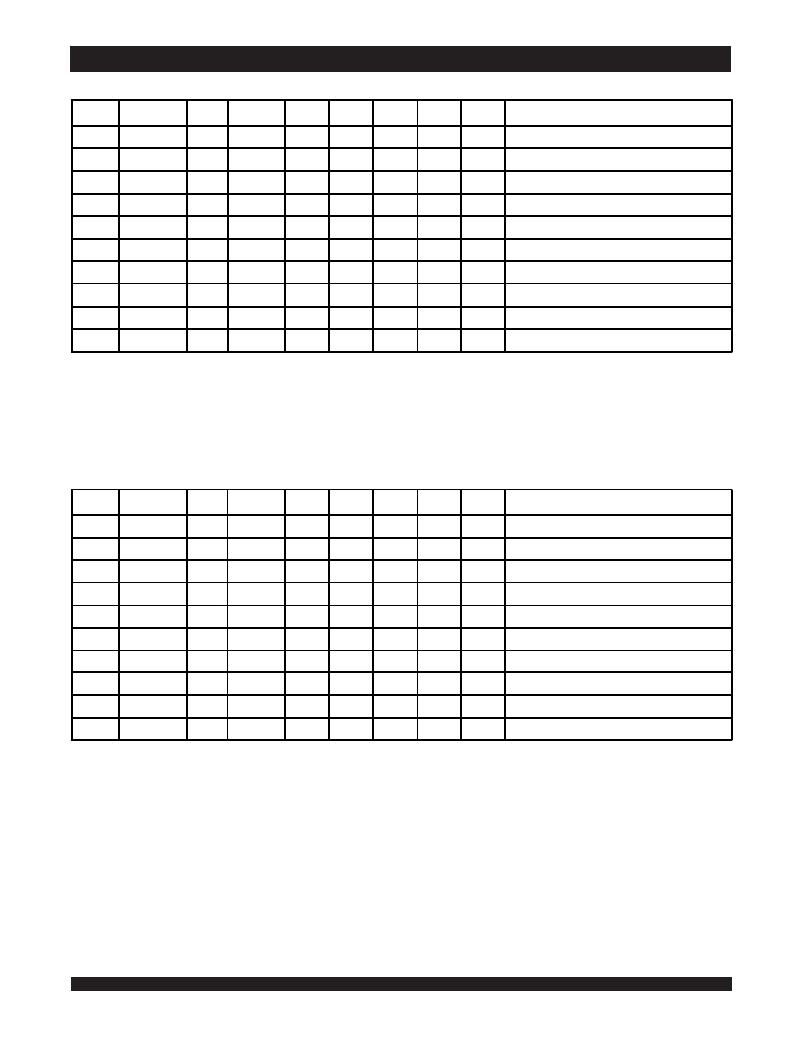

�Read� Operation� with� Chip� Enable� Used� (1)�

�Cycle�

�n�

�n+1�

�n+2�

�n+3�

�n+4�

�n+5�

�n+6�

�n+7�

�n+8�

�n+9�

�Address�

�X�

�X�

�A� 0�

�X�

�A� 1�

�X�

�X�

�A� 2�

�X�

�X�

�R/� W�

�X�

�X�

�H�

�X�

�H�

�X�

�X�

�H�

�X�

�X�

�ADV/� LD�

�L�

�L�

�L�

�L�

�L�

�L�

�L�

�L�

�L�

�L�

�CE� 1� (2)�

�H�

�H�

�L�

�H�

�L�

�H�

�H�

�L�

�H�

�H�

�CEN�

�L�

�L�

�L�

�L�

�L�

�L�

�L�

�L�

�L�

�L�

�BW� x�

�X�

�X�

�X�

�X�

�X�

�X�

�X�

�X�

�X�

�X�

�OE�

�X�

�X�

�X�

�L�

�X�

�L�

�X�

�X�

�L�

�X�

�I/O� (3)�

�?�

�Z�

�Z�

�Q� 0�

�Z�

�Q� 1�

�Z�

�Z�

�Q� 2�

�Z�

�Comments�

�Deselected.�

�Deselected.�

�Address� A� 0� and� Control� meet� setup.�

�Address� A� 0� read� out,� Deselected.�

�Address� A� 1� and� Control� meet� setup.�

�Address� A� 1� read� out,� Deselected.�

�Deselected.�

�Address� A� 2� and� Control� meet� setup.�

�Address� A� 2� read� out,� Deselected.�

�Deselected.�

�NOTES:�

�1.� H� =� High;� L� =� Low;� X� =� Don’t� Care;� ?� =� Don't� Know;� Z� =� High� Impedance.�

�2.� CE� 2� timing� transition� is� identical� to� CE� 1� signal.� CE� 2� timing� transition� is� identical� but� inverted� to� the� CE� 1� and� CE� 2� signals.�

�3.� Device� outputs� are� ensured� to� be� in� High-Z� during� device� power-up.�

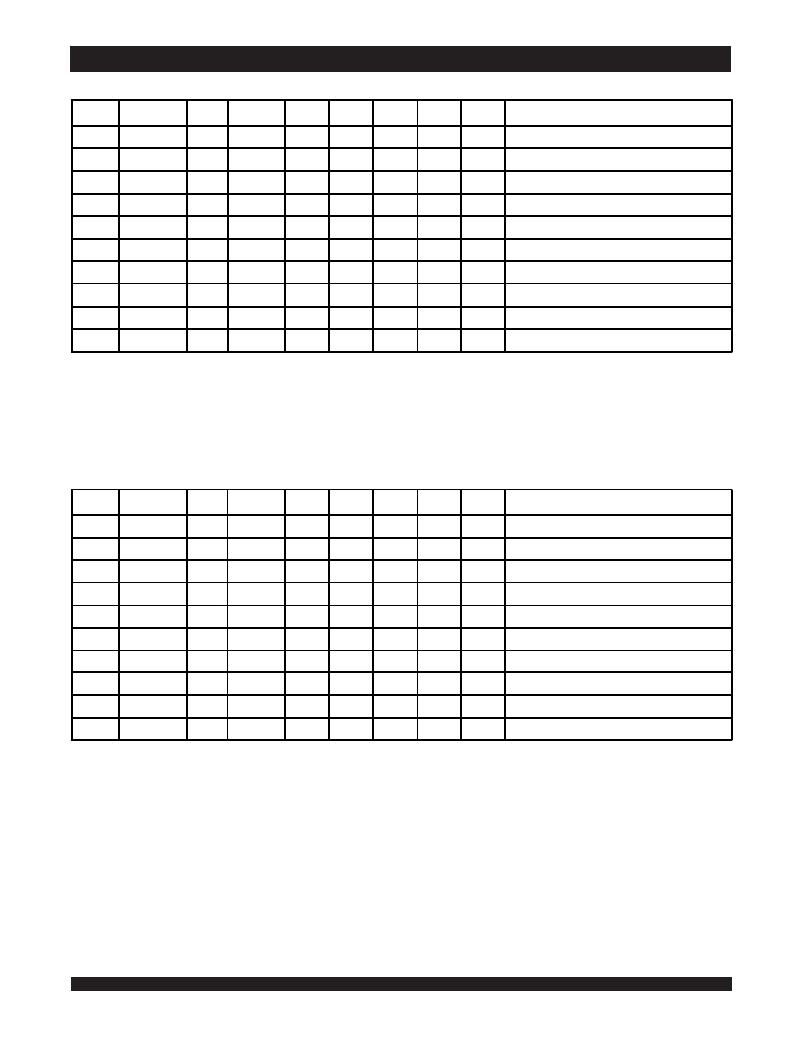

�Write� Operation� with� Chip� Enable� Used� (1)�

�5282� tbl� 19�

�Cycle�

�n�

�n+1�

�n+2�

�n+3�

�n+4�

�n+5�

�n+6�

�n+7�

�n+8�

�n+9�

�Address�

�X�

�X�

�A� 0�

�X�

�A� 1�

�X�

�X�

�A� 2�

�X�

�X�

�R/� W�

�X�

�X�

�L�

�X�

�L�

�X�

�X�

�L�

�X�

�X�

�ADV/� LD�

�L�

�L�

�L�

�L�

�L�

�L�

�L�

�L�

�L�

�L�

�CE� (2)�

�H�

�H�

�L�

�H�

�L�

�H�

�H�

�L�

�H�

�H�

�CEN�

�L�

�L�

�L�

�L�

�L�

�L�

�L�

�L�

�L�

�L�

�BW� x�

�X�

�X�

�L�

�X�

�L�

�X�

�X�

�L�

�X�

�X�

�OE�

�X�

�X�

�X�

�X�

�X�

�X�

�X�

�X�

�X�

�X�

�I/O�

�?�

�Z�

�Z�

�D� 0�

�Z�

�D� 1�

�Z�

�Z�

�D� 2�

�Z�

�Comments�

�Deselected.�

�Deselected.�

�Address� A� 0� and� Control� meet� setup�

�Data� D� 0� Write� In,� Deselected.�

�Address� A� 1� and� Control� meet� setup�

�Data� D� 1� Write� In,� Deselected.�

�Deselected.�

�Address� A� 2� and� Control� meet� setup�

�Data� D� 2� Write� In,� Deselected.�

�Deselected.�

�NOTES:�

�1.� H� =� High;� L� =� Low;� X� =� Don’t� Care;� ?� =� Don't� Know;� Z� =� High� Impedance.�

�2.� CE� =� L� is� defined� as� CE� 1� =� L,� CE� 2� =� L� and� CE2� =� H.� CE� =� H� is� defined� as� CE� 1� =� H,� CE� 2� =� H� or� CE� 2� =� L.�

�14�

�6.42�

�5282� tbl� 20�

�相关PDF资料 |

PDF描述 |

|---|---|

| ACB66DHAT-S621 | EDGECARD 132POS DIP R/A .050 SLD |

| GEC60DTEI | CONN EDGECARD 120POS .100 EYELET |

| AMM36DRST-S288 | CONN EDGECARD 72POS .156 EXTEND |

| AMC35DRYI-S93 | CONN EDGECARD 70POS DIP .100 SLD |

| 65801-042LF | CLINCHER RECEPTACLE ASS'-Y-GOLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT71V3557S75PFG8 | 功能描述:IC SRAM 4MBIT 75NS 100TQFP RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:72 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 同步 存储容量:4.5M(256K x 18) 速度:133MHz 接口:并联 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x20) 包装:托盘 |

| IDT71V3557S75PFGI | 功能描述:IC SRAM 4MBIT 75NS 100TQFP RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:2,000 系列:MoBL® 格式 - 存储器:RAM 存储器类型:SRAM - 异步 存储容量:16M(2M x 8,1M x 16) 速度:45ns 接口:并联 电源电压:2.2 V ~ 3.6 V 工作温度:-40°C ~ 85°C 封装/外壳:48-VFBGA 供应商设备封装:48-VFBGA(6x8) 包装:带卷 (TR) |

| IDT71V3557S75PFGI8 | 功能描述:IC SRAM 4MBIT 75NS 100TQFP RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:72 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 同步 存储容量:4.5M(256K x 18) 速度:133MHz 接口:并联 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x20) 包装:托盘 |

| IDT71V3557S75PFI | 功能描述:IC SRAM 4MBIT 75NS 100TQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 产品变化通告:Product Discontinuation 05/Nov/2008 标准包装:84 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 同步 ZBT 存储容量:4.5M(128K x 36) 速度:75ns 接口:并联 电源电压:3.135 V ~ 3.465 V 工作温度:-40°C ~ 85°C 封装/外壳:119-BGA 供应商设备封装:119-PBGA(14x22) 包装:托盘 其它名称:71V3557SA75BGI |

| IDT71V3557S75PFI8 | 功能描述:IC SRAM 4MBIT 75NS 100TQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 产品变化通告:Product Discontinuation 05/Nov/2008 标准包装:84 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 同步 ZBT 存储容量:4.5M(128K x 36) 速度:75ns 接口:并联 电源电压:3.135 V ~ 3.465 V 工作温度:-40°C ~ 85°C 封装/外壳:119-BGA 供应商设备封装:119-PBGA(14x22) 包装:托盘 其它名称:71V3557SA75BGI |

发布紧急采购,3分钟左右您将得到回复。