- 您现在的位置:买卖IC网 > PDF目录4159 > IDT71V546S133PFG (IDT, Integrated Device Technology Inc)IC SRAM 4MBIT 133MHZ 100TQFP PDF资料下载

参数资料

| 型号: | IDT71V546S133PFG |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 6/21页 |

| 文件大小: | 0K |

| 描述: | IC SRAM 4MBIT 133MHZ 100TQFP |

| 标准包装: | 72 |

| 格式 - 存储器: | RAM |

| 存储器类型: | SRAM - 同步 ZBT |

| 存储容量: | 4.5M(128K x 36) |

| 速度: | 133MHz |

| 接口: | 并联 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | 0°C ~ 70°C |

| 封装/外壳: | 100-LQFP |

| 供应商设备封装: | 100-TQFP(14x14) |

| 包装: | 托盘 |

| 其它名称: | 71V546S133PFG |

�� �

�

�

�IDT71V546,� 128K� x� 36,� 3.3V� Synchronous� SRAM� with�

�ZBT� ?� Feature,� Burst� Counter� and� Pipelined� Outputs�

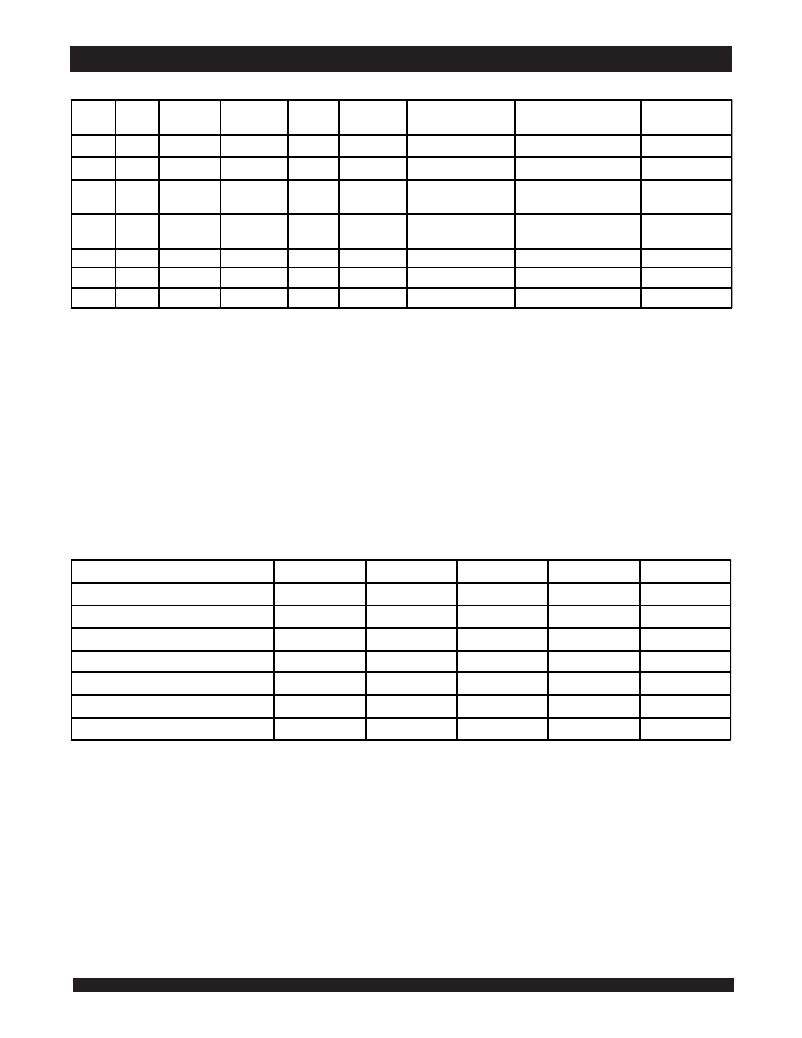

�Synchronous� Truth� Table� (1)�

�Commercial� and� Industrial� Temperature� Ranges�

�CEN�

�R/� W�

�Chip� (5)�

�ADV/� LD�

�BW� x�

�ADDRESS�

�PREVIOUIS� CYCLE�

�CURRENT� CYCLE�

�I/O�

�Enable�

�USED�

�(2� cycles� later)�

�SUSPEND�

�L�

�L�

�L�

�L�

�L�

�L�

�H�

�L�

�H�

�X�

�X�

�X�

�X�

�X�

�Select�

�Select�

�X�

�X�

�Deselect�

�X�

�X�

�L�

�L�

�H�

�H�

�L�

�H�

�X�

�Valid�

�X�

�Valid�

�X�

�X�

�X�

�X�

�External�

�External�

�Internal�

�Internal�

�X�

�X�

�X�

�X�

�X�

�LOAD� WRITE/�

�BURST� WRITE�

�LOAD� READ/�

�BURST� READ�

�X�

�DESELECT� /� NOOP�

�X�

�LOAD� WRITE�

�LOAD� READ�

�BURST� WRITE�

�(Advance� Burst� Counter)� (2)�

�BURST� READ�

�(Advance� Burst� Counter)� (2)�

�DESELECT� or� STOP� (3)�

�NOOP�

�(4)�

�D� (7)�

�Q� (7)�

�D� (7)�

�Q� (7)�

�HiZ�

�HiZ�

�Previous� Value�

�NOTES:�

�3821� tbl� 07�

�1.� L� =� V� IL� ,� H� =� V� IH� ,� X� =� Don’t� Care.�

�2.� When� ADV/� LD� signal� is� sampled� high,� the� internal� burst� counter� is� incremented.� The� R/� W� signal� is� ignored� when� the� counter� is� advanced.� Therefore� the� nature� of�

�the� burst� cycle� (Read� or� Write)� is� determined� by� the� status� of� the� R/� W� signal� when� the� first� address� is� loaded� at� the� beginning� of� the� burst� cycle.�

�3.� Deselect� cycle� is� initiated� when� either� (� CE� 1� ,� or� CE� 2� is� sampled� high� or� CE� 2� is� sampled� low)� and� ADV/� LD� is� sampled� low� at� rising� edge� of� clock.� The� data� bus� will�

�tri-state� two� cycles� after� deselect� is� initiated.�

�4.� When� CEN� is� sampled� high� at� the� rising� edge� of� clock,� that� clock� edge� is� blocked� from� propogating� through� the� part.� The� state� of� all� the� internal� registers� and� the� I/�

�Os� remains� unchanged.�

�5.� To� select� the� chip� requires� CE� 1� =� L,� CE� 2� =� L,� CE� 2� =� H� on� these� chip� enables.� Chip� is� deselected� if� either� one� of� the� chip� enables� is� false.�

�6.� Device� Outputs� are� ensured� to� be� in� High-Z� after� the� first� rising� edge� of� clock� upon� power-up.�

�7.� Q� -� Data� read� from� the� device,� D� -� data� written� to� the� device.�

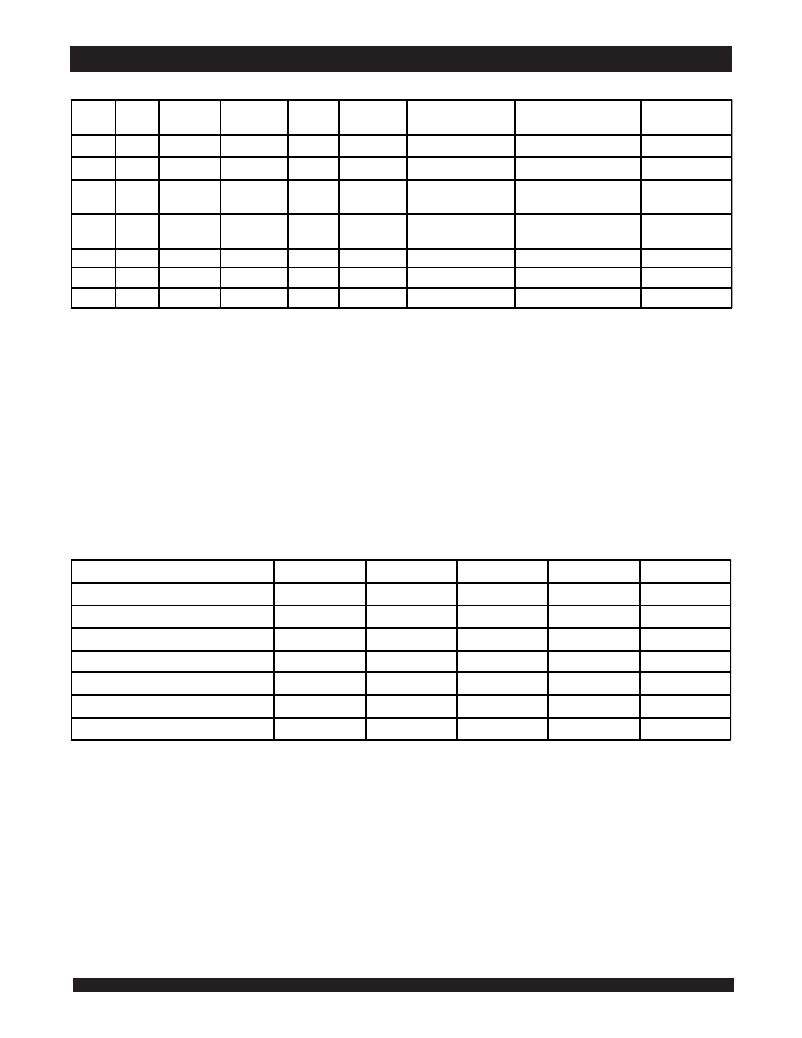

�Partial� Truth� Table� for� Writes� (1)�

�WRITE� BYTE� 1� (I/O� [0:7],� I/O� P1� )�

�WRITE� BYTE� 4� (I/O� [24:31],� I/O� P4� )�

�Operation�

�READ�

�WRITE� ALL� BYTES�

�(2)�

�WRITE� BYTE� 2� (I/O� [8:15],� I/O� P2� )� (2)�

�WRITE� BYTE� 3� (I/O� [16:23],� I/O� P3� )� (2)�

�(2)�

�NO� WRITE�

�R/� W�

�H�

�L�

�L�

�L�

�L�

�L�

�L�

�BW� 1�

�X�

�L�

�L�

�H�

�H�

�H�

�H�

�BW� 2�

�X�

�L�

�H�

�L�

�H�

�H�

�H�

�BW� 3�

�X�

�L�

�H�

�H�

�L�

�H�

�H�

�BW� 4�

�X�

�L�

�H�

�H�

�H�

�L�

�H�

�NOTES:�

�1.� L� =� V� IL� ,� H� =� V� IH� ,� X� =� Don’t� Care.�

�2.� Multiple� bytes� may� be� selected� during� the� same� cycle.�

�6�

�3821� tbl� 08�

�相关PDF资料 |

PDF描述 |

|---|---|

| 65801-038LF | CLINCHER RECEPTACLE 9POS GOLD |

| 65801-036LF | CLINCHER RECEPTACLE 7POS GOLD |

| 65801-013LF | CONN RCPT 13POS 2.54MM VERT TIN |

| 1-487378-3 | CONN RECEPT 14POS .100 SLIMLINE |

| FMC26DRYI-S13 | CONN EDGECARD 52POS .100 EXTEND |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT71V546S133PFG8 | 功能描述:IC SRAM 4MBIT 133MHZ 100TQFP RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:72 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 同步 存储容量:4.5M(256K x 18) 速度:133MHz 接口:并联 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x20) 包装:托盘 |

| IDT71V546S133PFGI | 功能描述:IC SRAM 4MBIT 133MHZ 100TQFP RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:2,000 系列:MoBL® 格式 - 存储器:RAM 存储器类型:SRAM - 异步 存储容量:16M(2M x 8,1M x 16) 速度:45ns 接口:并联 电源电压:2.2 V ~ 3.6 V 工作温度:-40°C ~ 85°C 封装/外壳:48-VFBGA 供应商设备封装:48-VFBGA(6x8) 包装:带卷 (TR) |

| IDT71V546S133PFGI8 | 功能描述:IC SRAM 4MBIT 133MHZ 100TQFP RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:2,000 系列:MoBL® 格式 - 存储器:RAM 存储器类型:SRAM - 异步 存储容量:16M(2M x 8,1M x 16) 速度:45ns 接口:并联 电源电压:2.2 V ~ 3.6 V 工作温度:-40°C ~ 85°C 封装/外壳:48-VFBGA 供应商设备封装:48-VFBGA(6x8) 包装:带卷 (TR) |

| IDT71V546S133PFI | 功能描述:IC SRAM 4MBIT 133MHZ 100TQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:576 系列:- 格式 - 存储器:闪存 存储器类型:闪存 - NAND 存储容量:512M(64M x 8) 速度:- 接口:并联 电源电压:2.7 V ~ 3.6 V 工作温度:-40°C ~ 85°C 封装/外壳:48-TFSOP(0.724",18.40mm 宽) 供应商设备封装:48-TSOP 包装:托盘 其它名称:497-5040 |

| IDT71V546S133PFI8 | 功能描述:IC SRAM 4MBIT 133MHZ 100TQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:576 系列:- 格式 - 存储器:闪存 存储器类型:闪存 - NAND 存储容量:512M(64M x 8) 速度:- 接口:并联 电源电压:2.7 V ~ 3.6 V 工作温度:-40°C ~ 85°C 封装/外壳:48-TFSOP(0.724",18.40mm 宽) 供应商设备封装:48-TSOP 包装:托盘 其它名称:497-5040 |

发布紧急采购,3分钟左右您将得到回复。