- 您现在的位置:买卖IC网 > PDF目录299201 > IDT72851L25TFG (INTEGRATED DEVICE TECHNOLOGY INC) 8K X 9 BI-DIRECTIONAL FIFO, 15 ns, PQFP64 PDF资料下载

参数资料

| 型号: | IDT72851L25TFG |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | FIFO |

| 英文描述: | 8K X 9 BI-DIRECTIONAL FIFO, 15 ns, PQFP64 |

| 封装: | GREEN, SLIM, TQFP-64 |

| 文件页数: | 1/16页 |

| 文件大小: | 176K |

| 代理商: | IDT72851L25TFG |

IDT, IDT logo and the

SyncFIFO logo are trademarks of Integrated Device Technology, Inc.

FEBRUARY 2006

DUAL CMOS SyncFIFO

DUAL 256 x 9, DUAL 512 x 9,

DUAL 1,024 x 9, DUAL 2,048 x 9,

DUAL 4,096 x 9, DUAL 8,192 x 9

IDT72801

IDT72811

IDT72821

IDT72831

IDT72841

IDT72851

COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGE

1

2006 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice.

DSC-3034/3

FEATURES:

The IDT72801 is equivalent to two IDT72201 256 x 9 FIFOs

The IDT72811 is equivalent to two IDT72211 512 x 9 FIFOs

The IDT72821 is equivalent to two IDT72221 1,024 x 9 FIFOs

The IDT72831 is equivalent to two IDT72231 2,048 x 9 FIFOs

The IDT72841 is equivalent to two IDT72241 4,096 x 9 FIFOs

The IDT72851 is equivalent to two IDT72251 8,192 x 9 FIFOs

Offers optimal combination of large capacity, high speed,

design flexibility and small footprint

Ideal for prioritization, bidirectional, and width expansion

applications

10 ns read/write cycle time for the IDT72801/72811/72821/72831/

72841/72851

Separate control lines and data lines for each FIFO

Separate Empty, Full, Programmable Almost-Empty and Almost-

Full flags for each FIFO

Enable puts output data lines in high-impedance state

Space-saving 64-pin Thin Quad Flat Pack (TQFP) and Slim Thin

Quad Flatpack (STQFP)

Industrial temperature range (–40

°°°°°C to +85°°°°°C) is available

Green parts available, see ordering information

DESCRIPTION:

The IDT72801/72811/72821/72831/72841/72851 are dual synchronous

(clocked)FIFOs. ThedeviceisfunctionallyequivalenttotwoIDT72201/72211/

72221/72231/72241/72251 FIFOs in a single package with all associated

control, data, and flag lines assigned to separate pins.

Each of the two FIFOs (designated FIFO A and FIFO B) contained in the

IDT72801/72811/72821/72831/72841/72851 has a 9-bit input data port (DA0

- DA8, DB0 - DB8) and a 9-bit output data port (QA0 - QA8, QB0 - QB8). Each

inputportiscontrolledbyafree-runningclock(WCLKA,WCLKB),andtwoWrite

Enable pins (

WENA1,WENA2,WENB1,WENB2). Dataiswrittenintoeachof

the two arrays on every rising clock edge of the Write Clock (WCLKA, WCLKB)

when the appropriate write enable pins are asserted.

The output port of each FIFO bank is controlled by its associated clock pin

(RCLKA, RCLKB) and two Read Enable pins (

RENA1, RENA2, RENB1,

RENB2).TheReadClockcanbetiedtotheWriteClockforsingleclockoperation

orthetwoclockscanrunasynchronousofoneanotherfordualclockoperation.

An Output Enable pin (

OEA, OEB) is provided on the read port of each FIFO

for three-state output control.

Each of the two FIFOs has two fixed flags, Empty (

EFA,EFB)andFull(FFA,

FFB). Twoprogrammableflags,Almost-Empty(PAEA,PAEB)andAlmost-Full

(

PAFA,PAFB),areprovidedforeachFIFObanktoimprovememoryutilization.

If not programmed, the programmable flags default to empty+7 for

PAEAand

PAEB, and full-7 for PAFA and PAFB.

TheIDT72801/72811/72821/72831/72841/72851architecturelendsitself

to many flexible configurations such as:

2-level priority data buffering

Bidirectional operation

Width expansion

Depth expansion

These FIFOs is fabricated using IDT's high-performance submicron

CMOS technology.

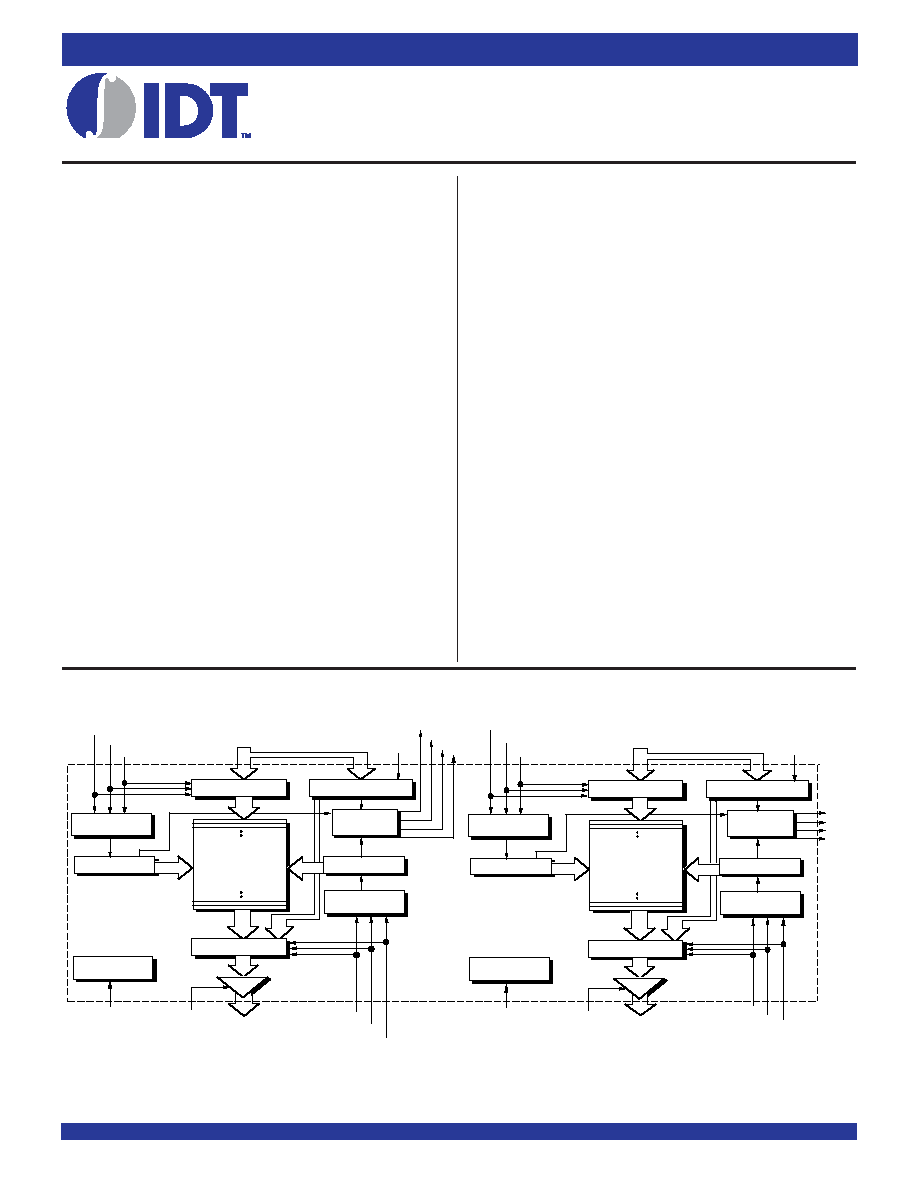

FUNCTIONAL BLOCK DIAGRAM

WCLKA

WENA1

WENA2

DA0 - DA8

LDA

OFFSET REGISTER

INPUT REGISTER

RAM ARRAY

256 x 9, 512 x 9,

1024 x 9, 2048 x 9,

4096 x 9, 8192 x 9

WRITE CONTROL

LOGIC

WRITE POINTER

RESET LOGIC

OUTPUT REGISTER

OEA

RSA

QA0 - QA8

RCLKA

RENA1

RENA2

READ CONTROL

LOGIC

READ POINTER

FLAG

LOGIC

EFA

PAEA

PAFA

FFA

3034 drw 01

WCLKB

WENB1

WENB2

DB0 - DB8

LDB

OFFSET REGISTER

INPUT REGISTER

WRITE CONTROL

LOGIC

WRITE POINTER

RESET LOGIC

OUTPUT REGISTER

OEB

RSB

QB0 - QB8

RCLKB

RENB1

RENB2

READ CONTROL

LOGIC

READ POINTER

FLAG

LOGIC

EFB

PAEB

PAFB

FFB

RAM ARRAY

256 x 9, 512 x 9,

1024 x 9, 2048 x 9,

4096 x 9, 8192 x 9

相关PDF资料 |

PDF描述 |

|---|---|

| IDT72T3675L4-4BB | 8K X 36 OTHER FIFO, 3.4 ns, PBGA208 |

| IDT72V2105L15PFI | 3.3 VOLT HIGH DENSITY CMOS SUPERSYNC FIFO 131,072 x 18 262,144 x 18 |

| IDT72V36100L15PFI | 3.3 VOLT HIGH-DENSITY SUPERSYNC II⑩ 36-BIT FIFO |

| IDT72V36100L6BB | 3.3 VOLT HIGH-DENSITY SUPERSYNC II⑩ 36-BIT FIFO |

| IDT72V36100L6PF | 3.3 VOLT HIGH-DENSITY SUPERSYNC II⑩ 36-BIT FIFO |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72851L25TFI | 功能描述:IC FIFO SYNC DUAL 8192X9 64QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:7200 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72851L25TFI8 | 功能描述:IC FIFO SYNC DUAL 8192X9 64QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:7200 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT7285L12PA | 功能描述:IC FIFO 4096X18 12NS 56TSSOP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:7200 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT7285L12PA8 | 功能描述:IC FIFO 4096X18 12NS 56TSSOP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:7200 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT7285L12PAG | 制造商:Integrated Device Technology Inc 功能描述:IC FIFO 4096X18 12NS 56TSSOP |

发布紧急采购,3分钟左右您将得到回复。