- 您现在的位置:买卖IC网 > PDF目录9902 > IDT72T3695L6-7BB (IDT, Integrated Device Technology Inc)IC FIFO 32768X36 6-7NS 208BGA PDF资料下载

参数资料

| 型号: | IDT72T3695L6-7BB |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 13/57页 |

| 文件大小: | 0K |

| 描述: | IC FIFO 32768X36 6-7NS 208BGA |

| 标准包装: | 1 |

| 系列: | 72T |

| 功能: | 异步,同步 |

| 存储容量: | 1.1M(32K x 36) |

| 数据速率: | 66MHz |

| 访问时间: | 3.8ns |

| 电源电压: | 2.375 V ~ 2.625 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 208-BGA |

| 供应商设备封装: | 208-PBGA(17x17) |

| 包装: | 托盘 |

| 其它名称: | 72T3695L6-7BB |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页

20

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

IDT72T3645/55/65/75/85/95/105/115/125 2.5V TeraSync

36-BIT FIFO

1K x 36, 2K x 36, 4K x 36, 8K x 36, 16K x 36, 32K x 36, 64K x 36, 128K x 36 and 256K x 36

FEBRUARY 4, 2009

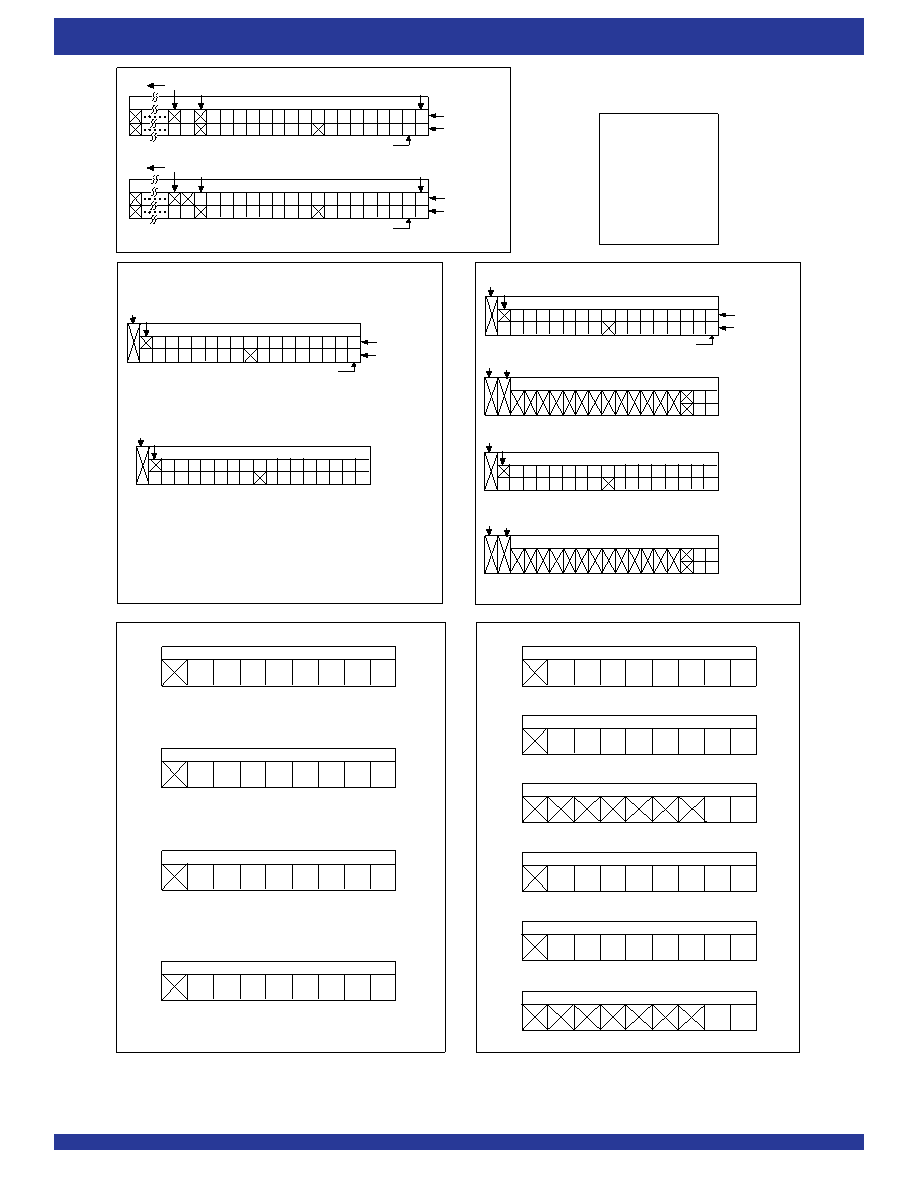

Figure 3. Programmable Flag Offset Programming Sequence (Continued)

# of Bits Used:

10 bits for the IDT72T3645

11 bits for the IDT72T3655

12 bits for the IDT72T3665

13 bits for the IDT72T3675

14 bits for the IDT72T3685

15 bits for the IDT72T3695

16 bits for the IDT72T36105

17 bits for the IDT72T36115

18 bits for the IDT72T36125

Note: All unused bits of the

LSB & MSB are don’t care

5907 drw07

D/Q17

D/Q0

D/Q8

EMPTY OFFSET REGISTER (PAE)

# of Bits Used

2

3

4

5

6

7

9

10

11

12

13

14

15

16

1st Parallel Offset Write/Read Cycle

2

3

4

5

6

7

8

12

13

14

15

16

17

11

Interspersed

Parity

17

10

1

8

D/Q35

D/Q19

9

D/Q17

D/Q0

D/Q8

FULL OFFSET REGISTER (PAF)

# of Bits Used

2

3

4

5

6

7

9

10

11

12

13

14

15

16

2nd Parallel Offset Write/Read Cycle

2

3

4

5

6

7

8

12

13

14

15

16

17

11

Interspersed

Parity

17

10

1

8

9

IDT72T3645/55/65/75/85/95/105/115/125

x36 Bus Width

Non-Interspersed

Parity

Non-Interspersed

Parity

D/Q35

D/Q19

D/Q17

D/Q0

D/Q16

EMPTY OFFSET (LSB) REGISTER (PAE)

Data Inputs/Outputs

# of Bits Used

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

1st Parallel Offset Write/Read Cycle

Data Inputs/Outputs

2nd Parallel Offset Write/Read Cycle

1

2

3

4

5

6

7

8

10

11

12

13

14

15

9

FULL OFFSET (LSB) REGISTER (PAF)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

1

2

3

4

5

6

7

8

10

11

12

13

14

15

9

Non-Interspersed

Parity

Interspersed

Parity

D/Q0

D/Q8

16

D/Q17

D/Q16

IDT72T3645/55/65/75/85/95/105

x18 Bus Width

D/Q17

D/Q0

D/Q16

EMPTY OFFSET (LSB) REGISTER (PAE)

Data Inputs/Outputs

# of Bits Used

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

EMPTY OFFSET (MSB) REGISTER (PAE)

Data Inputs/Outputs

17

16

1st Parallel Offset Write/Read Cycle

2nd Parallel Offset Write/Read Cycle

Data Inputs/Outputs

3rd Parallel Offset Write/Read Cycle

4th Parallel Offset Write/Read Cycle

1

2

3

4

5

6

7

8

10

11

12

13

14

15

9

FULL OFFSET (LSB) REGISTER (PAF)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

1

2

3

4

5

6

7

8

10

11

12

13

14

15

9

FULL OFFSET (MSB) REGISTER (PAF)

17

Non-Interspersed

Parity

Interspersed

Parity

D/Q0

D/Q8

16

17

D/Q17 D/Q16

D/Q17

D/Q16

D/Q17 D/Q16

IDT72T36115/72T36125

x18 Bus Width

18

D/Q8

D/Q0

EMPTY OFFSET REGISTER (PAE)

1

2

3

4

5

6

7

8

1st Parallel Offset Write/Read Cycle

2nd Parallel Offset Write/Read Cycle

3rd Parallel Offset Write/Read Cycle

4th Parallel Offset Write/Read Cycle

D/Q8

D/Q0

EMPTY OFFSET REGISTER (PAE)

9

10

11

12

13

14

15

16

D/Q8

D/Q0

FULL OFFSET REGISTER (PAF)

1

2

3

4

5

6

7

8

D/Q8

D/Q0

EMPTY OFFSET REGISTER (PAE)

17

5th Parallel Offset Write/Read Cycle

D/Q8

D/Q0

FULL OFFSET REGISTER (PAF)

9

10

11

12

13

14

15

16

6th Parallel Offset Write/Read Cycle

D/Q8

D/Q0

17

FULL OFFSET REGISTER (PAF)

IDT72T36115/72T36125

x9 Bus Width

18

D/Q8

D/Q0

EMPTY OFFSET REGISTER (PAE)

1

2

3

4

5

6

7

8

1st Parallel Offset Write/Read Cycle

2nd Parallel Offset Write/Read Cycle

3rd Parallel Offset Write/Read Cycle

D/Q8

D/Q0

EMPTY OFFSET REGISTER (PAE)

9

10

11

12

13

14

15

16

D/Q8

D/Q0

FULL OFFSET REGISTER (PAF)

1

2

3

4

5

6

7

8

4th Parallel Offset Write/Read Cycle

D/Q8

D/Q0

FULL OFFSET REGISTER (PAF)

9

10

11

12

13

14

15

16

IDT72T3645/55/65/75/85/95/105

x9 Bus Width

NOTE:

1. Consecutive reads of the offset registers is not permitted. The read operation must be disabled for a minimum of one RCLK cycle in between offset register accesses. (Please

refer to Figure 22, Parallel Read of Programmable Flag Registers (IDT Standard and FWFT Modes) for more details).

相关PDF资料 |

PDF描述 |

|---|---|

| V48A28T500BF3 | CONVERTER MOD DC/DC 28V 500W |

| IDT72T1895L6-7BB | IC FIFO 65536X18 6-7NS 144BGA |

| MS27508E12F4PC | CONN RCPT 4POS BOX MNT W/PINS |

| V48A28T500BF2 | CONVERTER MOD DC/DC 28V 500W |

| MS27508E12A4PB | CONN RCPT 4POS BOX MNT W/PINS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72T40108L10BB | 功能描述:IC FIFO DDR/SDR 10NS 208-BGA RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72T 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72T40108L4BB | 功能描述:IC FIFO DDR/SDR 4NS 208-BGA RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72T 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72T40108L5BB | 功能描述:IC FIFO DDR/SDR 5NS 208-BGA RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72T 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72T40108L6-7BB | 功能描述:IC FIFO DDR/SDR 6-7NS 208-BGA RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72T 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72T40118L10BB | 功能描述:IC FIFO DDR/SDR 10NS 208-BGA RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72T 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

发布紧急采购,3分钟左右您将得到回复。