- 您现在的位置:买卖IC网 > PDF目录4581 > IDT72T6360L6BB (IDT, Integrated Device Technology Inc)IC FLOW-CTRL 36BIT 6NS 324-BGA PDF资料下载

参数资料

| 型号: | IDT72T6360L6BB |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 13/51页 |

| 文件大小: | 0K |

| 描述: | IC FLOW-CTRL 36BIT 6NS 324-BGA |

| 标准包装: | 1 |

| 类型: | 连续流量控制 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 324-BGA |

| 供应商设备封装: | 324-PBGA(19x19) |

| 包装: | 托盘 |

| 其它名称: | 72T6360L6BB |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页

20

IDT72T6360 2.5V, SEQUENTIAL FLOW-CONTROL DEVICE

x9, x18, x36 BIT WIDE CONFIGURATION

COMMERCIALANDINDUSTRIAL

TEMPERATURERANGES

FEBRUARY 10, 2009

ERROR DETECTION AND CORRECTION

TheErrorDetectionandCorrection(EDC)featureisavailabletoensuredata

integrity between the DDR SDRAM interface and the SFC. The EDC corrects

all single bit hard and soft errors that are accessed from the DDR SDRAM.

Multiple bit errors are not detected nor corrected.

The EDC logic blocks consist of a check bit generator and error detection

correction logic.WhentheEDCisenabled,thecheckbitgeneratorwillgenerate

8 syndrome bits on the 8-byte boundary. The 8 syndrome bits are written into

the DDR SDRAM along with the data. The SFC will burst write two cycles for

data, and one cycle for syndrome bits. In order to minimize overhead and

increasethroughput,notallmemoryintheDDRSDRAMisutilized.Table5 lists

the total usable memory for all 7 configurations when the EDC is enabled.

When a read operation is performed, the syndrome bits will be transferred

to the error detection correction logic block and decoded to determine whether

there are any single bit errors on the data. Single bit errors will be corrected

and data is passed through to the QP cache.

The EDC is enabled using the MIC[2:0] pins. When the EDC is enabled, the

dynamicsofthetotalusablememoryintheDDRSDRAMandtheSFCoperating

speed will vary, listed in Tables 6 and 7. Table 8 shows how to enable the EDC

feature for the 7 configurations

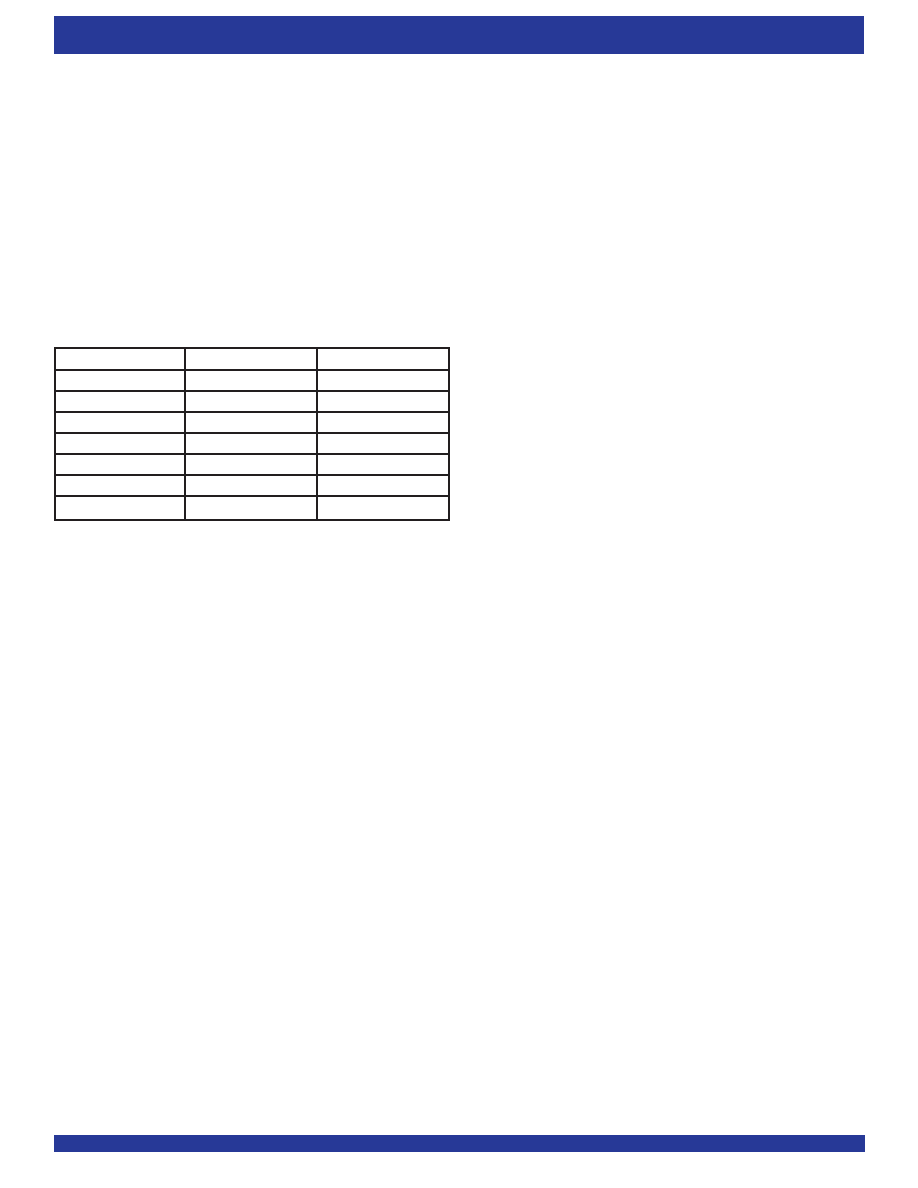

EDC Off

EDC On

Configuration 1

MIC [2:0] = 000

MIC [2:0] = 010

Configuration 2

MIC [2:0] = 001

MIC [2:0] = 011

Configuration 3

MIC [2:0] = 111

MIC [2:0] = 101

Configuration 4

MIC [2:0] = 100

MIC [2:0] = 110

Configuration 5

MIC [2:0] = 000

MIC [2:0] = 010

Configuration 6

MIC [2:0] = 100

MIC [2:0] = 110

Configuration 7

MIC [2:0] = 111

MIC [2:0] = 101

TABLE 8 – MIC[2:0] CONFIGURATIONS

相关PDF资料 |

PDF描述 |

|---|---|

| IDT77V500S25BCG8 | IC SW MEMORY 8X8 1.2BGPS 144-BGA |

| IDT77V500S25BC8 | IC SW MEMORY 8X8 1.2BGPS 144-BGA |

| LT1764AEFE-2.5#TRPBF | IC REG LDO 2.5V 3A 16TSSOP |

| LFXP10E-5F388C | IC FPGA 9.7KLUTS 244I/O 388-BGA |

| LFXP10E-4F388I | IC FPGA 9.7KLUTS 244I/O 388-BGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72T6360L6BBG | 功能描述:IC FLOW-CTRL 36BIT 6NS 324-BGA RoHS:是 类别:集成电路 (IC) >> 专用 IC 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT72T6360L7-5BB | 功能描述:IC FLOW-CTRL 48BIT 7-5NS 324-BGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT72T6360L7-5BBI | 功能描述:IC FLOW-CTRL 48BIT 7-5NS 324-BGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT72T6480L10BB | 功能描述:IC FLOW-CTRL 48BIT 10NS 324-BGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT72T6480L10BBI | 功能描述:IC FLOW-CTRL 48BIT 10NS 324-BGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

发布紧急采购,3分钟左右您将得到回复。