- 您现在的位置:买卖IC网 > PDF目录10114 > IDT72V201L10J8 (IDT, Integrated Device Technology Inc)IC FIFO SYNC 256X9 10NS 32-PLCC PDF资料下载

参数资料

| 型号: | IDT72V201L10J8 |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 5/14页 |

| 文件大小: | 0K |

| 描述: | IC FIFO SYNC 256X9 10NS 32-PLCC |

| 标准包装: | 750 |

| 系列: | 72V |

| 功能: | 同步 |

| 存储容量: | 2.3K(256 x 9) |

| 访问时间: | 10ns |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-LCC(J 形引线) |

| 供应商设备封装: | 32-PLCC(13.97x11.43) |

| 包装: | 带卷 (TR) |

| 其它名称: | 72V201L10J8 |

13

IDT72V201/72V211/72V221/72V231/72V241/72V251 3.3V CMOS SyncFIFO

256 x 9, 512 x 9, 1,024 x 9, 2,048 x 9, 4,096 x 9 and 8,192 x 9

COMMERCIALANDINDUSTRIAL

TEMPERATURERANGES

the Read Enable 2 (REN2) control input can be grounded (see Figure 14). In

thisconfiguration,theWriteEnable2/Load(WEN2/LD)pinissetLOWatReset

so that the pin operates as a control to load and read the programmable flag

offsets.

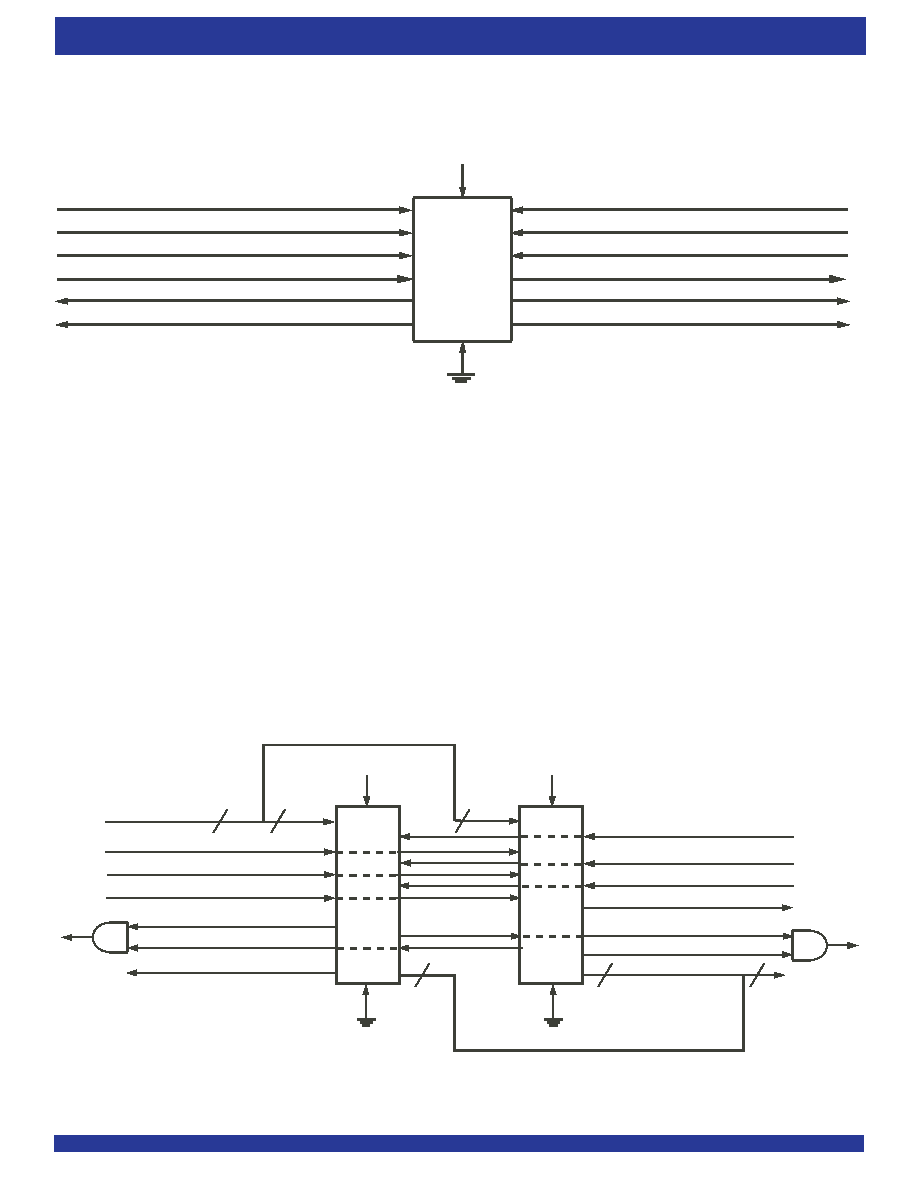

Figure 15. Block Diagram of 256 x 18, 512 x 18, 1,024 x 18, 2,048 x 18, 4,096 x 18 and 8,192 x 18

Synchronous FIFO Used in a Width Expansion Configuration

OPERATINGCONFIGURATIONS

SINGLE DEVICE CONFIGURATION

A single IDT72V201/72V211/72V221/72V231/72V241/72V251 may be

usedwhentheapplicationrequirementsarefor256/512/1,024/2,048/4,096/

8,192wordsorless. WhentheseFIFOsareinaSingleDeviceConfiguration,

1,024/2,048/4,096/8,192words. Theexistenceoftwoenablepinsontheread

andwriteportallowdepthexpansion. TheWriteEnable2/Loadpinisusedas

a second write enable in a depth expansion configuration thus the program-

mableflagsaresettothedefaultvalues. Depthexpansionispossiblebyusing

oneenableinputforsystemcontrolwhiletheotherenableinputiscontrolledby

expansionlogictodirecttheflowofdata. Atypicalapplicationwouldhavethe

expansionlogicalternatedataaccessfromonedevicetothenextinasequential

manner. TheseFIFOsoperateintheDepthExpansionconfigurationwhenthe

followingconditionsaremet:

1. The WEN2/ LD pin is held HIGH during Reset so that this pin

operatesasecondWriteEnable.

2. External logic is used to control the flow of data.

Please see the Application Note" DEPTH EXPANSION OF IDT'S SYN-

CHRONOUSFIFOsUSINGTHERINGCOUNTERAPPROACH"fordetails

ofthisconfiguration.

WIDTH EXPANSION CONFIGURATION

Wordwidthmaybeincreasedsimplybyconnectingthecorrespondinginput

controlssignalsofmultipledevices. Acompositeflagshouldbecreatedforeach

oftheend-pointstatusflags(EFandFF). Thepartialstatusflags(AEandAF)

can be detected from any one device. Figure 15 demonstrates a 18-bit word

widthbyusingtwoIDT72V201/72V211/72V221/72V231/72V241/72V251s.

Any word width can be attained by adding additional IDT72V201/72V211/

72V221/72V231/72V241/72V251s.

When these devices are in a Width Expansion Configuration, the Read

Enable 2 (REN2) control input can be grounded (see Figure 15). In this

configuration,theWriteEnable2/Load(WEN2/LD)pinissetLOWatResetso

thatthepinoperatesasacontroltoloadandreadtheprogrammableflagoffsets.

DEPTH EXPANSION

The IDT72V201/72V211/72V221/72V231/72V241/72V251 can be

adaptedtoapplicationswhentherequirementsareforgreaterthan256/512/

Figure 14. Block Diagram of Single 256 x 9, 512 x 9, 1,024 x 9, 2,048 x 9, 4,096 x 9 and 8,192 x 9 Synchronous FIFO

DATA OUT (Q0 - Q8)

DATA IN (D0 - D8)

RESET (

RS)

READ CLOCK (RCLK)

READ ENABLE 1 (

REN1)

OUTPUT ENABLE (

OE)

EMPTY FLAG (

EF)

PROGRAMMABLE ALMOST-EMPTY (

PAE)

READ ENABLE 2 (

REN2)

WRITE CLOCK (WCLK)

WRITE ENABLE 1 (

WEN1)

WRITE ENABLE 2/LOAD (WEN2/

LD)

FULL FLAG (

FF)

PROGRAMMABLE ALMOST-FULL (

PAF)

IDT

72V201

72V211

72V221

72V231

72V241

72V251

4092 drw16

DATA IN (D)

WRITE CLOCK (WCLK)

18

9

RESET (

RS)

READ CLOCK (RCLK)

DATA OUT (Q)

9

18

READ ENABLE 2 (

REN2)

READ ENABLE 2 (

REN2)

WRITE ENABLE1 (

WEN1)

FULL FLAG (

FF) #1

PROGRAMMABLE (

PAF)

PROGRAMMABLE (

PAE)

EMPTY FLAG (

EF) #2

OUTPUT ENABLE (

OE)

READ ENABLE1 (

REN1)

9

WRITE ENABLE2/LOAD (WEN2/

LD)

FULL FLAG (

FF) #2

EMPTY FLAG (

EF) #1

RESET (

RS)

4092 drw17

IDT

72V201

72V211

72V221

72V231

72V241

72V251

IDT

72V201

72V211

72V221

72V231

72V241

72V251

相关PDF资料 |

PDF描述 |

|---|---|

| MS27656E21B39S | CONN RCPT 39POS WALL MNT W/SCKT |

| IDT72201L15JI8 | IC FIFO 256X9 SYNC 15NS 32-PLCC |

| D38999/20MC98SD | CONN RCPT 10POS WALL MNT W/SCKT |

| IDT72201L10JG8 | IC FIFO 256X9 SYNC 10NS 32-PLCC |

| VE-24B-IU-F1 | CONVERTER MOD DC/DC 95V 200W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72V201L10PF | 功能描述:IC FIFO SYNC 256X9 10NS 32-TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:80 系列:7200 功能:同步 存储容量:18.4K(1K x 18) 数据速率:- 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(10x10) 包装:托盘 其它名称:72225LB10TF |

| IDT72V201L10PF8 | 功能描述:IC FIFO SYNC 256X9 10NS 32-TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:80 系列:7200 功能:同步 存储容量:18.4K(1K x 18) 数据速率:- 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(10x10) 包装:托盘 其它名称:72225LB10TF |

| IDT72V201L10PFG | 功能描述:IC FIFO SYNC 256X9 10NS 32-TQFP RoHS:是 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:80 系列:7200 功能:同步 存储容量:18.4K(1K x 18) 数据速率:- 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(10x10) 包装:托盘 其它名称:72225LB10TF |

| IDT72V201L10PFG8 | 制造商:Integrated Device Technology Inc 功能描述:IC FIFO SYNC 256X9 10NS 32-TQFP |

| IDT72V201L15J | 功能描述:IC FIFO SYNC 256X9 15NS 32-PLCC RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:80 系列:7200 功能:同步 存储容量:18.4K(1K x 18) 数据速率:- 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(10x10) 包装:托盘 其它名称:72225LB10TF |

发布紧急采购,3分钟左右您将得到回复。