- 您现在的位置:买卖IC网 > PDF目录9188 > IDT72V70200PF (IDT, Integrated Device Technology Inc)IC DGTL SW 512X512 3.3V 100-TQFP PDF资料下载

参数资料

| 型号: | IDT72V70200PF |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 6/23页 |

| 文件大小: | 0K |

| 描述: | IC DGTL SW 512X512 3.3V 100-TQFP |

| 标准包装: | 90 |

| 系列: | 72V |

| 类型: | 多路复用器 |

| 电路: | 1 x 16:16 |

| 独立电路: | 1 |

| 电压电源: | 单电源 |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 100-LQFP |

| 供应商设备封装: | 100-TQFP(14x14) |

| 包装: | 托盘 |

| 其它名称: | 72V70200PF |

14

COMMERCIALTEMPERATURERANGE

IDT72V70200 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 512 x 512

JTAG SUPPORT

The IDT72V70200 JTAG interface conforms to the Boundary-Scan stan-

dard IEEE-1149.1. This standard specifies a design-for-testability technique

called Boundary-Scan Test (BST). The operation of the boundary-scan

circuitry is controlled by an external test access port (TAP) Controller.

TEST ACCESS PORT (TAP)

The Test Access Port (TAP) provides access to the test functions of the

IDT72V70200. It consists of three input pins and one output pin.

Test Clock Input (TCK)

TCK provides the clock for the test logic. The TCK does not interfere with

anyon-chipclockandthusremainindependent.TheTCKpermitsshiftingoftest

data into or out of the Boundary-Scan register cells concurrently with the

operation of the device and without interfering with the on-chip logic.

Test Mode Select Input (TMS)

The logic signals received at the TMS input are interpreted by the TAP

Controller to control the test operations. The TMS signals are sampled at the

rising edge of the TCK pulse. This pin is internally pulled to Vcc when it is not

driven from an external source.

Test Data Input (TDI)

Serial input data applied to this port is fed either into the instruction register

or into a test data register, depending on the sequence previously applied to

the TMS input. Both registers are described in a subsequent section. The

received input data is sampled at the rising edge of TCK pulses. This pin is

internally pulled to Vcc when it is not driven from an external source.

Test Data Output (TDO)

Depending on the sequence previously applied to the TMS input, the

contents of either the instruction register or data register are serially shifted out

towards the TDO. The data out of the TDO is clocked on the falling edge of the

TCKpulses.Whennodataisshiftedthroughtheboundaryscancells,theTDO

driver is set to a high impedance state.

Test Reset (

TRST)

Reset the JTAG scan structure. This pin is internally pulled to VCC.

INSTRUCTION REGISTER

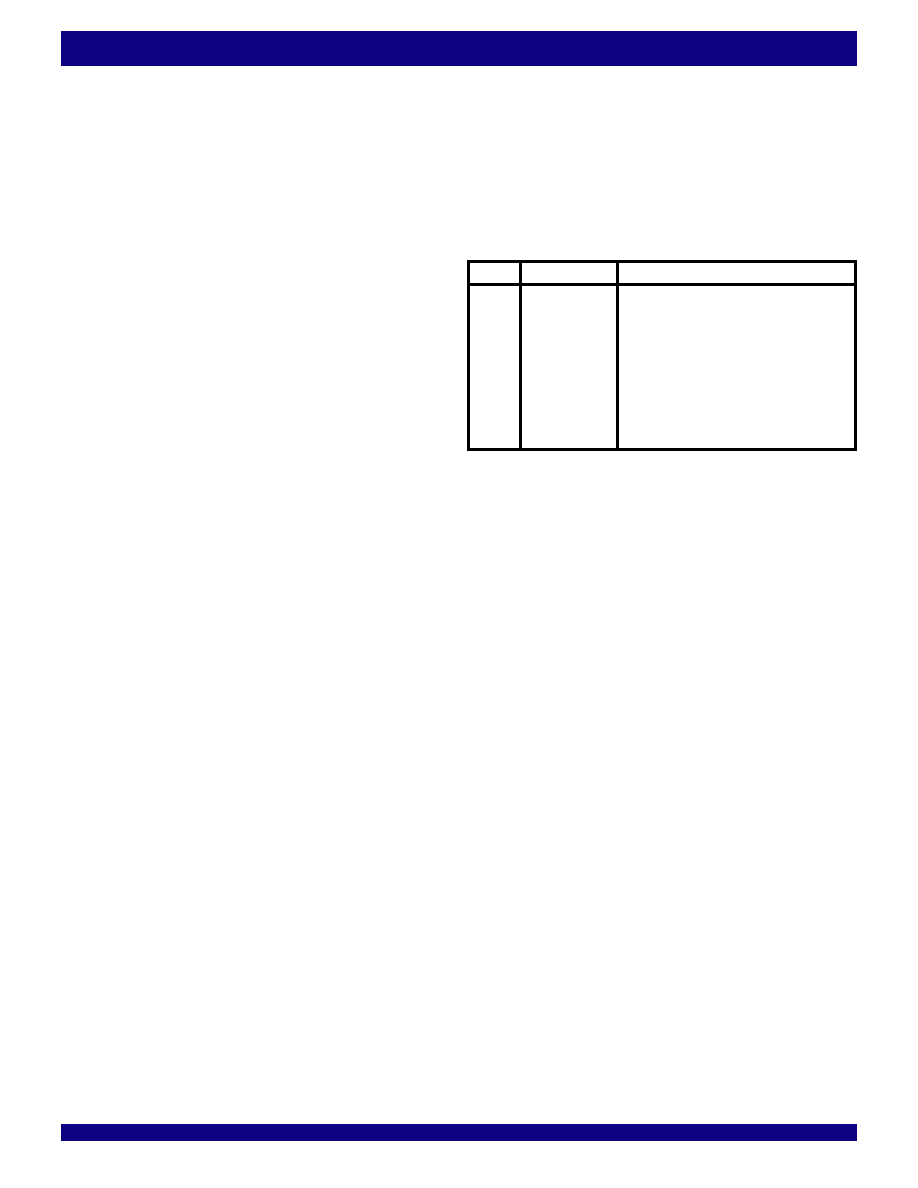

In accordance with the IEEE 1149.1 standard, the IDT72V70200 uses

public instructions. The IDT72V70200 JTAG Interface contains a two-bit

instruction register. Instructions are serially loaded into the instruction register

from the TDI when the TAP Controller is in its shifted-IR state. Subsequently,

theinstructionsaredecodedtoachievetwobasicfunctions:toselectthetestdata

registerthatmayoperatewhiletheinstructioniscurrent,andtodefinetheserial

test data register path, which is used to shift data between TDI and TDO during

data register scanning. See Table below for Instruction decoding.

Value Instruction

Function

000

EXTEST

Select Boundary Scan Register

001

EXTEST

Select Boundary Scan Register

010

Sample/preload

Select Boundary Scan Register

011

Sample/preload

Select Boundary Scan Register

100

Sample/preload

Select Boundary Scan Register

101

Sample/preload

Select Boundary Scan Register

110

Bypass

Select Bypass Register

111

Bypass

Select Bypass Register

JTAG Instruction Register Decoding

TEST DATA REGISTER

AsspecifiedinIEEE1149.1,theIDT72V70200JTAGInterfacecontainstwo

testdataregisters:

The Boundary-Scan register

The Boundary-Scan register consists of a series of Boundary-Scan cells

arranged to form a scan path around the boundary of the IDT72V70200 core

logic.

The Bypass Register

The Bypass register is a single stage shift register that provides a one-bit

path from TDI to its TDO. The IDT72V70200 boundary scan register contains

118 bits. Bit 0 in Table 11 Boundary Scan Register is the first bit clocked out.

All three-state enable bits are active high.

相关PDF资料 |

PDF描述 |

|---|---|

| IDT72V70800TFG | IC DGTL SW 512X512 3.3V 64-STQFP |

| MS3450L22-6SZ | CONN RCPT 3POS WALL MNT W/SCKT |

| IDT72V70800TF | IC DGTL SW 512X512 3.3V 64-STQFP |

| MS3450L22-6SY | CONN RCPT 3POS WALL MNT W/SCKT |

| IDT72V70800PFG8 | IC DGTL SW 512X512 3.3V 64-TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72V70200PF8 | 功能描述:IC DGTL SW 512X512 3.3V 100-TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - 信号开关,多路复用器,解码器 系列:72V 标准包装:48 系列:74VHC 类型:多路复用器 电路:4 x 2:1 独立电路:1 输出电流高,低:8mA,8mA 电压电源:单电源 电源电压:2 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-SOIC(0.154",3.90mm 宽) 供应商设备封装:16-SOIC 包装:管件 |

| IDT72V70200PFG | 功能描述:IC DGTL SW 512X512 3.3V 100-TQFP RoHS:是 类别:集成电路 (IC) >> 逻辑 - 信号开关,多路复用器,解码器 系列:72V 标准包装:48 系列:74VHC 类型:多路复用器 电路:4 x 2:1 独立电路:1 输出电流高,低:8mA,8mA 电压电源:单电源 电源电压:2 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-SOIC(0.154",3.90mm 宽) 供应商设备封装:16-SOIC 包装:管件 |

| IDT72V70200PFG8 | 功能描述:IC DGTL SW 512X512 3.3V 100-TQFP RoHS:是 类别:集成电路 (IC) >> 逻辑 - 信号开关,多路复用器,解码器 系列:72V 标准包装:48 系列:74VHC 类型:多路复用器 电路:4 x 2:1 独立电路:1 输出电流高,低:8mA,8mA 电压电源:单电源 电源电压:2 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-SOIC(0.154",3.90mm 宽) 供应商设备封装:16-SOIC 包装:管件 |

| IDT72V70210DA | 功能描述:IC DGTL SW 1024X1024 144-TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - 信号开关,多路复用器,解码器 系列:72V 标准包装:48 系列:74VHC 类型:多路复用器 电路:4 x 2:1 独立电路:1 输出电流高,低:8mA,8mA 电压电源:单电源 电源电压:2 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-SOIC(0.154",3.90mm 宽) 供应商设备封装:16-SOIC 包装:管件 |

| IDT72V70210DAG | 功能描述:IC DGTL SW 1024X1024 144-TQFP RoHS:是 类别:集成电路 (IC) >> 逻辑 - 信号开关,多路复用器,解码器 系列:72V 标准包装:48 系列:74VHC 类型:多路复用器 电路:4 x 2:1 独立电路:1 输出电流高,低:8mA,8mA 电压电源:单电源 电源电压:2 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-SOIC(0.154",3.90mm 宽) 供应商设备封装:16-SOIC 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。