- 您现在的位置:买卖IC网 > PDF目录9186 > IDT72V71623BCG8 (IDT, Integrated Device Technology Inc)IC DGTL SW 2048X2048 144-BGA PDF资料下载

参数资料

| 型号: | IDT72V71623BCG8 |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 23/28页 |

| 文件大小: | 0K |

| 描述: | IC DGTL SW 2048X2048 144-BGA |

| 标准包装: | 1,000 |

| 系列: | 72V |

| 类型: | 多路复用器 |

| 电路: | 1 x 1:16 |

| 独立电路: | 1 |

| 电压电源: | 单电源 |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 144-LBGA |

| 供应商设备封装: | 144-CABGA(13x13) |

| 包装: | 带卷 (TR) |

| 其它名称: | 72V71623BCG8 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页当前第23页第24页第25页第26页第27页第28页

4

COMMERCIAL TEMPERATURE RANGE

IDT72V71623 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 2,048 x 2,048

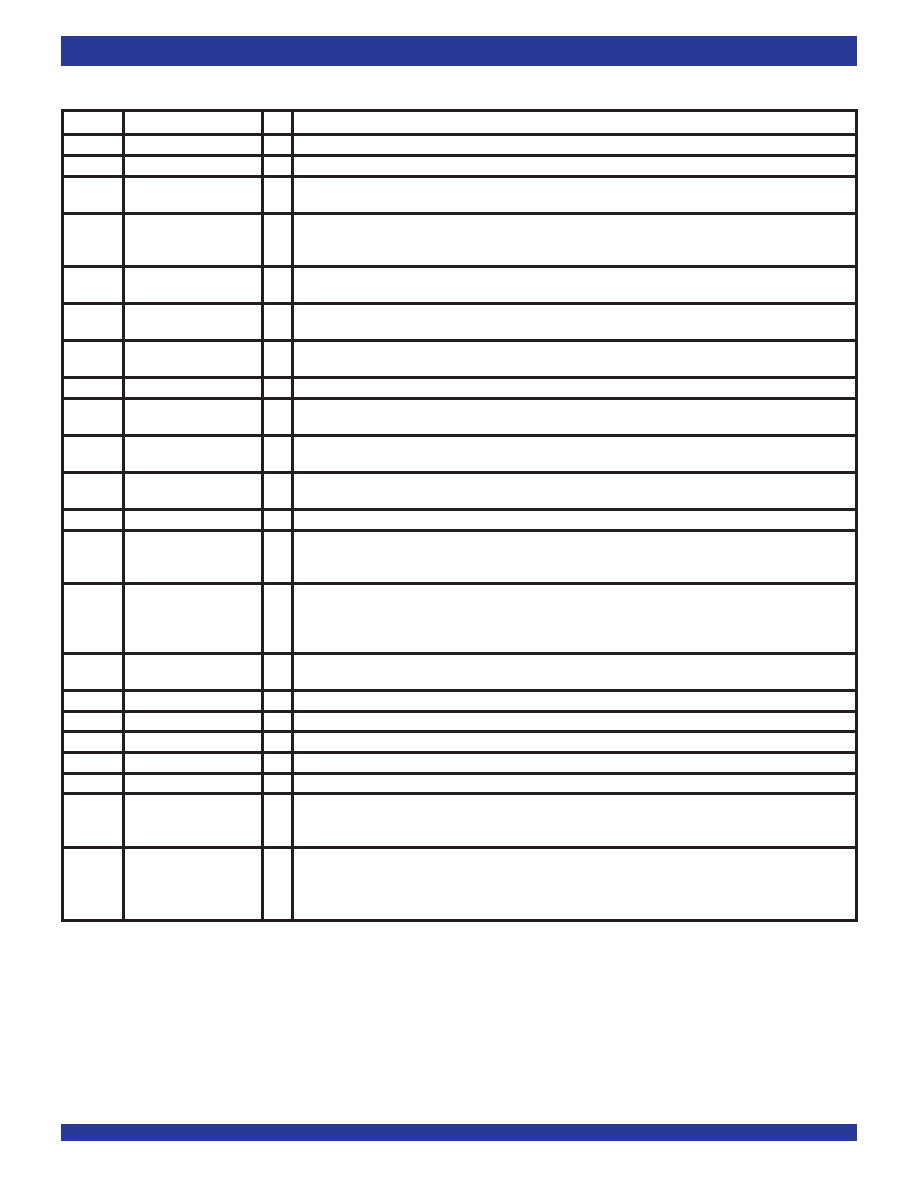

PIN DESCRIPTION

SYMBOL

NAME

I/O

DESCRIPTION

GND

Ground.

Ground Rail.

Vcc

+3.3 Volt Power Supply.

TX0-15

TX Output 0 to 15

O

Serial data output stream. These streams may have a data rate of 2.048 Mb/s, 4.096 Mb/s, 8.192 Mb/s,

(Three-state Outputs)

or 16.384 Mb/s.

OEI0-15

Output Enable

O

These pins reflect the active or three-state status for the corresponding, (TX0-15) output streams.

Indication 0 to 15

(Three-state Outputs)

RX0-15

RX Input 0 to 15

I

Serial data input stream. These streams may have a data rate of 2.048 Mb/s, 4.096 Mb/s, 8.192 Mb/s,

or 16.384 Mb/s.

F0i

Frame Pulse

I

This input accepts and automatically identifies frame synchronization signals formatted according to

ST-BUS and GCI specifications.

FE/HCLK Frame Evaluation/

I

When the WFPS pin is LOW, this pin is the frame measurement input. When the WFPS pin is HIGH, the HCLK

HCLK Clock

(4.096 MHZ clock) is required for frame alignment in the wide frame pulse (WFP) mode.

CLK

Clock

I

Serial clock for shifting data in/out on the serial streams (RX/TX 0-15).

TMS

Test Mode Select

I

JTAG signal that controls the state transitions of the TAP controller. This pin is pulled HIGH by an internal

pull-up when not driven.

TDI

Test Serial Data In

I

JTAG serial test instructions and data are shifted in on this pin. This pin is pulled HIGH by an internal pull-up

when not driven.

TDO

Test Serial Data Out

O

JTAG serial data is output on this pin on the falling edge of TCK. This pin is held in high-impedance state when

JTAG scan is not enabled.

TCK

Test Clock

I

Provides the clock to the JTAG test logic.

TRST

Test Reset

I

Asynchronously initializes the JTAG TAP controller by putting it in the Test-Logic-reset state. This pin is pulled

by an internal pull-up when not driven. This pin should be pulsed LOW on power-up, or held LOW, to ensure

that the IDT72V71623 is in the normal functional mode.

RESET

Device Reset

I

This input (active LOW) puts the IDT72V71623 in its reset state that clears the device internal counters, registers

and brings TX0-15 and microport data outputs to a high-impedance state. In normal operation, the RESET

pin must be held LOW for a minimum of 100ns to reset the device. After reset state, RESET must be held HIGH

for minimum 100ns before beginning operation.

WFPS

Wide Frame Pulse Select

I

When 1, enables the wide frame pulse (WFP) Frame Alignment interface. When 0, the device operates in

ST-BUS /GCI mode.

DS

Data Strobe

I

This active LOW input works in conjunction with CS to enable the read and write operations.

R/W

Read/Write

I

This input controls the direction of the data bus lines during a microprocessor access.

CS

Chip Select

I

Active LOW input used by a microprocessor to activate the microprocessor port of IDT72V71623.

A0-13

Address Bus 0 to 13

I

These pins allow direct access to Connection Memory, Data Memory and internal control registers.

D0-15

Data Bus 0-15

I/O These pins are the data bits of the microprocessor port.

DTA

Data Transfer

O

This active LOW signal indicates that a data bus transfer is complete. When the bus cycle ends, this pin drives

Acknowledgment

HIGH and then goes high-impedance, allowing for faster bus cycles with a weaker pull-up resistor. A pull-up

resistor is required to hold a HIGH level when the pin is in high-impedance.

ODE

Output Drive Enable

I

This is the output enable control for the TX0-15 serial outputs. When ODE input is LOW and the OSB bit of

the IMS register is LOW, TX0-15 are in a high-impedance state. If this input is HIGH, the TX0-15 output

drivers are enabled. However, each channel may still be put into a high-impedance state by using the per

channel control bit in the Connection Memory.

相关PDF资料 |

PDF描述 |

|---|---|

| V28A6V5H200B | CONVERTER MOD DC/DC 6.5V 200W |

| IDT72V71623BC8 | IC DGTL SW 2048X2048 144-BGA |

| VI-BWY-MY-F3 | CONVERTER MOD DC/DC 3.3V 33W |

| V28A8H200BG3 | CONVERTER MOD DC/DC 8V 200W |

| IDT72V90823PF | IC DGTL SW 2048X2048 100-TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72V71623DA | 功能描述:IC DGTL SW 2048X2048 144-TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - 信号开关,多路复用器,解码器 系列:72V 标准包装:48 系列:74VHC 类型:多路复用器 电路:4 x 2:1 独立电路:1 输出电流高,低:8mA,8mA 电压电源:单电源 电源电压:2 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-SOIC(0.154",3.90mm 宽) 供应商设备封装:16-SOIC 包装:管件 |

| IDT72V71623DAG | 功能描述:IC DGTL SW 2048X2048 144-TQFP RoHS:是 类别:集成电路 (IC) >> 逻辑 - 信号开关,多路复用器,解码器 系列:72V 标准包装:48 系列:74VHC 类型:多路复用器 电路:4 x 2:1 独立电路:1 输出电流高,低:8mA,8mA 电压电源:单电源 电源电压:2 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-SOIC(0.154",3.90mm 宽) 供应商设备封装:16-SOIC 包装:管件 |

| IDT72V71643BC | 功能描述:IC DGTL SW 4096X4096 144-BGA RoHS:否 类别:集成电路 (IC) >> 逻辑 - 信号开关,多路复用器,解码器 系列:72V 标准包装:48 系列:74VHC 类型:多路复用器 电路:4 x 2:1 独立电路:1 输出电流高,低:8mA,8mA 电压电源:单电源 电源电压:2 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-SOIC(0.154",3.90mm 宽) 供应商设备封装:16-SOIC 包装:管件 |

| IDT72V71643BC8 | 功能描述:IC DGTL SW 4096X4096 144-BGA RoHS:否 类别:集成电路 (IC) >> 逻辑 - 信号开关,多路复用器,解码器 系列:72V 标准包装:48 系列:74VHC 类型:多路复用器 电路:4 x 2:1 独立电路:1 输出电流高,低:8mA,8mA 电压电源:单电源 电源电压:2 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-SOIC(0.154",3.90mm 宽) 供应商设备封装:16-SOIC 包装:管件 |

| IDT72V71643BCG | 功能描述:IC DGTL SW 4096X4096 144-BGA RoHS:是 类别:集成电路 (IC) >> 逻辑 - 信号开关,多路复用器,解码器 系列:72V 标准包装:48 系列:74VHC 类型:多路复用器 电路:4 x 2:1 独立电路:1 输出电流高,低:8mA,8mA 电压电源:单电源 电源电压:2 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-SOIC(0.154",3.90mm 宽) 供应商设备封装:16-SOIC 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。