- 您现在的位置:买卖IC网 > PDF目录10006 > IDT72V811L10TFG (IDT, Integrated Device Technology Inc)IC FIFO 512X9 SYNC DUAL 64TQFP PDF资料下载

参数资料

| 型号: | IDT72V811L10TFG |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 14/16页 |

| 文件大小: | 0K |

| 描述: | IC FIFO 512X9 SYNC DUAL 64TQFP |

| 标准包装: | 80 |

| 系列: | 72V |

| 功能: | 异步 |

| 存储容量: | 4.6K(512 x 9) |

| 数据速率: | 100MHz |

| 访问时间: | 10ns |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-LQFP |

| 供应商设备封装: | 64-TQFP(10x10) |

| 包装: | 托盘 |

7

IDT72V801/72V8211/72V821/72V831/72V841/72V851 3.3V DUAL CMOS SyncFIFOTM

DUAL 256 x 9, DUAL 512 x 9, DUAL 1K x 9, DUAL 2K x 9, DUAL 4K x 9, DUAL 8K x 9

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

OCTOBER 22, 2008

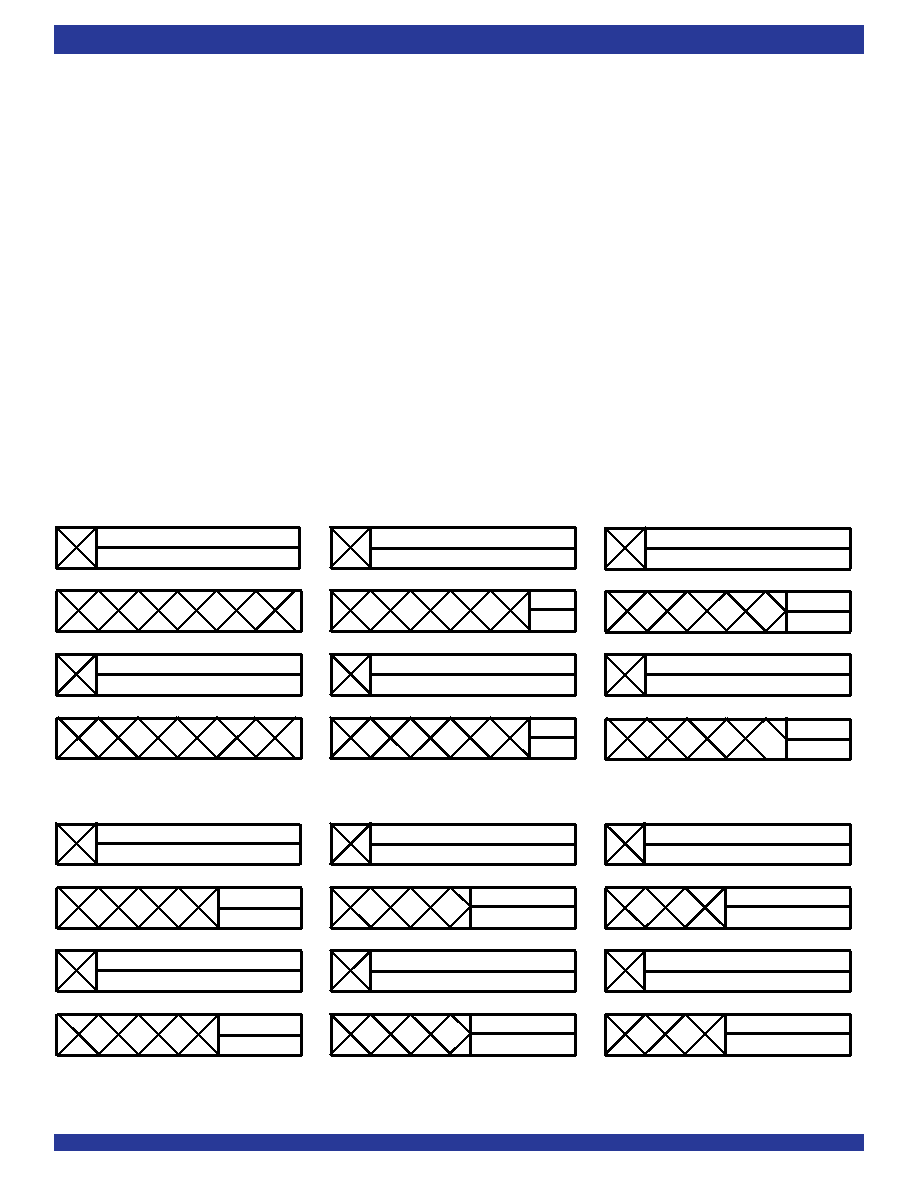

Figure 3. Offset Register Formats and Default Values for the A and B FIFOs

contains four 8-bit offset registers which can be loaded with data on the inputs,

or read on the outputs. See Figure 3 for details of the size of the registers and

the default values.

If FIFO A (B) is configured to have programmable flags, when the

WENA1

(

WENB1) and WENA2/LDA(WENB2/LDB) are set LOW, data on the DA (DB)

inputsarewrittenintotheEmpty(LeastSignificantBit)Offsetregisteronthefirst

LOW-to-HIGH transition of the WCLKA (WCLKB). Data are written into the

Empty (Most Significant Bit) Offset register on the second LOW-to-HIGH

transitionofWCLKA(WCLKB),intotheFull(LeastSignificantBit)Offsetregister

on the third transition, and into the Full (Most Significant Bit) Offset register on

thefourthtransition. ThefifthtransitionofWCLKA(WCLKB)againwritestothe

Empty (Least Significant Bit) Offset register.

87

0

Empty Offset (LSB) Reg.

Default Value 007H

80

Full Offset (LSB) Reg.

Default Value 007H

7

80

Empty Offset (LSB)

Default Value 007H

80

Full Offset (LSB)

Default Value 007H

72V801 - 256 x 9 x 2

72V811 - 512 x 9 x 2

7

80

(MSB)

1

0

87

0

Empty Offset (LSB) Reg.

Default Value 007H

80

Full Offset (LSB) Reg.

Default Value 007H

7

80

Empty Offset (LSB)

Default Value 007H

80

Full Offset (LSB)

Default Value 007H

72V831 - 2,048 x 9 x 2

7

80

(MSB)

0000

2

(MSB)

000

3

80

(MSB)

0000

2

(MSB)

000

3

80

8

0

80

(MSB)

1

0

87

0

Empty Offset (LSB) Reg.

Default Value 007H

80

Full Offset (LSB) Reg.

Default Value 007H

7

72V821 - 1,024 x 9 x 2

80

(MSB)

00

1

80

(MSB)

00

1

4093 drw 05

72V841 - 4,096 x 9 x 2

80

Empty Offset (LSB)

Default Value 007H

80

Full Offset (LSB)

Default Value 007H

7

80

(MSB)

00000

4

72V851 - 8,192 x 9 x 2

(MSB)

00000

80

4

However,writingalloffsetregistersdoesnothavetooccuratonetime. One

or two offset registers can be written and then by bringing

LDA(LDB) HIGH,

FIFO A (B) is returned to normal read/write operation. When

LDA(LDB) is set

LOW, and

WENA1 (WENB1) is LOW, the next offset register in sequence is

written.

ThecontentsoftheoffsetregisterscanbereadontheQA(QB)outputswhen

WENA2/

LDA (WENB2/LDB) is set LOW and both Read Enables RENA1,

RENA2(RENB1,RENB2)aresetLOW. DatacanbereadontheLOW-to-HIGH

transition of the Read Clock RCLKA (RCLKB).

A read and write should not be performed simultaneously to the offset

registers.

相关PDF资料 |

PDF描述 |

|---|---|

| GTC030-28-21P | CONN RCPT 37POS PANEL MNT W/PINS |

| IDT72220L10TP | IC FIFO 1024X8 SYNC 10NS 28-DIP |

| IDT72605L50PF | IC FIFO BI SYNC 256X18 64-TQFP |

| IDT7207L20J | IC FIFO 16384X18 20NS 32PLCC |

| IDT72V3640L6PF8 | IC FIFO SS 1024X36 6NS 128-TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72V811L10TFG8 | 制造商:Integrated Device Technology Inc 功能描述:IC FIFO SYNC 512X9 10NS 64QFP |

| IDT72V811L15PF | 功能描述:IC FIFO SYNC 512X9 15NS 64QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V811L15PF8 | 功能描述:IC FIFO SYNC 512X9 15NS 64QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V811L15PFGI | 制造商:Integrated Device Technology Inc 功能描述:IC FIFO SYNC 512X9 15NS 64QFP |

| IDT72V811L15PFI | 功能描述:IC FIFO SYNC 512X9 15NS 64QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

发布紧急采购,3分钟左右您将得到回复。