- 您现在的位置:买卖IC网 > PDF目录8240 > IDT74ALVCF162835APA8 (IDT, Integrated Device Technology Inc)IC UNIV BUS DVR 18BIT 56TSSOP PDF资料下载

参数资料

| 型号: | IDT74ALVCF162835APA8 |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 5/6页 |

| 文件大小: | 0K |

| 描述: | IC UNIV BUS DVR 18BIT 56TSSOP |

| 标准包装: | 2,000 |

| 系列: | 74ALVCF |

| 逻辑类型: | 通用总线驱动器,CMOS |

| 电路数: | 18 位 |

| 输出电流高,低: | 18mA,18mA |

| 电源电压: | 2.3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 56-TFSOP(0.240",6.10mm 宽) |

| 供应商设备封装: | 56-TSSOP |

| 包装: | 带卷 (TR) |

| 其它名称: | 74ALVCF162835APA8 |

INDUSTRIALTEMPERATURERANGE

IDT74ALVCF162835A

3.3V CMOS 18-BIT UNIVERSAL BUS DRIVER WITH 3-STATE OUTPUTS

5

Open

VLOAD

GND

VCC

Pulse

Generator

D.U.T.

500

Ω

500

Ω

CL

RT

VIN

VOUT

(1, 2)

ALVC Link

INPUT

VIH

0V

VOH

VOL

tPLH1

tSK (x)

OUTPUT 1

OUTPUT 2

tPHL1

tSK (x)

tPLH2

tPHL2

VT

VOH

VT

VOL

tSK(x) = tPLH2 - tPLH1 or tPHL2 - tPHL1

ALVC Link

SAME PHASE

INPUT TRANSITION

OPPOSITE PHASE

INPUT TRANSITION

0V

VOH

VOL

tPLH

tPHL

tPLH

OUTPUT

VIH

VT

VIH

VT

ALVC Link

DATA

INPUT

0V

tREM

TIMING

INPUT

SYNCHRONOUS

CONTROL

tSU

tH

tSU

tH

VIH

VT

VIH

VT

VIH

VT

VIH

VT

ALVC Link

ASYNCHRONOUS

CONTROL

LOW-HIGH-LOW

PULSE

HIGH-LOW-HIGH

PULSE

VT

tW

VT

ALVC Link

CONTROL

INPUT

tPLZ

0V

OUTPUT

NORMALLY

LOW

tPZH

0V

SWITCH

CLOSED

OUTPUT

NORMALLY

HIGH

ENABLE

DISABLE

SWITCH

OPEN

tPHZ

0V

VOL + VLZ

VOH

VT

tPZL

VLOAD/2

VIH

VT

VOL

VOH - VHZ

ALVC Link

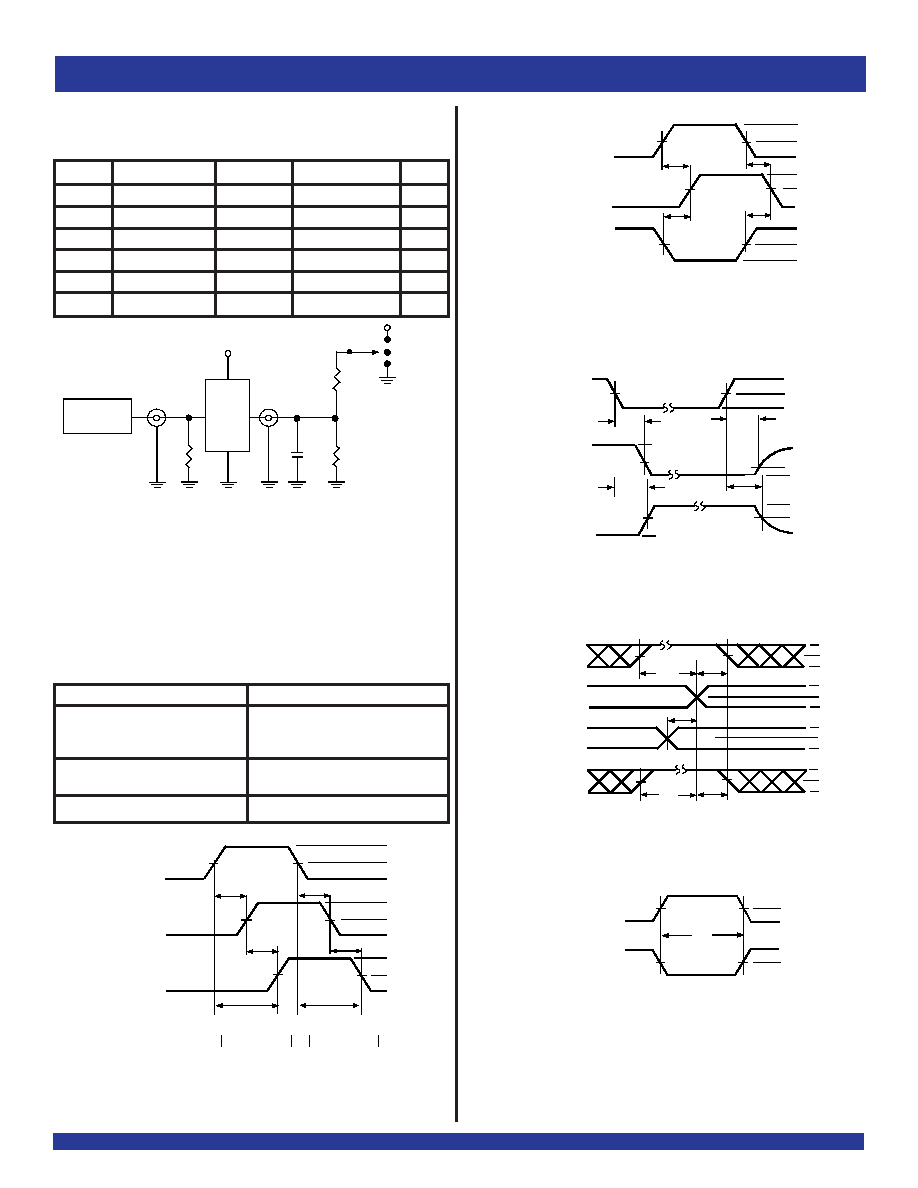

TEST CIRCUITS AND WAVEFORMS

Propagation Delay

Test Circuit for All Outputs

Enable and Disable Times

Set-up, Hold, and Release Times

NOTES:

1.

For tSK(o) OUTPUT1 and OUTPUT2 are any two outputs.

2.

For tSK(b) OUTPUT1 and OUTPUT2 are in the same bank.

DEFINITIONS:

CL = Load capacitance: includes jig and probe capacitance.

RT = Termination resistance: should be equal to ZOUT of the Pulse Generator.

NOTES:

1. Pulse Generator for All Pulses: Rate

≤ 1.0MHz; tF ≤ 2.5ns; tR ≤ 2.5ns.

2. Pulse Generator for All Pulses: Rate

≤ 1.0MHz; tF ≤ 2ns; tR ≤ 2ns.

Output Skew - tSK(X)

Pulse Width

NOTE:

1. Diagram shown for input Control Enable-LOW and input Control Disable-HIGH.

Symbol

VCC

(1)= 3.3V±0.3V VCC(1)=2.7V

VCC

(2)= 2.5V±0.2V

Unit

VLOAD

6

2 x Vcc

V

VIH

2.7

Vcc

V

VT

1.5

Vcc / 2

V

VLZ

300

150

mV

VHZ

300

150

mV

CL

50

30

pF

TEST CONDITIONS

SWITCH POSITION

Test

Switch

Open Drain

Disable Low

VLOAD

Enable Low

Disable High

GND

Enable High

All Other Tests

Open

相关PDF资料 |

PDF描述 |

|---|---|

| 20020010-D061B01LF | TERM BLK PLUG 6 POS 3.81MM |

| 691363110003 | TERM BLOCK PLUG 3POS R/A 3.5MM |

| CD4072BNSRE4 | IC DUAL 4INPUT OR GATE 14-SOP |

| CD4071BNSRE4 | IC QUAD 2INPUT OR GATE 14-SOP |

| OSTTJ0631530 | TERM BLOCK PLUG 3.81MM 6POS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT74ALVCF162835APAG | 功能描述:IC UNIV BUS DVR 18BIT 56TSSOP RoHS:是 类别:集成电路 (IC) >> 逻辑 - 通用总线函数 系列:74ALVCF 产品变化通告:Product Discontinuation 09/Dec/2010 标准包装:1,500 系列:74AVC 逻辑类型:通用总线驱动器 输入数:- 电路数:18 位 输出电流高,低:12mA,12mA 电源电压:1.65 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:56-TFSOP(0.240",6.10mm 宽) 供应商设备封装:56-TSSOP 包装:带卷 (TR) |

| IDT74ALVCF162835APAG8 | 功能描述:IC UNIV BUS DVR 18BIT 56TSSOP RoHS:是 类别:集成电路 (IC) >> 逻辑 - 通用总线函数 系列:74ALVCF 产品变化通告:Product Discontinuation 09/Dec/2010 标准包装:1,500 系列:74AVC 逻辑类型:通用总线驱动器 输入数:- 电路数:18 位 输出电流高,低:12mA,12mA 电源电压:1.65 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:56-TFSOP(0.240",6.10mm 宽) 供应商设备封装:56-TSSOP 包装:带卷 (TR) |

| IDT74ALVCF162835APF | 功能描述:IC UNIV BUS DVR 18BIT 56TVSOP RoHS:否 类别:集成电路 (IC) >> 逻辑 - 通用总线函数 系列:74ALVCF 产品变化通告:Product Discontinuation 09/Dec/2010 标准包装:1,500 系列:74AVC 逻辑类型:通用总线驱动器 输入数:- 电路数:18 位 输出电流高,低:12mA,12mA 电源电压:1.65 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:56-TFSOP(0.240",6.10mm 宽) 供应商设备封装:56-TSSOP 包装:带卷 (TR) |

| IDT74ALVCF162835APF8 | 功能描述:IC UNIV BUS DVR 18BIT 56TVSOP RoHS:否 类别:集成电路 (IC) >> 逻辑 - 通用总线函数 系列:74ALVCF 产品变化通告:Product Discontinuation 09/Dec/2010 标准包装:1,500 系列:74AVC 逻辑类型:通用总线驱动器 输入数:- 电路数:18 位 输出电流高,低:12mA,12mA 电源电压:1.65 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:56-TFSOP(0.240",6.10mm 宽) 供应商设备封装:56-TSSOP 包装:带卷 (TR) |

| IDT74ALVCF162835APFG | 功能描述:IC UNIV BUS DVR 18BIT 56TVSOP RoHS:是 类别:集成电路 (IC) >> 逻辑 - 通用总线函数 系列:74ALVCF 产品变化通告:Product Discontinuation 09/Dec/2010 标准包装:1,500 系列:74AVC 逻辑类型:通用总线驱动器 输入数:- 电路数:18 位 输出电流高,低:12mA,12mA 电源电压:1.65 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:56-TFSOP(0.240",6.10mm 宽) 供应商设备封装:56-TSSOP 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。