- 您现在的位置:买卖IC网 > PDF目录175819 > IDT74LVCH162721APV8 (INTEGRATED DEVICE TECHNOLOGY INC) LVC/LCX/Z SERIES, 20-BIT DRIVER, TRUE OUTPUT, PDSO56 PDF资料下载

参数资料

| 型号: | IDT74LVCH162721APV8 |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 总线收发器 |

| 英文描述: | LVC/LCX/Z SERIES, 20-BIT DRIVER, TRUE OUTPUT, PDSO56 |

| 封装: | SSOP-56 |

| 文件页数: | 1/6页 |

| 文件大小: | 65K |

| 代理商: | IDT74LVCH162721APV8 |

INDUSTRIALTEMPERATURERANGE

IDT74LVCH162721A

3.3V CMOS 20-BIT FLIP-FLOP WITH 3-STATE OUTPUTS

1

OCTOBER 1999

INDUSTRIAL TEMPERATURE RANGE

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

1999 Integrated Device Technology, Inc.

DSC-4940/1

FEATURES:

Typical tSK(o) (Output Skew) < 250ps

ESD > 2000V per MIL-STD-883, Method 3015; > 200V using

machine model (C = 200pF, R = 0)

VCC = 3.3V ± 0.3V, Normal Range

VCC = 2.7V to 3.6V, Extended Range

CMOS power levels (0.4

W typ. static)

All inputs, outputs, and I/O are 5V tolerant

Supports hot insertion

Available in SSOP, TSSOP, and TVSOP packages

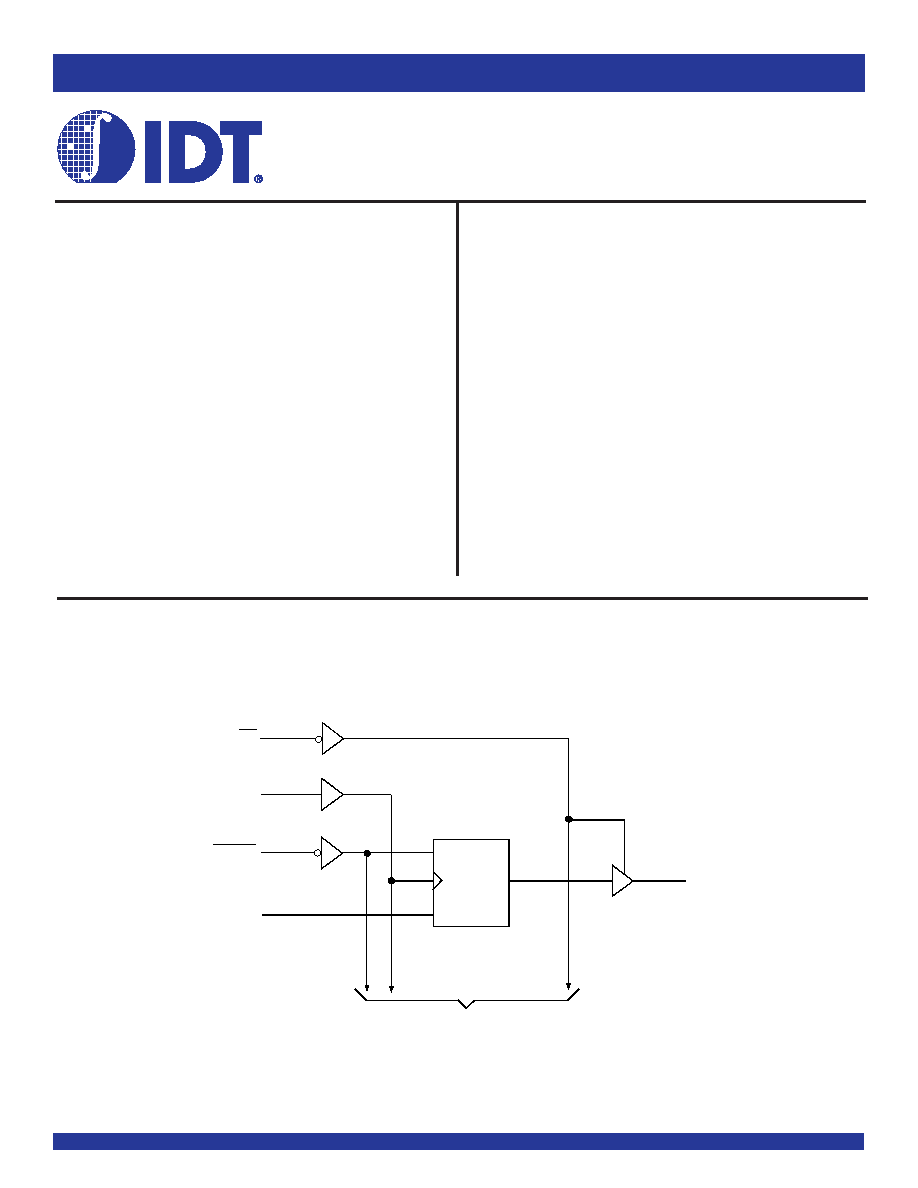

FUNCTIONAL BLOCK DIAGRAM

DRIVE FEATURES:

Balanced Output Drivers: ±12mA

Low switching noise

APPLICATIONS:

5V and 3.3V mixed voltage systems

Data communication and telecommunication systems

IDT74LVCH162721A

DESCRIPTION:

This 20-bit flip-flop is built using advanced dual metal CMOS technology.

The 20 flip-flops of the LVCH162721A are edge-triggered D-type flip-flops

with qualified clock storage. On the positive transition of the clock (CLK)

input, the device provides true data at the Q outputs if the clock-enable

(CLKEN) input is low. If CLKEN is high, no data is stored.

A buffered output-enable (OE) input places the 20 outputs in either a

normal logic state (high or low) or a high-impedance state. In the high-

impedancestate,theoutputsneitherloadnordrivethebuslinessignificantly.

The high-impedance state and increased drive provide the capability to

drivebuslineswithouttheneedforinterfaceorpullupcomponents. OEdoes

not affect the internal operation of the flip-flops. Old data can be retained or

new data can be entered while the outputs are in the high-impedance state.

The LVCH162721A has series resistors in the device output structure

which will significantly reduce line noise when used with light loads. This

driver has been designed to drive ±12mA at the designated threshold

levels.

The LVCH162721A has “bus-hold” which retains the inputs’ last state

whenever the input goes to a high impedance. This prevents floating inputs

and eliminates the need for pull-up/down resistors.

3.3V CMOS 20-BIT

FLIP-FLOP WITH 3-STATE

OUTPUTS, 5 VOLT TOLERANT I/O

AND BUS-HOLD

CLK

OE

CLKEN

D1

1

56

29

55

CE

C1

1D

2

Q1

To 19 O ther Channels

相关PDF资料 |

PDF描述 |

|---|---|

| IDT74LVCH162721APV | LVC/LCX/Z SERIES, 20-BIT DRIVER, TRUE OUTPUT, PDSO56 |

| IDT75C18S100D | Video DAC without Color Palette |

| IDT75C18S100DB | Video DAC without Color Palette |

| IDT75C18S100L | Video DAC without Color Palette |

| IDT75C18S100LB | Video DAC without Color Palette |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT74LVCH16373APAG | 功能描述:IC TRANSP LATCH 16BIT D 48-TSSOP RoHS:是 类别:集成电路 (IC) >> 逻辑 - 锁销 系列:74LVCH 标准包装:48 系列:74VHCT 逻辑类型:D 型,可寻址 电路:1:8 输出类型:标准 电源电压:4.5 V ~ 5.5 V 独立电路:1 延迟时间 - 传输:6ns 输出电流高,低:8mA,8mA 工作温度:-55°C ~ 125°C 安装类型:表面贴装 封装/外壳:16-SOIC(0.154",3.90mm 宽) 供应商设备封装:16-SOIC 包装:管件 |

| IDT74LVCH16373APAG8 | 功能描述:IC TRANSP LATCH 16BIT D 48-TSSOP RoHS:是 类别:集成电路 (IC) >> 逻辑 - 锁销 系列:74LVCH 标准包装:48 系列:74VHCT 逻辑类型:D 型,可寻址 电路:1:8 输出类型:标准 电源电压:4.5 V ~ 5.5 V 独立电路:1 延迟时间 - 传输:6ns 输出电流高,低:8mA,8mA 工作温度:-55°C ~ 125°C 安装类型:表面贴装 封装/外壳:16-SOIC(0.154",3.90mm 宽) 供应商设备封装:16-SOIC 包装:管件 |

| IDT74LVCH16374APAG | 功能描述:IC FLIP FLOP 16BIT D 3ST 48TSSOP RoHS:是 类别:集成电路 (IC) >> 逻辑 - 触发器 系列:74LVCH 标准包装:1 系列:74AC 功能:设置(预设)和复位 类型:D 型 输出类型:差分 元件数:2 每个元件的位元数:1 频率 - 时钟:160MHz 延迟时间 - 传输:6ns 触发器类型:正边沿 输出电流高,低:24mA,24mA 电源电压:2 V ~ 6 V 工作温度:-55°C ~ 125°C 安装类型:表面贴装 封装/外壳:14-SOIC(0.154",3.90mm 宽) 包装:Digi-Reel® 产品目录页面:928 (CN2011-ZH PDF) 其它名称:296-18123-6 |

| IDT74LVCH16374APAG8 | 功能描述:IC FLIP FLOP 16BIT D 3ST 48TSSOP RoHS:是 类别:集成电路 (IC) >> 逻辑 - 触发器 系列:74LVCH 标准包装:1 系列:74LVX 功能:主复位 类型:D 型总线 输出类型:非反相 元件数:1 每个元件的位元数:8 频率 - 时钟:150MHz 延迟时间 - 传输:7.1ns 触发器类型:正边沿 输出电流高,低:4mA,4mA 电源电压:2 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:20-TSSOP(0.173",4.40mm 宽) 包装:Digi-Reel® 其它名称:74LVX273MTCXDKR |

| IDT74LVCH16374APV | 制造商:Integrated Device Technology Inc 功能描述:74LVCH SMD 74LVCH16374 SSOP48 |

发布紧急采购,3分钟左右您将得到回复。