- 您现在的位置:买卖IC网 > PDF目录67122 > IDT74LVCH16276APV8 (INTEGRATED DEVICE TECHNOLOGY INC) LVC/LCX/Z SERIES, 12-BIT EXCHANGER, TRUE OUTPUT, PDSO56 PDF资料下载

参数资料

| 型号: | IDT74LVCH16276APV8 |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 总线收发器 |

| 英文描述: | LVC/LCX/Z SERIES, 12-BIT EXCHANGER, TRUE OUTPUT, PDSO56 |

| 封装: | SSOP-56 |

| 文件页数: | 3/8页 |

| 文件大小: | 72K |

| 代理商: | IDT74LVCH16276APV8 |

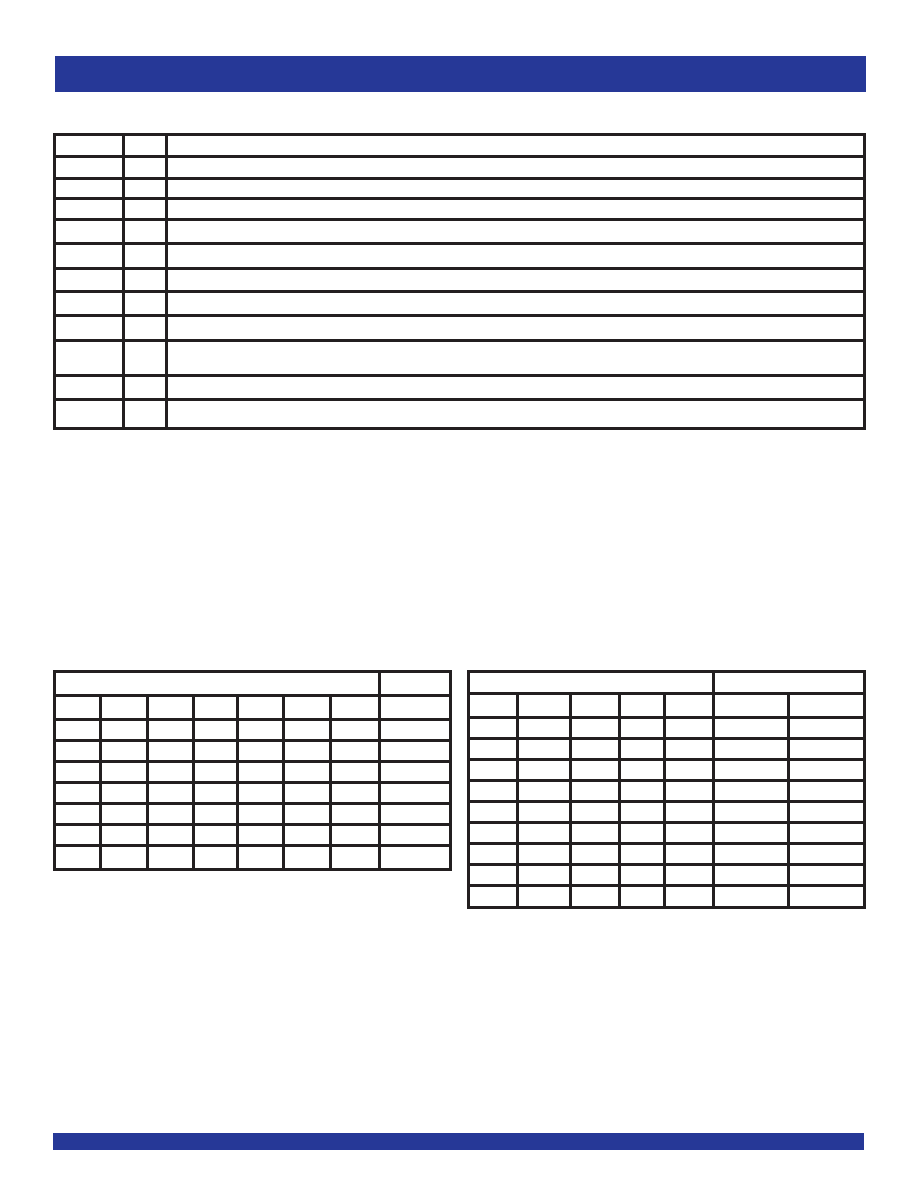

INDUSTRIALTEMPERATURERANGE

IDT74LVCH16276A

3.3VCMOS12-BITSYNCHRONOUSBUSEXCHANGER

3

Inputs

Outputs

Ax

CEA1B CEA2B

OEB

CLK

1Bx

2Bx

HLL

L

↑

HH

LL

L

↑

LL

HL

H

L

↑

HB(2)

LL

H

L

↑

LB(2)

HH

L

↑

B(2)

H

LH

L

↑

B(2)

L

XH

H

L

↑

B(2)

XX

X

H

↑

ZZ

XX

X

L

↑

Active

FUNCTION TABLES(1)

Inputs

Outputs

1Bx

2Bx

SEL

CE1B CE2B

OEA

CLK

Ax

HX

H

L

X

L

↑

H

LX

H

L

X

L

↑

L

XX

H

X

L

↑

A(2)

XH

L

X

L

↑

H

XL

L

X

L

↑

L

XX

L

X

H

L

↑

A(2)

X

XXX

H

↑

Z

NOTES:

1. H = HIGH Voltage Level

L = LOW Voltage Level

X = Don’t Care

Z = High-Impedance

↑ = LOW-to-HIGH Transition

2. A, B = Output level before the indicated steady-state input conditions were

established.

PIN DESCRIPTION

Signal

I/O

Description

A(1:12)

I/O

Bidirectional Data Port A. Usually connected to the CPU’s Address/Data bus.(1)

1B(1:12)

I/O

Bidirectional Data Port 1B. Usually connected to the even path or even bank of memory.(1)

2B(1:12)

I/O

Bidirectional Data Port 2B. Usually connected to the odd path or odd bank of memory.(1)

CLK

I

Clock Input.

CEA1B

I

Clock Enable Input for the A-1B Register. If CEA1B is LOW during the rising edge of CLK, data will be clocked into register A-1B (Active LOW).

CEA2B

I

Clock Enable Input for the A-2B Register. If CEA2B is LOW during the rising edge of CLK, data will be clocked into register A-2B (Active LOW).

CE1B

I

Clock Enable Input for the 1B-A Register. If CE1B is LOW during the rising edge of CLK, data will be clocked into register 1B-A (Active LOW).

CE2B

I

Clock Enable Input for the 2B-A Register. If CE2B is LOW during the rising edge of CLK, data will be clocked into register 2B-A (Active LOW).

SEL

I

1B or 2B Part Selection. When HIGH during the rising edge of CLK, SEL enables data transfer from 1B Port to A Port. When LOW during the rising

edge of CLK, SEL enables data transfer from 2B Port to A Port.

OEA

I

Synchronous Output Enable for A Port (Active LOW).

OEB

I

Synchronous Output Enable for 1B Port and 2B Port (Active LOW).

NOTE:

1. These pins have “Bus-hold”. All other pins are standard inputs, outputs, or I/Os.

相关PDF资料 |

PDF描述 |

|---|---|

| IDT74LVCH16374APA8 | LVC/LCX/Z SERIES, DUAL 8-BIT DRIVER, TRUE OUTPUT, PDSO48 |

| IDT74LVCH16374APAG8 | LVC/LCX/Z SERIES, DUAL 8-BIT DRIVER, TRUE OUTPUT, PDSO48 |

| IDT74LVCH16501APV | LVC/LCX/Z SERIES, 18-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PDSO56 |

| IDT74LVCH16601APA | LVC/LCX/Z SERIES, 18-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PDSO56 |

| IDT74LVCH16601APF | LVC/LCX/Z SERIES, 18-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PDSO56 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT74LVCH16373APAG | 功能描述:IC TRANSP LATCH 16BIT D 48-TSSOP RoHS:是 类别:集成电路 (IC) >> 逻辑 - 锁销 系列:74LVCH 标准包装:48 系列:74VHCT 逻辑类型:D 型,可寻址 电路:1:8 输出类型:标准 电源电压:4.5 V ~ 5.5 V 独立电路:1 延迟时间 - 传输:6ns 输出电流高,低:8mA,8mA 工作温度:-55°C ~ 125°C 安装类型:表面贴装 封装/外壳:16-SOIC(0.154",3.90mm 宽) 供应商设备封装:16-SOIC 包装:管件 |

| IDT74LVCH16373APAG8 | 功能描述:IC TRANSP LATCH 16BIT D 48-TSSOP RoHS:是 类别:集成电路 (IC) >> 逻辑 - 锁销 系列:74LVCH 标准包装:48 系列:74VHCT 逻辑类型:D 型,可寻址 电路:1:8 输出类型:标准 电源电压:4.5 V ~ 5.5 V 独立电路:1 延迟时间 - 传输:6ns 输出电流高,低:8mA,8mA 工作温度:-55°C ~ 125°C 安装类型:表面贴装 封装/外壳:16-SOIC(0.154",3.90mm 宽) 供应商设备封装:16-SOIC 包装:管件 |

| IDT74LVCH16374APAG | 功能描述:IC FLIP FLOP 16BIT D 3ST 48TSSOP RoHS:是 类别:集成电路 (IC) >> 逻辑 - 触发器 系列:74LVCH 标准包装:1 系列:74AC 功能:设置(预设)和复位 类型:D 型 输出类型:差分 元件数:2 每个元件的位元数:1 频率 - 时钟:160MHz 延迟时间 - 传输:6ns 触发器类型:正边沿 输出电流高,低:24mA,24mA 电源电压:2 V ~ 6 V 工作温度:-55°C ~ 125°C 安装类型:表面贴装 封装/外壳:14-SOIC(0.154",3.90mm 宽) 包装:Digi-Reel® 产品目录页面:928 (CN2011-ZH PDF) 其它名称:296-18123-6 |

| IDT74LVCH16374APAG8 | 功能描述:IC FLIP FLOP 16BIT D 3ST 48TSSOP RoHS:是 类别:集成电路 (IC) >> 逻辑 - 触发器 系列:74LVCH 标准包装:1 系列:74LVX 功能:主复位 类型:D 型总线 输出类型:非反相 元件数:1 每个元件的位元数:8 频率 - 时钟:150MHz 延迟时间 - 传输:7.1ns 触发器类型:正边沿 输出电流高,低:4mA,4mA 电源电压:2 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:20-TSSOP(0.173",4.40mm 宽) 包装:Digi-Reel® 其它名称:74LVX273MTCXDKR |

| IDT74LVCH16374APV | 制造商:Integrated Device Technology Inc 功能描述:74LVCH SMD 74LVCH16374 SSOP48 |

发布紧急采购,3分钟左右您将得到回复。