- 您现在的位置:买卖IC网 > PDF目录65593 > IDT74LVCHR16501APV (INTEGRATED DEVICE TECHNOLOGY INC) LVC/LCX/Z SERIES, 18-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PDSO56 PDF资料下载

参数资料

| 型号: | IDT74LVCHR16501APV |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 总线收发器 |

| 英文描述: | LVC/LCX/Z SERIES, 18-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PDSO56 |

| 封装: | SSOP-56 |

| 文件页数: | 1/7页 |

| 文件大小: | 82K |

| 代理商: | IDT74LVCHR16501APV |

INDUSTRIALTEMPERATURERANGE

IDT74LVCHR16501A

3.3V CMOS 18-BIT REGISTERED TRANSCEIVER WITH 3-STATE OUTPUTS

1

JUNE 2006

INDUSTRIAL TEMPERATURE RANGE

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

2006 Integrated Device Technology, Inc.

DSC-4893/4

FEATURES:

Typical tSK(o) (Output Skew) < 250ps

ESD > 2000V per MIL-STD-883, Method 3015; > 200V using

machine model (C = 200pF, R = 0)

VCC = 3.3V ± 0.3V, Normal Range

VCC = 2.7V to 3.6V, Extended Range

CMOS power levels (0.4

μμμμμ W typ. static)

All inputs, outputs, and I/O are 5V tolerant

Supports hot insertion

Available in SSOP and TSSOP packages

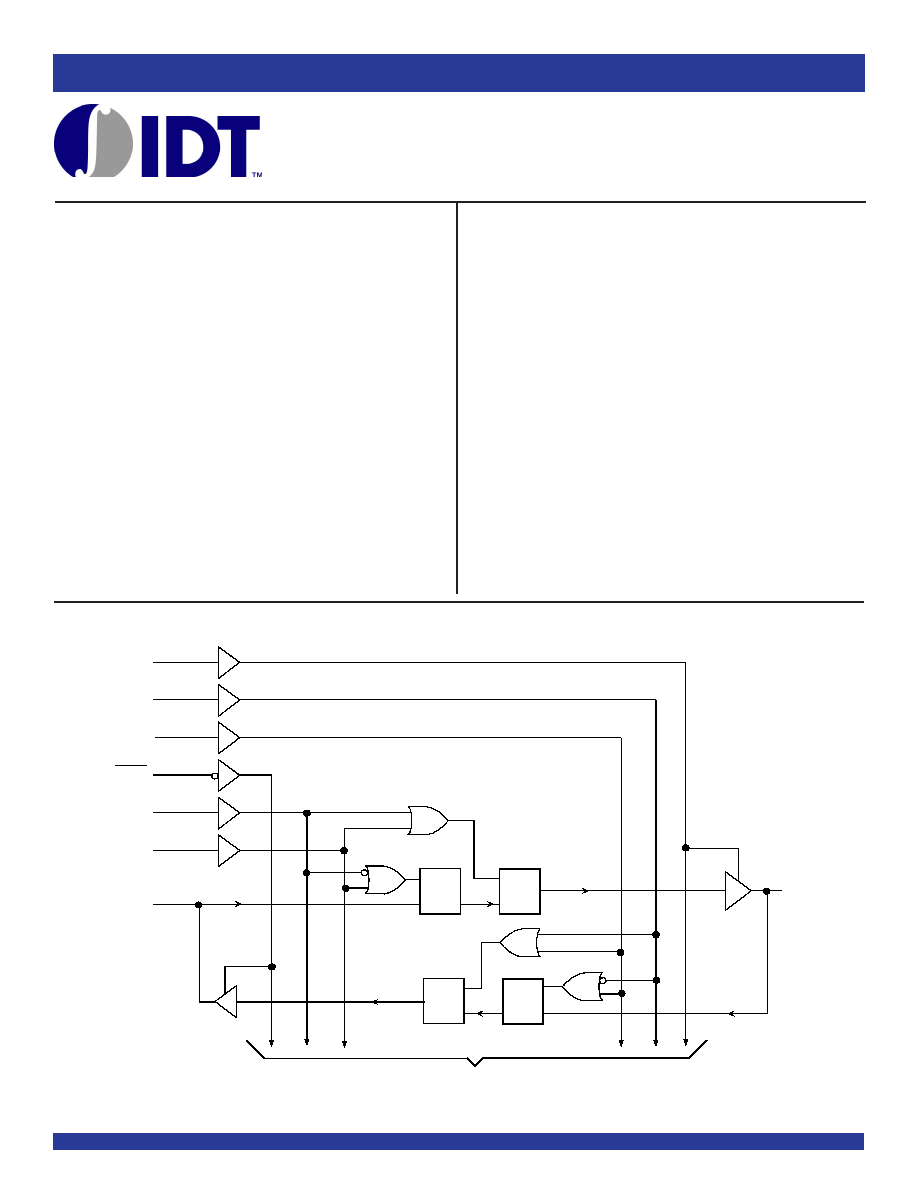

FUNCTIONAL BLOCK DIAGRAM

DRIVE FEATURES:

Balanced Output Drivers: ±12mA

Low switching noise

APPLICATIONS:

5V and 3.3V mixed voltage systems

Data communication and telecommunication systems

IDT74LVCHR16501A

DESCRIPTION:

The LVCHR16501A 18-bit registered transceiver is built using advanced

dual metal CMOS technology. This high-speed, low power 18-bit registered

bus transceiver combines D-type latches and D-type flip-flops to allow data

flow in transparent, latched, and clocked modes. Data flow in each direction

is controlled by output-enable (OEAB and

OEBA), latch enable (LEAB and

LEBA) and clock (CLKAB and CLKBA) inputs. For A-to-B data flow, the

device operates in transparent mode when LEAB is high. When LEAB is low,

the A data is latched if CLKAB is held at a high or low logic level. If LEAB

is low, the A bus data is stored in the latch/flip-flop on the low-to-high transition

of CLKAB. OEAB performs the output enable function on the B port. Data

flow from B port to A port is similar but requires using

OEBA, LEBA and

CLKBA. Flow-through organization of signal pins simplifies layout. All inputs

are designed with hysteresis for improved noise margin.

The LVCHR16501A has series resistors in the device output structure

which will significantly reduce line noise when used with light loads. This

driver has been developed to drive ±12mA at the designated thresholds.

The LVCHR16501A has “bus-hold” which retains the inputs’ last state

whenever the input goes to a high impedance. This prevents floating inputs

and eliminates the need for pull-up/down resistors.

3.3V CMOS 18-BIT

REGISTERED TRANSCEIVER

WITH 3-STATE OUTPUTS,

5 VOLT TOLERANT I/O, BUS-HOLD

B1

C

D

C

D

A1

LEAB

CLKAB

OEBA

LEBA

CLKBA

OEAB

TO 17 OTHER CHANNELS

C

D

C

D

1

30

28

27

55

2

3

54

相关PDF资料 |

PDF描述 |

|---|---|

| IDT74LVCHR16543APF8 | LVC/LCX/Z SERIES, DUAL 8-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PDSO56 |

| IDT74LVCHR16543APV8 | LVC/LCX/Z SERIES, DUAL 8-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PDSO56 |

| IDT74LVCHR16646APF8 | LVC/LCX/Z SERIES, DUAL 8-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PDSO56 |

| IDT74LVCHR16646APA | LVC/LCX/Z SERIES, DUAL 8-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PDSO56 |

| IDT74LVCHR2245AQ | LVC/LCX/Z SERIES, 8-BIT TRANSCEIVER, TRUE OUTPUT, PDSO20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT74LVCHR16646APAG | 功能描述:IC SERIAL RTC LP W/I2C 56-TSSOP RoHS:是 类别:未定义的类别 >> 其它 系列:* 标准包装:1 系列:* 其它名称:MS305720A |

| IDT74LVCHR16646APAG8 | 功能描述:IC SERIAL RTC LP W/I2C 56-TSSOP RoHS:是 类别:未定义的类别 >> 其它 系列:* 标准包装:1 系列:* 其它名称:MS305720A |

| IDT74LVCR162245APAG | 功能描述:IC BUS TRSCVR 3-ST 16BIT 48TSSOP RoHS:是 类别:集成电路 (IC) >> 逻辑 - 缓冲器,驱动器,接收器,收发器 系列:74LVCR 标准包装:47 系列:74LVX 逻辑类型:缓冲器/线路驱动器,非反相 元件数:4 每个元件的位元数:1 输出电流高,低:4mA,4mA 电源电压:2 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:14-SOIC(0.209",5.30mm 宽) 供应商设备封装:14-SOIC 包装:管件 |

| IDT74LVCR162245APAG8 | 功能描述:IC BUS TRSCVR 3-ST 16BIT 48TSSOP RoHS:是 类别:集成电路 (IC) >> 逻辑 - 缓冲器,驱动器,接收器,收发器 系列:74LVCR 标准包装:47 系列:74LVX 逻辑类型:缓冲器/线路驱动器,非反相 元件数:4 每个元件的位元数:1 输出电流高,低:4mA,4mA 电源电压:2 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:14-SOIC(0.209",5.30mm 宽) 供应商设备封装:14-SOIC 包装:管件 |

| IDT74LVCR162245APV | 制造商:Integrated Device Technology Inc 功能描述: |

发布紧急采购,3分钟左右您将得到回复。