- 您现在的位置:买卖IC网 > PDF目录377488 > IDTCSPT857CNLI (INTEGRATED DEVICE TECHNOLOGY INC) 2.5V - 2.6V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER PDF资料下载

参数资料

| 型号: | IDTCSPT857CNLI |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 2.5V - 2.6V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER |

| 中文描述: | 857 SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), QCC40 |

| 封装: | VFQFPN-40 |

| 文件页数: | 9/15页 |

| 文件大小: | 148K |

| 代理商: | IDTCSPT857CNLI |

9

IDTCSPT857C

2.5V - 2.6V PLL DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER

COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

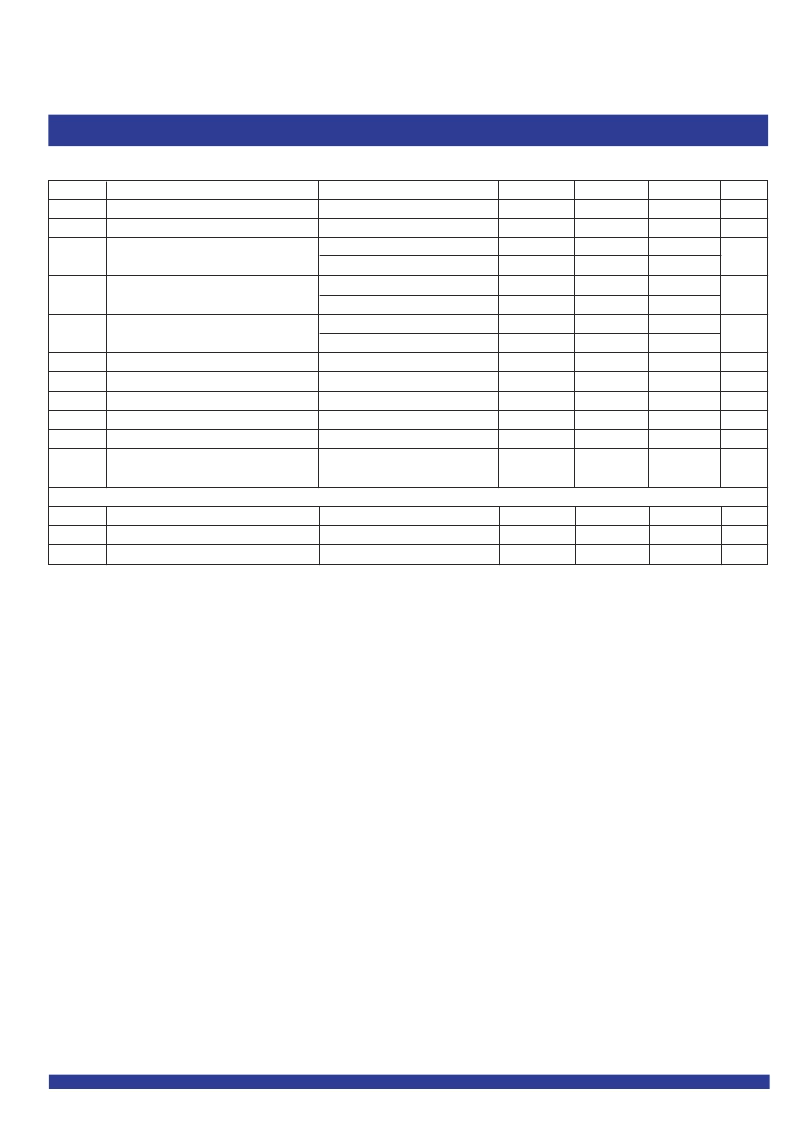

SWITCHING CHARACTERISTICS FOR PC3200

Symbol

Description

t

PLH(1)

LOW to HIGH Level Propagation Delay Time

t

PHL(1)

HIGH to LOW Level Propagation Delay Time

t

JIT(PER)

Jitter (period), see figure 6

Test Conditions

Test mode, CLK to any output

Test mode, CLK to any output

66MHz

200 MHz

66MHz

200 MHz

66MHz

200 MHz

200 MHz (20% to 80%)

Min.

Typ.

(1)

4.5

4.5

Max.

Unit

ns

ns

ps

– 90

– 50

– 180

– 75

– 160

– 75

1

1

– 50

90

50

180

75

160

75

2.5

4

50

75

900

V

DDQ

/2

+ 0.15

t

JIT(CC)

Jitter (cycle-to-cycle), see figure 3

ps

t

JIT(HPER)

Half-Period Jitter, see figure 7

ps

t

SLR(O)

t

SLR(I)

t

(

)

t

SK(O)

t

R,

t

F

V

OX(5)

Output Clock Slew Rate (Single-Ended)

Input Clock Slew Rate

Static Phase Offset, see figure 4

(2,3)

Output Skew, see figure 5

Output Rise and Fall Times (20% to 80%)

Output Differential Voltage

V/ns

V/ns

ps

ps

ps

V

200 MHz

Load: 120

/ 14pF

Differential outputs are termnated

with 120

650

V

DDQ

/2

– 0.15

The PLL on the CSPT857 will meet all the above test parameters while supporting SSC synthesizers

(4)

with the following parameters:

SSC

Modulation Frequency

SSC

Clock Input Frequency Deviation

f

3dB

PLL Loop Bandwidth

30

0

5

50

-0.5

KHz

%

MHz

NOTES:

1.

2.

3.

4.

5.

Refers to transition of non-inverting output.

Static phase offset does not include jitter.

t(

φ

) is measured with input clock slew rate t

SLR

(

I

) = 2V/ns and an input differential voltage V

ID

of 1.75V.

The SSC requirements meet the Intel PC100 SDRAMRegistered DIMMspecification.

V

OX

is specified at the SDRAMclock input or test load.

相关PDF资料 |

PDF描述 |

|---|---|

| IDTCSPT857CPA | 2.5V - 2.6V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER |

| IDTCSPT857CPAG | 2.5V - 2.6V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER |

| IDTCSPT857CPAGI | 2.5V - 2.6V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER |

| IDTCSPT857CPAI | 2.5V - 2.6V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER |

| IDTCSPT857CPF | 2.5V - 2.6V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDTCSPT857CPA | 制造商:IC'S/TRANSISTORS/DIO 功能描述: 制造商:IC'S/TRANSISTORS/DIODES 功能描述: |

| IDTCSPT857CPAG | 功能描述:IC SDRAM CLK DVR 1:10 48-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| IDTCSPT857CPAG8 | 功能描述:IC PLL CLK DVR SDRAM 48-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| IDTCSPT857CPAGI | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:2.5V - 2.6V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER |

| IDTCSPT857CPAI | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:2.5V - 2.6V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER |

发布紧急采购,3分钟左右您将得到回复。