- 您现在的位置:买卖IC网 > PDF目录239729 > IMSR-67025V-35 (TEMIC SEMICONDUCTORS) 8K X 16 DUAL-PORT SRAM, 35 ns, PQCC84 PDF资料下载

参数资料

| 型号: | IMSR-67025V-35 |

| 厂商: | TEMIC SEMICONDUCTORS |

| 元件分类: | SRAM |

| 英文描述: | 8K X 16 DUAL-PORT SRAM, 35 ns, PQCC84 |

| 封装: | PLASTIC, LCC-84 |

| 文件页数: | 22/23页 |

| 文件大小: | 257K |

| 代理商: | IMSR-67025V-35 |

M 67025

MATRA MHS

Rev. D (29/09/95)

8

semaphores are used, both the CPU and the I/0 device can

access assigned memory segments, without the need for

wait states, once the two devices have determined which

memory area is barred to the CPU.

Semaphores are also useful in applications where no

memory WAIT state is available on one or both sides. On

a semaphore handshake has been performed, both

processors can access their assigned RAM segments at

full speed.

Another application is in complex data structures. Block

arbitration is very important in this case, since one

processor may be responsible for building and updating

a data structure whilst the other processor reads and

interprets it. A major error condition may be created if the

interpreting processor reads an incomplete data structure.

Some sort of arbitration between the two different

processors is therefore necessary. The building processor

requests access to the block, locks it and is then able to

enter the block to update the data structure. Once the

update is completed the data structure may be released.

This allows the interpreting processor, to return to read

the complete data structure, thus ensuring a consistent

data structure.

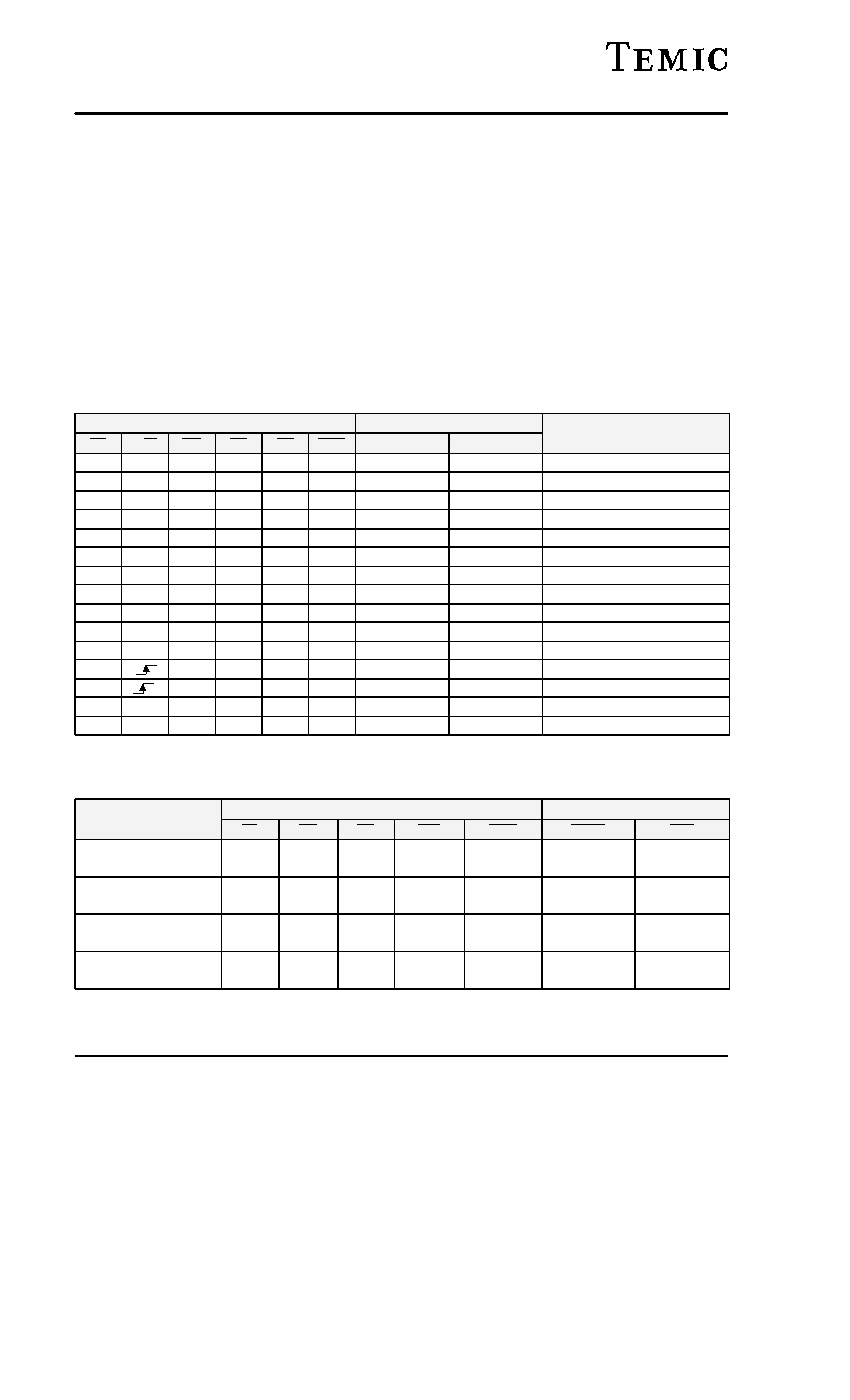

Truth Table

Table 1 : Non Contention Read/Write Control.

INPUTS (1)

OUTPUTS

MODE

CS

R/W

OE

UB

LB

SEM

IO8–IO15

I/O0–I/O7

MODE

H

X

H

Hi–Z

Deselected : Power Down

X

H

Hi–Z

Deselected : Power Down

L

X

L

H

DATAIN

Hi–Z

Write to Upper Byte Only

L

X

H

L

H

Hi–Z

DATAIN

Write to Lower Byte Only

L

X

L

H

DATAIN

Write to Both Bytes

L

H

L

H

DATAOUT

Hi–Z

Read Upper Byte Only

L

H

L

H

L

H

Hi–Z

DATAOUT

Read Lower Byte Only

L

H

L

H

DATAOUT

Read Both Bytes

X

H

X

Hi–Z

Outputs Disabled

H

L

X

L

DATAOUT

Read Data in Sema. Flag

X

H

L

H

L

DATAOUT

Read Data in Sema. Flag

H

X

L

DATAIN

Write DIN0 into Sema. Flag

X

H

L

DATAIN

Write DIN0 into Sema. Flag

L

X

L

X

L

–

Not Allowed

L

X

L

–

Not Allowed

Note :

1. A0L – A12L ≠ A0R – A12R.

Table 2 : Arbitration Options.

OPTIONS

INPUTS

OUTPUTS

OPTIONS

CS

UB

LB

M/S

SEM

BUSY

INT

Busy Logic Master

L

X

L

H

Output

–

yg

L

X

H

Signal

Busy Logic Slave

L

X

L

H

Input

–

yg

L

X

L

H

Signal

–

Interrupt Logic

L

X

L

X

H

–

Output

pg

L

X

H

Signal

Semaphore Logic*

H

X

H

L

H

–

pg

H

X

L

Hi–Z

* Inputs Signals are for Semaphore Flags set and test (Write and Read) operations.

相关PDF资料 |

PDF描述 |

|---|---|

| IM42-67025V-55 | 8K X 16 DUAL-PORT SRAM, 55 ns, CQCC84 |

| IDT7052S20G | 2K X 8 FOUR-PORT SRAM, 20 ns, CPGA108 |

| IS61NVP12836B-200B3 | 128K X 36 ZBT SRAM, 3.1 ns, PBGA165 |

| IDT7202SA120DB | 1K X 9 OTHER FIFO, 120 ns, CDIP28 |

| IDT7202SA25L8 | 1K X 9 OTHER FIFO, 25 ns, CQCC32 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IMSRA81AL | 制造商:Hubbell Wiring Device-Kellems 功能描述:ISTATION MOD, W/S-VID,RCA AUD,8P F,1U,AL |

| IMSRA81BK | 制造商:Hubbell Wiring Device-Kellems 功能描述:ISTATION MOD, W/S-VID,RCA AUD,8P F,1U,BK |

| IMSRA81EI | 制造商:Hubbell Wiring Device-Kellems 功能描述:ISTATION MOD, W/S-VID,RCA AUD,8P F,1U,EI |

| IMSRA81GY | 制造商:Hubbell Wiring Device-Kellems 功能描述:ISTATION MOD, W/S-VID,RCA AUD,8P F,1U,GY |

| IMSRA81LA | 制造商:Hubbell Wiring Device-Kellems 功能描述:ISTATION MOD, W/S-VID,RCA AUD,8P F,1U,LA |

发布紧急采购,3分钟左右您将得到回复。