- 您现在的位置:买卖IC网 > PDF目录383110 > IP82C54-12 (HARRIS SEMICONDUCTOR) CMOS Programmable Interval Timer PDF资料下载

参数资料

| 型号: | IP82C54-12 |

| 厂商: | HARRIS SEMICONDUCTOR |

| 元件分类: | XO, clock |

| 英文描述: | CMOS Programmable Interval Timer |

| 中文描述: | 3 TIMER(S), PROGRAMMABLE TIMER, PDIP24 |

| 文件页数: | 9/17页 |

| 文件大小: | 142K |

| 代理商: | IP82C54-12 |

4-9

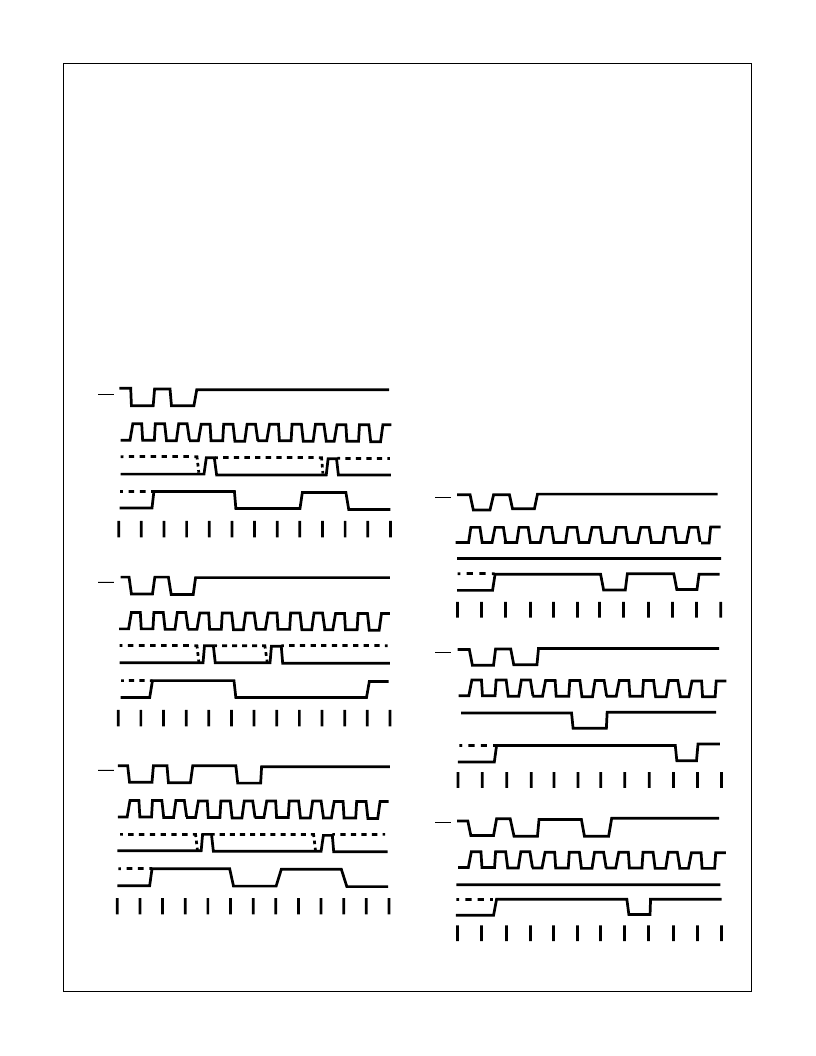

Mode 1: Hardware Retriggerable One-Shot

OUT will be initially high. OUT will go low on the CLK pulse

following a trigger to begin the one-shot pulse, and will remain

low until the Counter reaches zero. OUT will then go high and

remain high until the CLK pulse after the next trigger.

After writing the Control Word and initial count, the Counter is

armed. A trigger results in loading the Counter and setting

OUT low on the next CLK pulse, thus starting the one-shot

pulse N CLK cycles in duration. The one-shot is retriggerable,

hence OUT will remain low for N CLK pulses after any trigger.

The one-shot pulse can be repeated without rewriting the

same count into the counter. GATE has no effect on OUT.

If a new count is written to the Counter during a one-shot

pulse, the current one-shot is not affected unless the

Counter is retriggerable. In that case, the Counter is loaded

with the new count and the one-shot pulse continues until

the new count expires.

FIGURE 10. MODE 1

Mode 2: Rate Generator

This Mode functions like a divide-by-N counter. It is typically

used to generate a Real Time Clock Interrupt. OUT will ini-

tially be high. When the initial count has decremented to 1,

OUT goes low for one CLK pulse. OUT then goes high

again, the Counter reloads the initial count and the process

is repeated. Mode 2 is periodic; the same sequence is

repeated indefinitely. For an initial count of N, the sequence

repeats every N CLK cycles.

GATE = 1 enables counting; GATE = 0 disables counting. If

GATE goes low during an output pulse, OUT is set high

immediately. A trigger reloads the Counter with the initial

count on the next CLK pulse; OUT goes low N CLK pulses

after the trigger. Thus the GATE input can be used to syn-

chronize the Counter.

After writing a Control Word and initial count, the Counter will

be loaded on the next CLK pulse. OUT goes low N CLK

pulses after the initial count is written. This allows the

Counter to be synchronized by software also.

Writing a new count while counting does not affect the current

counting sequence. If a trigger is received after writing a new

count but before the end of the current period, the Counter will

be loaded with the new count on the next CLK pulse and count-

ing will continue from the end of the current counting cycle.

FIGURE 11. MODE 2

WR

CLK

GATE

OUT

WR

CLK

GATE

OUT

WR

CLK

GATE

OUT

N

N

N

N

0

3

0

2

0

1

0

0

FF

FF

0

3

0

2

N

CW = 12

LSB = 3

CW = 12

LSB = 3

CW = 12

LSB = 2

LSB = 4

N

N

N

N

0

2

0

1

0

0

FF

FF

FF

FE

0

4

0

3

N

N

N

N

N

0

3

0

2

0

1

0

3

0

2

0

1

0

0

N

N

N

N

N

0

2

0

1

0

3

0

2

0

1

0

3

0

3

N

N

N

N

0

2

0

2

0

3

0

2

0

1

0

3

0

3

N

N

N

N

0

3

0

2

0

1

0

5

0

4

0

3

0

4

WR

CLK

GATE

OUT

CW = 14

LSB = 3

WR

CLK

GATE

OUT

CW = 14

LSB = 3

WR

CLK

GATE

OUT

CW = 14

LSB = 4

LSB = 5

82C54

相关PDF资料 |

PDF描述 |

|---|---|

| IP82C54 | CMOS Programmable Interval Timer |

| IP82C54-10 | CMOS Programmable Interval Timer |

| IP82C59A | CMOS Priority Interrupt Controller |

| IP82C59A-5 | CMOS Priority Interrupt Controller |

| IP82C59A-12 | CMOS Priority Interrupt Controller |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IP82C54Z | 功能描述:计时器和支持产品 W/ANNEAL PERIPH PRG- CNTR 5V 8MHZ RoHS:否 制造商:Micrel 类型:Standard 封装 / 箱体:SOT-23 内部定时器数量:1 电源电压-最大:18 V 电源电压-最小:2.7 V 最大功率耗散: 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装:Reel |

| IP82C55A | 功能描述:外围驱动器与原件 - PCI PERIPH PRG-I/O 5V 8MHZ IND RoHS:否 制造商:PLX Technology 工作电源电压: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:FCBGA-1156 封装:Tray |

| IP82C55A/+ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Peripheral Interface |

| IP82C55A-5 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| IP82C55AS2064 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

发布紧急采购,3分钟左右您将得到回复。