- 您现在的位置:买卖IC网 > PDF目录383110 > IP82C59A (HARRIS SEMICONDUCTOR) CMOS Priority Interrupt Controller PDF资料下载

参数资料

| 型号: | IP82C59A |

| 厂商: | HARRIS SEMICONDUCTOR |

| 元件分类: | 中断控制器 |

| 英文描述: | CMOS Priority Interrupt Controller |

| 中文描述: | 80C86; 80C88; 80C286; 8080; 8085; 8086; 8088; 80286; NSC800 COMPATIBLE, INTERRUPT CONTROLLER, PDIP28 |

| 文件页数: | 4/20页 |

| 文件大小: | 152K |

| 代理商: | IP82C59A |

4-4

A more desirable method would be one that would allow the

microprocessor to be executing its main program and only

stop to service peripheral devices when it is told to do so by

the device itself. In effect, the method would provide an

external asynchronous input that would inform the processor

that it should complete whatever instruction that is currently

being executed and fetch a new routine that will service the

requesting device. Once this servicing is complete, however,

the processor would resume exactly where it left off.

This is the Interrupt-driven method. It is easy to see that sys-

tem throughput would drastically increase, and thus, more

tasks could be assumed by the microcomputer to further

enhance its cost effectiveness.

The Programmable Interrupt Controller (PlC) functions as an

overall manager in an Interrupt-Driven system. It accepts

requests from the peripheral equipment, determines which

of the incoming requests is of the highest importance (prior-

ity), ascertains whether the incoming request has a higher

priority value than the level currently being serviced, and

issues an interrupt to the CPU based on this determination.

Each peripheral device or structure usually has a special

program or “routine” that is associated with its specific func-

tional or operational requirements; this is referred to as a

“service routine”. The PlC, after issuing an interrupt to the

CPU, must somehow input information into the CPU that can

“point” the Program Counter to the service routine associ-

ated with the requesting device. This “pointer” is an address

in a vectoring table and will often be referred to, in this docu-

ment, as vectoring data.

82C59A Functional Description

The 82C59A is a device specifically designed for use in real

time, interrupt driven microcomputer systems. It manages

eight levels of requests and has built-in features for expand-

ability to other 82C59As (up to 64 levels). It is programmed

by system software as an I/O peripheral. A selection of prior-

ity modes is available to the programmer so that the manner

in which the requests are processed by the 82C59A can be

configured to match system requirements. The priority

modes can be changed or reconfigured dynamically at any

time during main program operation. This means that the

complete interrupt structure can be defined as required,

based on the total system environment.

Interrupt Request Register (IRR) and In-Service Register

(ISR)

The interrupts at the IR input lines are handled by two registers

in cascade, the Interrupt Request Register (lRR) and the In-

Service Register (lSR). The IRR is used to indicate all the inter-

rupt levels which are requesting service, and the ISR is used to

store all the interrupt levels which are currently being serviced.

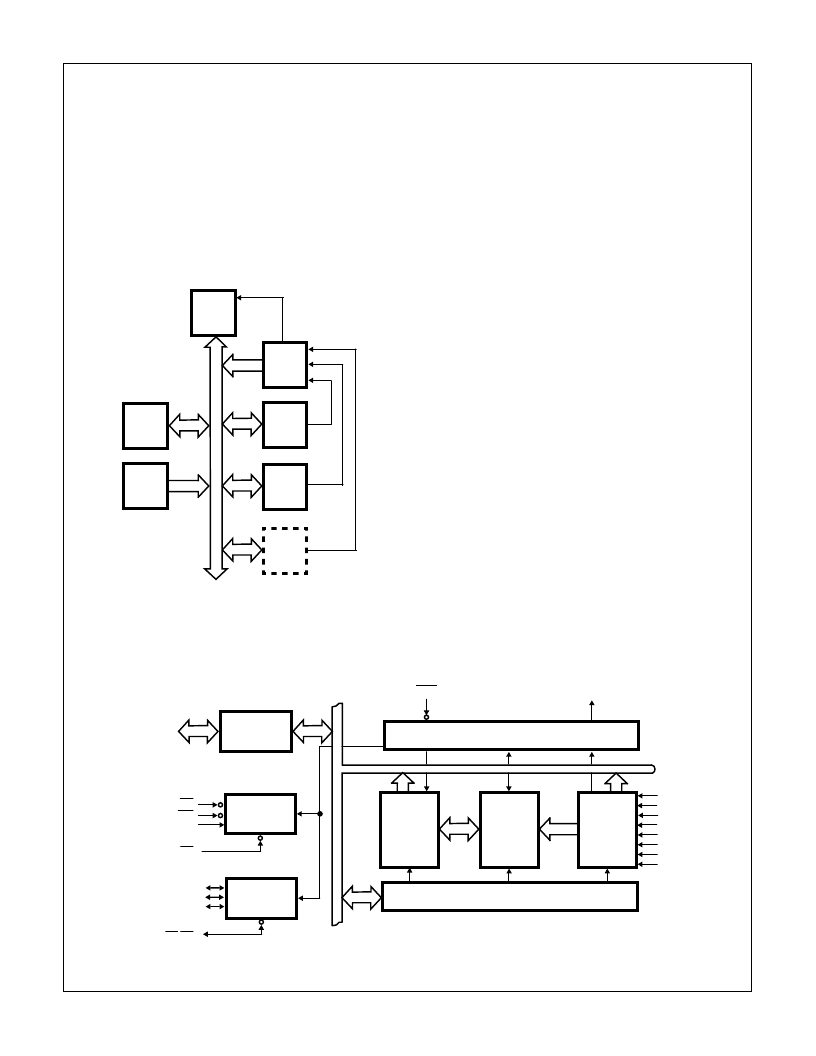

ROM

I/O (2)

RAM

CPU

INT

I/O (1)

I/O (N)

PIC

FIGURE 3. INTERRUPT METHOD

IR0

IR1

IR2

IR3

IR4

IR5

IR6

IR7

CASCADE

BUFFER

COMPARATOR

READ/

WRITE

LOGIC

DATA

BUS

BUFFER

IN

SERVICE

REG

(ISR)

PRIORITY

RESOLVER

INTERRUPT MASK REG

(IMR)

INTERRUPT

REQUEST

REG

(IRR)

CONTROL LOGIC

INT

INTA

CAS 0

CAS 1

CAS 2

RD

WR

A

0

SP/EN

CS

D

7

- D

0

INTERNAL BUS

FIGURE 4. 82C59A FUNCTIONAL DIAGRAM

82C59A

相关PDF资料 |

PDF描述 |

|---|---|

| IP82C59A-5 | CMOS Priority Interrupt Controller |

| IP82C59A-12 | CMOS Priority Interrupt Controller |

| IP82C83H | CMOS Octal Latching Inverting Bus Driver |

| IP82C84A | CMOS Clock Generator Driver |

| IP82C86H | CMOS Octal Bus Transceiver |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IP82C59A10 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Controller Miscellaneous - Datasheet Reference |

| IP82C59A-10 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| IP82C59A-12 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| IP82C59A-5 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述: |

| IP82C59AS2064 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。