- 您现在的位置:买卖IC网 > PDF目录383129 > ISL3873A (Intersil Corporation) Wireless LAN Integrated Medium Access Controller with Baseband Processor PDF资料下载

参数资料

| 型号: | ISL3873A |

| 厂商: | Intersil Corporation |

| 元件分类: | 基带处理器 |

| 英文描述: | Wireless LAN Integrated Medium Access Controller with Baseband Processor |

| 中文描述: | 集成的无线局域网媒体访问控制器基带处理器 |

| 文件页数: | 16/42页 |

| 文件大小: | 778K |

| 代理商: | ISL3873A |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页

16

PE1 and PE2 encoding details are found in Table 2.

Note that during normal receive and transmit operation that

PE1 is static and PE2 toggles for receive and transmit

states.

Master Clock

Prescaler

The ISL3873A contains a clock prescaler to provide flexibility in

the choice of clock input frequencies. For 11Mb/s operation, the

internal master clock, MCLK, must be at least 11MHz. The

clock generator itself requires an input from the prescaler that is

twice the desired MCLK frequency. Thus the lowest oscillator

frequency thatcan be used for an 11MHz MCLK is 22MHz. The

prescaler can divide by integers and 1/2 steps (IE1, 1.5, 2, 2.5).

Another way to look at it is that the divisor ratio between the

external clock source and the internal MCLK may be integers

between 2 and 14.

Typically, the 44MHz baseband clock is used as the input, and

the prescaler is set to divide by 2. Contact the factory for further

details on setting the clock prescaler register in the ISL3873A.

Low-Frequency Crystal

The ISL3873AMACcontroller can accept the same clock signal

as the PHY baseband processor (typically 44MHz), thereby

avoiding the need for a separate, MAC-specific oscillator. The

ISL3873A input has a low-frequency oscillator. This low-

frequency oscillator is intended for use with a 32.768KHz,

tuning-fork type watch crystal to permit accurate timekeeping

with very low power consumption during sleep state.

If a 32.768KHz crystal is connected, the resulting LF clock is

supplied to an interval timer to permit measuring sleep

intervals as well as providing a programmable wake-up time.

In addition, the clock generator can operate either from CLKIN

or (very slowly) from the LF clock. Glitch-free switching

between these two clock sources, under firmware control, is

provided by two, non-architectural Strobe functions (“FAST”

and “SLOW”). In addition, during hardware reset, the clock

generator source is set to the LF clock if no edges are

detected on CLKIN for two cycles of the LF clock (roughly 61

microseconds). This allows proper initialization with omission

of either clock source, since without the LF crystal attached

there will not be cycles of the LF clock to activate the detection

circuit. The ability to initialize the ISL3873A using the LF

oscillator to generate MCLK allows the high-frequency (PHY)

oscillator to be powered down during sleep state. If this is

done, firmware can turn on power to the PHY oscillator upon

wake-up, and use the interval timer to measure the start-up

and stabilization period before switching to use CLKIN.

Clock Generator

The ISL3873A can operate with MCLK frequencies up to at

least 12MHz and CLKIN frequencies of at least 50MHz. The

MCLK prescaler generates MCLK (and QCLK) from the

external clock provided atthe CLKINinput,or fromthe output of

the LF oscillator. The MCLK prescaler divides the selected

input clock by any integer value between 2 and 16, inclusive.

When using a 44MHz CLKIN, as is typical for 802.11 or

802.11b controllers with a PC Card Host Interface, common

divisors are 4 (11MHz) or 5 (8.8MHz)

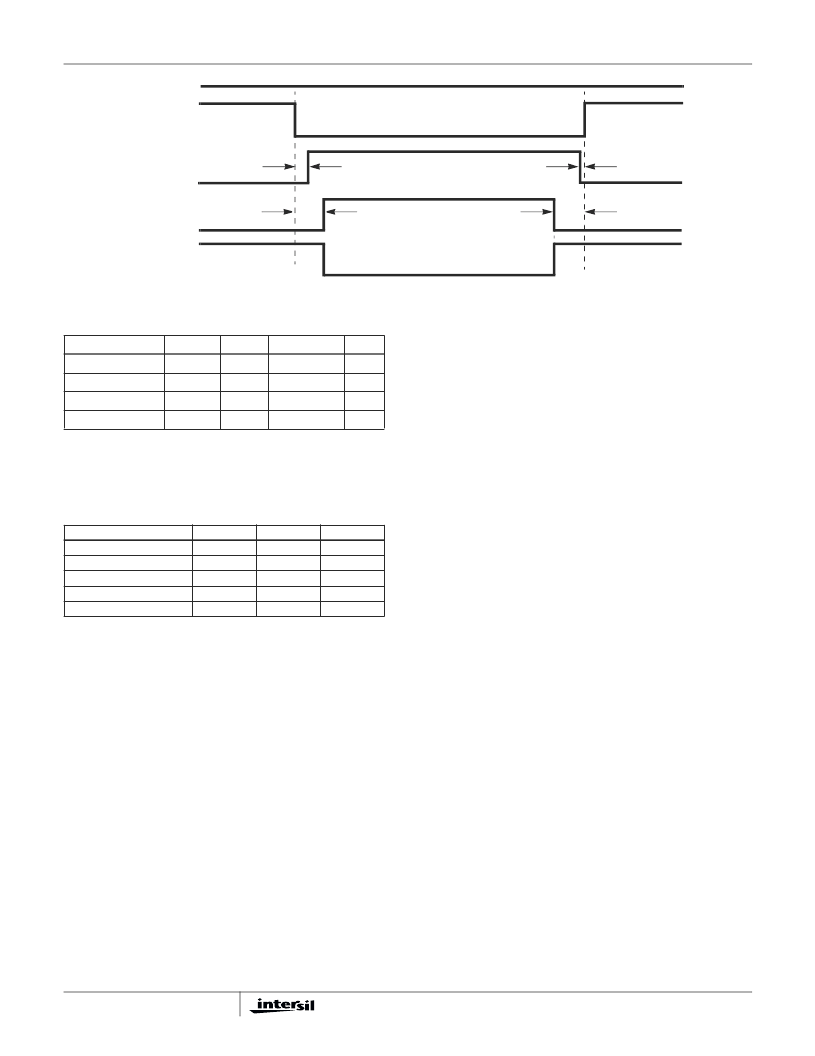

FIGURE 10. TRANSMIT CONTROL SIGNAL SEQUENCING

PE1

PE2

TR_SW

TR_SW_BAR

PA_PE

t

D1

t

D5

t

D3

t

D4

TABLE 1. TRANSMIT CONTROL TIMING SPECIFICATIONS

PARAMETER

SYMBOL

DELAY

TOLERANCE

UNITS

PE2 to PA_PE

t

D1

t

D3

t

D4

t

D5

0.1

±

0.1

±

0.1

±

0.1

±

0.1

μ

s

μ

s

μ

s

μ

s

TPE2 to TR Switch

1.5

TR Switch to PE2

3

PA_PE to PE2

1

TABLE 2. POWER ENABLE STATES

PE1

Power Down State

Receive State

Transmit State

PLL Active State

PLL Disable State

PLL_PE is controlled via the serial interface, and can be used to

disable the internal synthesizer, the actual synthesizer control is an

AND function of PLL_PE, and a result of the OR function of PE1

and PE2. PE1 and PE2 will directly control the power enable

functionality of the LO buffer(s)/phase shifter.

PE2

0

1

0

1

X

PLL_PE

1

1

1

1

0

0

1

1

0

X

ISL3873A

相关PDF资料 |

PDF描述 |

|---|---|

| ISL3873AIK | RES 0805 1/8W 5% 1.2KOHM |

| ISL3874IK96 | Wireless LAN Integrated Medium Access Controller with Baseband Processor with Mini-PCI |

| ISL3874 | Wireless LAN Integrated Medium Access Controller with Baseband Processor with Mini-PCI |

| ISL3874IK | Wireless LAN Integrated Medium Access Controller with Baseband Processor with Mini-PCI |

| ISL39300A-DAPDK-CD | PRISM 54Mbps Wireless Local Area Network Access Point |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL3873AIK | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Wireless LAN Integrated Medium Access Controller with Baseband Processor |

| ISL3873AIK-TK | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Wireless LAN Integrated Medium Access Controller with Baseband Processor |

| ISL3873BIK | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Intersil Corporation 功能描述: |

| ISL3873BIK-TK | 制造商:Intersil Corporation 功能描述:1 CHANNEL(S), 11M bps, LOCAL AREA NETWORK CONTROLLER, PBGA192 |

| ISL3873IK | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Wireless LAN Integrated Medium Access Controller with Baseband Processor |

发布紧急采购,3分钟左右您将得到回复。