- 您现在的位置:买卖IC网 > PDF目录10589 > ISL59885ISZ-T7 (Intersil)IC VIDEO SYNC SEPARATOR 8-SOIC PDF资料下载

参数资料

| 型号: | ISL59885ISZ-T7 |

| 厂商: | Intersil |

| 文件页数: | 4/15页 |

| 文件大小: | 0K |

| 描述: | IC VIDEO SYNC SEPARATOR 8-SOIC |

| 标准包装: | 1 |

| 类型: | 同步分离器 |

| 应用: | HD 视频 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 8-SOIC(0.154",3.90mm 宽) |

| 供应商设备封装: | 8-SOICN |

| 包装: | 标准包装 |

| 产品目录页面: | 1247 (CN2011-ZH PDF) |

| 其它名称: | ISL59885ISZ-T7DKR |

ISL59885

12

FN7442.8

October 31, 2011

Applications Information

Video In

An AC-coupled video signal is input to Video In pin 2 via C1,

nominally 0.1F. Clamp charge current prevents the signal on

pin 2 from going any more negative than Sync Tip Ref, about

1.5V. This charge current is nominally about 1mA. A clamp

discharge current of about 10A is always attempting to

discharge C1 to Sync Tip Ref; thus, charge is lost between sync

pulses that must be replaced during sync pulses. Droop voltage

can be calculated from It = CV, where V is the droop voltage, I is

the discharge current, t is the time between sync pulses (sync

period-sync tip width), and C is C1.

An NTSC video signal has a horizontal frequency of 15.73kHz

and a sync tip width of 4.7s. This gives a period of 63.6s and a

time of t = 58.9s. The droop voltage will then be V = 5.9mV. This

is less than 2% of a nominal sync tip amplitude of 286mV. The

charge represented by this droop is replaced in a time given by

t = CV/I, where I = clamp charge current = 5.3mA. Here,

t = 590ns, about 12% of the sync pulse width of 4.7s. It is

important that C1 be large enough that droop voltage does not

approach the switching threshold of the internal comparator.

Composite Sync

The composite sync output is simply a reproduction of the input

signal with the active video removed. The sync tip of the

composite video signal is clamped to 1.5V at pin 2 and then

slices at 70mV above the sync tip reference. The output signal is

buffered out to pin 1. When there is loss of sync, the composite

sync output is held low.

Vertical Sync

A low-going vertical sync pulse is output during the start of the

vertical cycle of the incoming video signal. The vertical cycle

starts with a pre-equalizing phase of pulses with a duty cycle of

about 93%, followed by a vertical serration phase that has a duty

cycle of about 15%. Vertical sync is clocked out of the ISL59885

on the first rising edge during the vertical serration phase. In the

absence of vertical serration pulses, a vertical sync pulse is

forced out after the vertical sync default delay time, which is

approximately 60s after the last falling edge of the vertical

equalizing phase.

Horizontal Sync

The horizontal block senses the leading edges of the composite

sync signal and generates horizontal pulses of nominal width

5.2s. Any half line pulses present in the input signal during

vertical blanking are removed with an internal 2H line eliminator

function that inhibits retriggering of horizontal output pulses until

70% of the line time is reached. Then, the horizontal output

operation is enabled again. Any signals present on the I/P signal

after the real H sync are ignored; thus, the horizontal output is

not affected by MacroVision copy protection. When there is a loss

of incoming composite sync, the horizontal sync output is held

high.

CSET

An external CSET capacitor is connected from CSET pin 6 to

ground. The CSET capacitor should be a X7R grade or better

because the Y5U general use capacitors may be too leaky and

cause faulty operation. The CSET capacitor should be very close

to the CSET pin to reduce possible board leakage. A setting of

56nF is recommended (see “CSET Bias Block Diagram” on

creates a voltage on CSET. The CSET voltage is converted to bias

current for HSYNC and VSYNC timing.

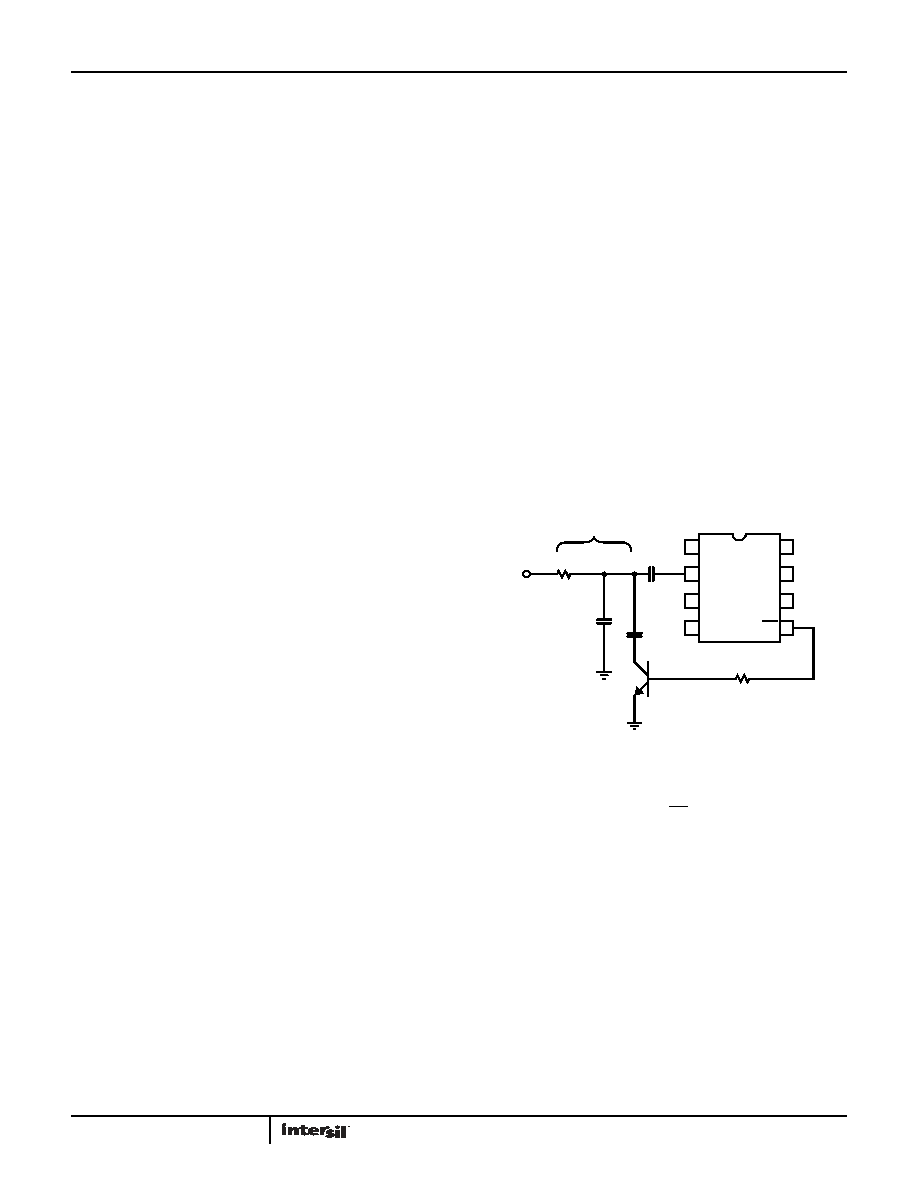

Chroma Filter

A chroma filter is suggested to increase the S/N ratio of the

incoming video signal. Use of the optional chroma filter is shown

in Figure 16. It can be implemented very simply and

inexpensively with a series resistor of 100 and a capacitor of

570pF, which gives a single pole roll-off frequency of about

2.79MHz during NTSC or PAL. This sufficiently attenuates the

3.58MHz (NTSC) or 4.43MHz (PAL) color burst signal, yet passes

the approximately 15kHz sync signals without appreciable

attenuation. During HDTV, the transistor turns off and a 100pF

capacitor is left to filter any noise present at the input. A chroma

filter will increase the propagation delay from the composite

input to the outputs.

HD-Detect

High definition video is flagged by HD going low when the input

horizontal frequency is greater than 25kHz.

ISL59885

0.1F

100

RF

CF2

470pF

VIDEO IN

CHROMA FILTER

1

2

3

4

8

7

6

5

HD

10k

MMBT3904

GND

VDD

CSET

CVIN

CSYNC

HOUT

VSYNC

CF

100pF

FIGURE 16. OPTIONAL CHROMA FILTER

相关PDF资料 |

PDF描述 |

|---|---|

| EL1881CSZ-T7A | IC VIDEO SYNC SEPARATOR 8SOIC |

| HI3-574AKN-5Z | IC ADC 12BIT 40KSPS 28-PDIP |

| PT06A-8-2P | CONN PLUG 2 POS STRAIGHT W/PINS |

| EL1883ISZ-T7 | IC VID SYNC SEPARATOR HORZ 8SOIC |

| EL1883ISZ-T13 | IC VID SYNC SEPARATOR HORZ 8SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL59885ISZ-T7A | 功能描述:视频 IC ISL9214A EVALRD 1 RHS CMPL 10LD DF RoHS:否 制造商:Fairchild Semiconductor 工作电源电压:5 V 电源电流:80 mA 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-28 封装:Reel |

| ISL59885ISZ-T7R5218 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Intersil Corporation 功能描述: |

| ISL59885ISZ-T7R5260 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Auto-Adjusting Sync Separator for HD and SD Video |

| ISL59886ISZ | 功能描述:IC SEPARATOR VID SYNC AUTO 8SOIC RoHS:是 类别:集成电路 (IC) >> 线性 - 视频处理 系列:- 标准包装:250 系列:- 类型:电平移位器 应用:LCD 电视机/监控器 安装类型:表面贴装 封装/外壳:28-WFQFN 裸露焊盘 供应商设备封装:28-WQFN(4x4)裸露焊盘 包装:带卷 (TR) 其它名称:296-32523-2TPS65198RUYT-ND |

| ISL59886ISZ-T13 | 功能描述:IC SEPARATOR VID SYNC AUTO 8SOIC RoHS:是 类别:集成电路 (IC) >> 线性 - 视频处理 系列:- 产品变化通告:Product Discontinuation 07/Mar/2011 标准包装:3,000 系列:OMNITUNE™ 类型:调谐器 应用:移动电话,手机,视频显示器 安装类型:表面贴装 封装/外壳:65-WFBGA 供应商设备封装:PG-WFSGA-65 包装:带卷 (TR) 其它名称:SP000365064 |

发布紧急采购,3分钟左右您将得到回复。