- 您现在的位置:买卖IC网 > PDF目录383139 > ISL6121LIB-T (INTERSIL CORP) Single Supply Integrated Current Limiting Controller PDF资料下载

参数资料

| 型号: | ISL6121LIB-T |

| 厂商: | INTERSIL CORP |

| 元件分类: | 电源管理 |

| 英文描述: | Single Supply Integrated Current Limiting Controller |

| 中文描述: | 1-CHANNEL POWER SUPPLY SUPPORT CKT, PDSO8 |

| 封装: | PLASTIC, MS-012AA, SOIC-8 |

| 文件页数: | 15/16页 |

| 文件大小: | 566K |

| 代理商: | ISL6121LIB-T |

15

FN9005.4

June 10, 2005

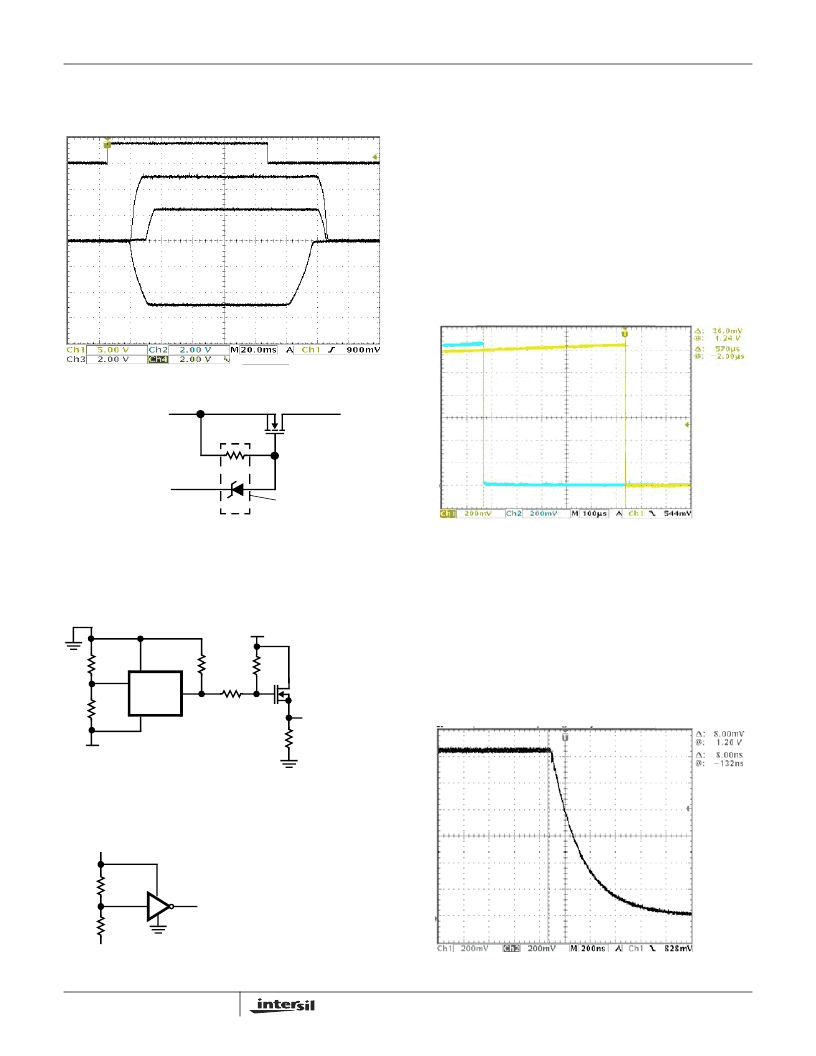

Figures 24 and 25 illustrate a high accuracy -V detection

circuit using the ISL6131and a low cost low accuracy -V

detect circuit and respectively.

Application Considerations

Timing Error Sources

In any system there are variance contributors, for the ISL612X

family the timing errors are mainly contributed by three sources.

Capacitor Timing Mismatch Error

Obviously, the absolute capacitor value is an error source

thus lower percentage tolerance capacitors help to reduce

this error source. Figure 26 illustrates a difference of 0.57ms

between two DLY_X outputs ramping to DLY_X threshold

voltage, these 5% capacitors were from a common source.

In applications where two or more GATEs or LOGIC outputs

must have concurrent transitions, it is recommended that a

common DLY_X cap. be used to eliminate this timing error.

DLY_X Threshold Voltage and Charging Current

Mismatch

The two other error sources come from the IC itself and are

the differences in the DLY_X threshold voltage, (DLY_Vth)

when the GATE charging latch is set and the DLY_X

charging current, (DLY_ichg) across the four individual I/Os.

Both of these parameters are bounded by specification and

Figure 27 illustrates that with a common capacitor the typical

error contributed by these factors is insignificant as both

DLY_X traces overlay each other.

FIGURE 22. ±VOLTAGE SEQUENCING

FIGURE 23. -VOLTAGE FET DRIVE CIRCUIT

FIGURE 24. HGH ACCURACY -V LOCK OUT

FIGURE 25. LOW ACCURACY -V PRESENCE DETECTION

ISL612X GATE

-Vin

-Vout

D1

R1

Additional 2 components

necessary for -V control

and sequencing.

D1 necessary to prevent premature turn-on. R1 is used

to hold FET Vgs = 0V until D1 Vz is overcome. R1 value

can be changed to adjust -V ramp rates. Choose a R1

value between 4M

and 10M

initially and fine tune

resistor value for the particular need.

ISL6131

OR

ISL6536A

-V

+V

TO UVLO OF

ISL612X FOR

-V CONTROL AND

SEQUENCING

R1

R2

R3

(1K)

R4

(15K)

R5

(10K)

R6

R1 and R2 define -V UVLO level

R3 ensures supervisor (ISL6131 or ISL6536A) PGOOD pull-up

R4 and R5 provide Q1 gate bias between 0V and +V

to 0V (resistor values suitable for -V = -5V and +V = +3.3V)

Q1 Si1300DL

OR EQUIV.

-BIAS

VMON

PGOOD

+BIAS

+V

-V

TO UVLO OF ISL612X FOR CONTROL

AND SEQUENCING OF -V

R1

R2

Chose R1 and R2 values to drive UVLO

high when -V is sufficiently present

FIGURE 26. CAPACITOR TIMING MISMATCH

FIGURE 27. DLY_VTH AND DLY_ICHG TIMING MISMATCH

ISL6123, ISL6124, ISL6125, ISL6126, ISL6127, ISL6128

相关PDF资料 |

PDF描述 |

|---|---|

| ISL6124IR | Power Sequencing Controllers |

| ISL6126IRZA | CAP 2.2UF 6.3V CERAMIC X5R 0805 |

| ISL6127IR | Power Sequencing Controllers |

| ISL6128IR | Power Sequencing Controllers |

| ISL6121LIBZA | Single Supply Integrated Current Limiting Controller |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6121LIBZA | 功能描述:IC SUPPLY/CURR LIMIT CTRLR 8SOIC RoHS:是 类别:集成电路 (IC) >> PMIC - 电源控制器,监视器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 应用:多相控制器 输入电压:- 电源电压:9 V ~ 14 V 电流 - 电源:- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:40-WFQFN 裸露焊盘 供应商设备封装:40-TQFN-EP(5x5) 包装:带卷 (TR) |

| ISL6121LIBZA-T | 功能描述:IC SUPPLY/CURR LIMIT CTRLR 8SOIC RoHS:是 类别:集成电路 (IC) >> PMIC - 电源控制器,监视器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 应用:多相控制器 输入电压:- 电源电压:9 V ~ 14 V 电流 - 电源:- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:40-WFQFN 裸露焊盘 供应商设备封装:40-TQFN-EP(5x5) 包装:带卷 (TR) |

| ISL6123 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Power Sequencing Controllers |

| ISL6123_07 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Power Sequencing Controllers |

| ISL6123_11 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Power Sequencing Controllers |

发布紧急采购,3分钟左右您将得到回复。