参数资料

| 型号: | ISL612XSEQEVAL1Z |

| 厂商: | Intersil |

| 文件页数: | 9/23页 |

| 文件大小: | 0K |

| 描述: | EVALUATION BOARD ISL612XSEQ |

| 标准包装: | 1 |

| 主要目的: | 电源管理,电源监控器/跟踪器/序列发生器 |

| 嵌入式: | 否 |

| 已用 IC / 零件: | ISL6123,ISL6124,ISL6126,ISL6127,ISL6128,ISL6130 |

| 主要属性: | 4 通道电源定序器 |

| 次要属性: | 欠压保护 |

| 已供物品: | 板,IC 样品 |

�� �

�

�

�ISL6123,� ISL6124,� ISL6125,� ISL6126,� ISL6127,� ISL6128,� ISL6130�

�level� of� feedback� and� control,� if� desired.� The� ISL6128� requires�

�that� the� related� ENABLE� be� cycled� for� restart� of� its� associated�

�group� GATEs.� If� no� capacitors� are� connected� between� DLY_ON� or�

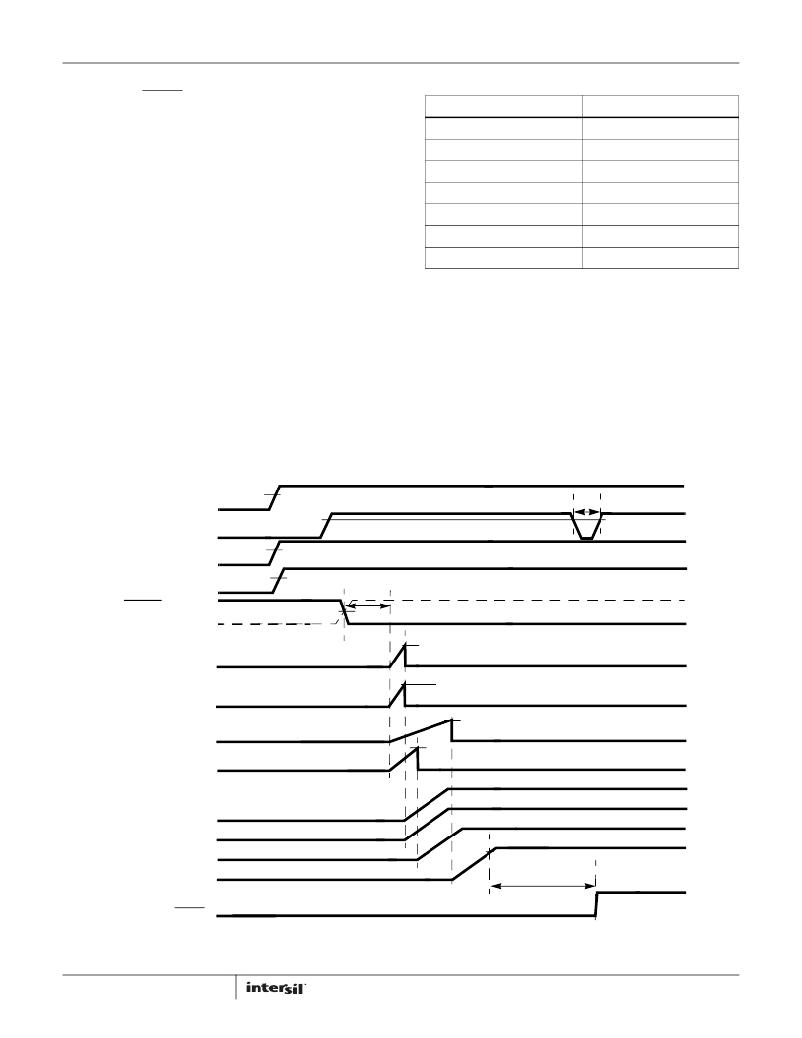

�TABLE� 1.� NOMINAL� DELAY� TO� SEQUENCING� THRESHOLD�

�DLY� PIN� CAPACITANCE� TIME(s)�

�DLY_OFF� pins� and� ground,� then� all� such� related� GATEs� start� to�

�turn� on� immediately� after� the� 10ms� (TUVLOdel)� ENABLE�

�stabilization� timeout� has� expired.� The� GATEs� start� to� turn� off�

�immediately� when� ENABLE� is� asserted.�

�If� some� of� the� rails� are� sequenced� together� to� reduce� cost� and�

�eliminate� the� effect� of� capacitor� variance� on� the� timing,� a�

�common� capacitor� can� be� connected� to� two� or� more� DLY_ON� or�

�DLY_OFF� pins.� In� this� case,� multiply� the� capacitor� value� by� the�

�number� of� common� DLY_X� pins� to� obtain� the� desired� timing.�

�Open�

�100pF�

�1000pF�

�0.01μF�

�0.1μF�

�1μF�

�10μF�

�0.00006�

�0.00013�

�0.0013�

�0.013�

�0.13�

�1.3�

�13�

�Table� 1� shows� the� nominal� time� delay� on� the� DLY_X� pins� for�

�various� capacitor� values,� from� the� start� of� charging� to� the� 1.27V�

�reference.� This� table� does� not� include� the� 10ms� of� ENABLE�

�lockout� delay� during� a� start-up� sequence,� but� it� does� represent�

�the� time� from� the� end� of� the� ENABLE� lockout� delay� to� the� start�

�of� GATE� transition.� There� is� no� ENABLE� lockout� delay� for� a�

�sequence-off,� so� this� table� illustrates� the� delay� to� GATE�

�transition� from� a� disable� signal.�

�NOTE:� Nom.� T� DEL_SEQ� =� Capacitor� (μF)*1.3M� Ω� .�

�Figure� 4� shows� the� turn-on� and� Figure� 5� shows� the� nominal�

�turn-off� timing� diagram� of� the� ISL6123� and� ISL6124.�

�The� ISL6125� is� similar� to� the� ISL6124� except� that,� instead� of�

�charge� pumped� GATE� outputs,� there� are� sequenced� open-drain�

�outputs� that� can� be� pulled� up� to� a� maximum� of� V� DD� .�

�Delay� and� flexible� sequencing� possibilities� include� multiple� series,�

�parallel,� or� adjustable� capacitors� that� can� be� used� to� easily�

�fine-tune� timing� over� that� offered� by� standard� value� capacitors.�

�UVLO_A�

�V� UVLOVth�

�<t� FIL�

�V� UVLOVth�

�UVLO_B�

�V� UVLOVth�

�UVLO_C�

�V� UVLOVth�

�UVLO_D�

�ENABLE� (ISL6124)�

�t� UVLOdel�

�V� EN�

�ENABLE� (ISL6123)�

�DLY_Vth�

�DLYON_B�

�DLY_Vth�

�DLYON_D�

�DLY_Vth�

�DLYON_A�

�DLY_Vth�

�DLYON_C�

�V� QPUMP�

�V� QPUMP�

�GATE_B�

�GATE_D�

�GATE_C�

�GATE_A�

�V� QPUMP� -1V�

�t� RSTdel�

�V� QPUMP�

�V� QPUMP�

�RESET�

�FIGURE� 4.� ISL6123,� ISL6124� TURN-ON� AND� GLITCH� RESPONSE� TIMING� DIAGRAM�

�9�

�FN9005.12�

�September� 26,� 2012�

�相关PDF资料 |

PDF描述 |

|---|---|

| ISL6142/52EVAL1 | EVAL BOARD W/CURRENT MONITOR |

| ISL6144EVAL1 | EVALUATION BOARD ISL6144 ORING |

| ISL61853EVAL1Z | EVAL BOARD FOR ISL61853 |

| ISL6227EVAL1 | EVALUATION BOARD 1 ISL6227 |

| ISL62386HIEVAL1Z | EVAL BOARD FOR ISL62386HI 32TQFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6130 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Power Sequencing Controllers |

| ISL6130IRZA | 功能描述:IC POWER SUPPLY SEQUENCER 24QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 电源控制器,监视器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 应用:多相控制器 输入电压:- 电源电压:9 V ~ 14 V 电流 - 电源:- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:40-WFQFN 裸露焊盘 供应商设备封装:40-TQFN-EP(5x5) 包装:带卷 (TR) |

| ISL6130IRZA-T | 功能描述:IC POWER SUPPLY SEQUENCER 24QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 电源控制器,监视器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 应用:多相控制器 输入电压:- 电源电压:9 V ~ 14 V 电流 - 电源:- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:40-WFQFN 裸露焊盘 供应商设备封装:40-TQFN-EP(5x5) 包装:带卷 (TR) |

| ISL6130IRZA-TS2378 | 制造商:Intersil Corporation 功能描述: |

| ISL6131 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Multiple Voltage Supervisory ICs |

发布紧急采购,3分钟左右您将得到回复。