参数资料

| 型号: | ISL6425ERZ-T |

| 厂商: | Intersil |

| 文件页数: | 9/12页 |

| 文件大小: | 0K |

| 描述: | IC REG DUAL LNBP TTL-INP 32-QFN |

| 标准包装: | 6,000 |

| 应用: | 转换器,卫星信号接收机顶盒设计 |

| 输入电压: | 8 V ~ 14 V |

| 输出数: | 2 |

| 输出电压: | 13 V ~ 18 V |

| 工作温度: | -20°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-VFQFN 裸露焊盘 |

| 供应商设备封装: | 32-QFN(5x5) |

| 包装: | 带卷 (TR) |

�� �

�

�

�ISL6425�

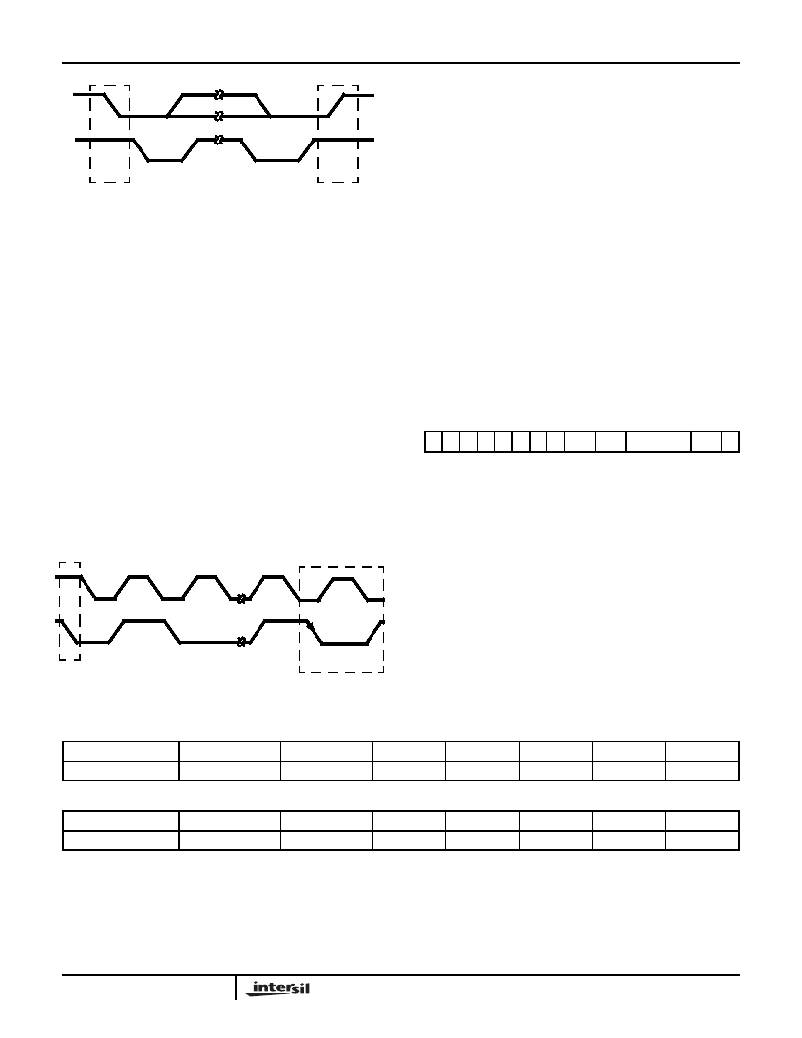

�Transmission� Without� Acknowledge�

�SDA�

�SCL�

�Avoiding� detection� of� the� acknowledgement,� the�

�microprocessor� can� use� a� simpler� transmission;� it� waits� one�

�clock� without� checking� the� slave� acknowledging,� and� sends�

�the� new� data.�

�S�

�START�

�CONDITION�

�P�

�STOP�

�CONDITION�

�This� approach,� though,� is� less� protected� from� error� and�

�decreases� the� noise� immunity.�

�FIGURE� 2.� START� AND� STOP� WAVEFORMS�

�Byte� Format�

�Every� byte� put� on� the� SDA� line� must� be� 8� bits� long.� The� number�

�of� bytes� that� can� be� transmitted� per� transfer� is� unrestricted.�

�Each� byte� has� to� be� followed� by� an� acknowledge� bit.� Data� is�

�transferred� with� the� most� significant� bit� first� (MSB).�

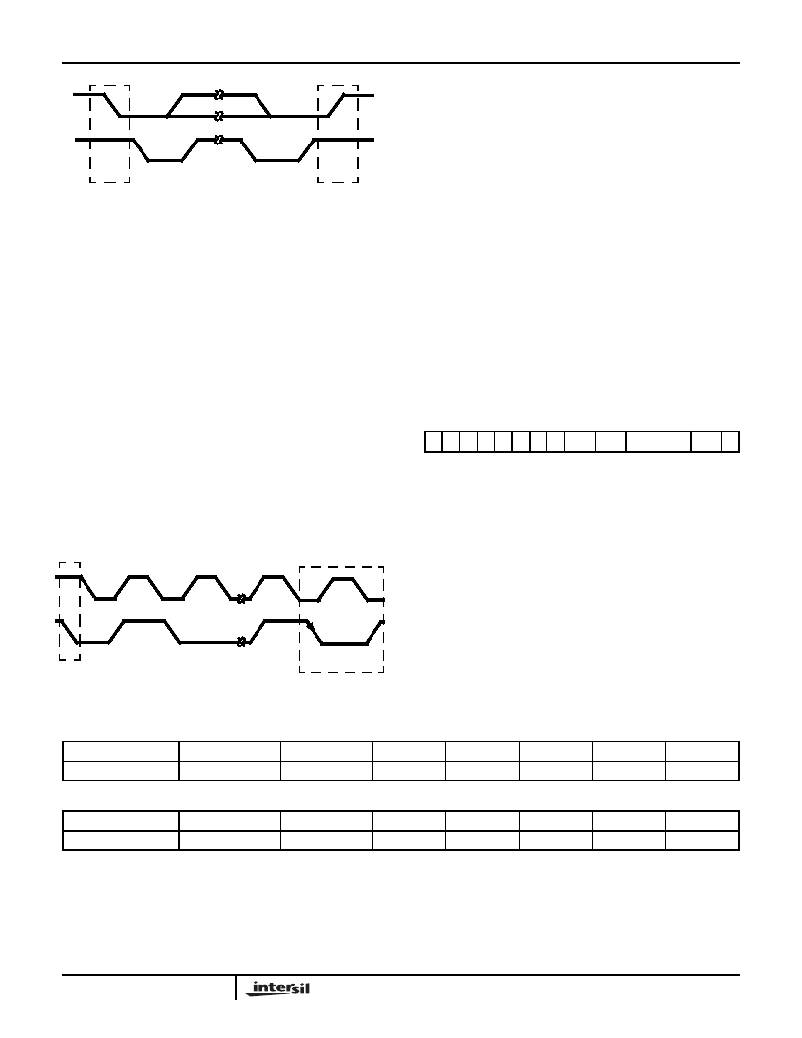

�Acknowledge�

�The� master� (microprocessor)� puts� a� resistive� HIGH� level� on�

�the� SDA� line� during� the� acknowledge� clock� pulse� (Figure� 3).�

�The� peripheral� that� acknowledges� has� to� pull� down� (LOW)�

�the� SDA� line� during� the� acknowledge� clock� pulse,� so� that� the�

�ISL6425� Software� Description�

�Interface� Protocol�

�The� interface� protocol� is� comprised� of� the� following,� as�

�shown� below� in� Table� 2:�

�?� A� start� condition� (S)�

�?� A� chip� address� byte� (MSB� on� left;� the� LSB� bit� determines�

�read� (1)� or� write� (0)� transmission)� (the� assigned� I� 2� C� slave�

�address� for� the� ISL6425� is� 0001� 00XX)�

�?� A� sequence� of� data� (1� byte� +� Acknowledge)�

�?� A� stop� condition� (P)�

�SDA� line� is� stable� LOW� during� this� clock� pulse.� (Of� course,�

�set-up� and� hold� times� must� also� be� taken� into� account.)�

�S�

�0�

�0�

�0�

�TABLE� 2.� INTERFACE� PROTOCOL�

�1� 0� 0� 0� R/W� ACK� Data� (8� bits)� ACK� P�

�The� peripheral� which� has� been� addressed� has� to� generate�

�an� acknowledge� after� the� reception� of� each� byte,� otherwise�

�the� SDA� line� remains� at� the� HIGH� level� during� the� ninth�

�clock� pulse� time.� In� this� case,� the� master� transmitter� can�

�generate� the� STOP� information� in� order� to� abort� the� transfer.�

�The� ISL6425� will� not� generate� the� acknowledge� if� the�

�POWER� OK� signal� from� the� UVLO� is� LOW.�

�SCL�

�Transmitted� Data� (� I� 2� C� bus� WRITE� mode)�

�When� the� R/W� bit� in� the� chip� is� set� to� 0,� the� main�

�microprocessor� can� write� on� the� system� register� (SR1)� of� the�

�ISL6425� via� I� 2� C� bus.� These� will� be� written� by� the�

�microprocessor� as� shown� below.�

�1�

�2�

�8�

�9�

�SDA�

�MSB�

�START�

�ACKNOWLEDGE�

�FROM� SLAVE�

�FIGURE� 3.� ACKNOWLEDGE� ON� THE� I� 2� C� BUS�

�TABLE� 3.� SYSTEM� REGISTER� 1� (SR1)�

�R,� W�

�SR1�

�R,� W�

�DCL�

�R,� W�

�X�

�R,� W�

�ENT1�

�R,� W�

�LLC1�

�R,� W�

�VSEL1�

�R,� W�

�EN1�

�R�

�OLF1�

�TABLE� 4.� SYSTEM� REGISTER� 2� (SR2)�

�R,� W�

�SR2�

�R,� W�

�X�

�R,� W�

�X�

�R,� W�

�X�

�R,� W�

�X�

�R,� W�

�EN2�

�R�

�OTF�

�R�

�X�

�System� Register� Format�

�?� R,� W� =� Read� and� Write� bit�

�?� R� =� Read-only� bit�

�All� bits� reset� to� 0� at� Power-On�

�9�

�FN9176.1�

�February� 8,� 2005�

�相关PDF资料 |

PDF描述 |

|---|---|

| LT3083EQ#PBF | IC REG LDO ADJ 3A 5-DDPAK |

| RCC65DCMI-S288 | CONN EDGECARD 130POS .100 EXTEND |

| ESC31DRTN-S13 | CONN EDGECARD 62POS .100 EXTEND |

| X40011V8I-CT1 | IC VOLTAGE MONITOR DUAL 8-TSSOP |

| AMM10DRUN | CONN EDGECARD 20POS .156 DIP SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6425EVAL2 | 功能描述:EVAL BOARD 2 FOR ISL6425 RoHS:否 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:* 标准包装:75 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:1MHz 占空比:81% 电源电压:4.3 V ~ 13.5 V 降压:是 升压:是 回扫:是 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:无 工作温度:0°C ~ 70°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:管件 产品目录页面:1051 (CN2011-ZH PDF) 其它名称:296-2543-5 |

| ISL6426CB | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| ISL6426CR | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Intersil Corporation 功能描述: |

| ISL6426CV | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Intersil Corporation 功能描述: |

| ISL6426IB | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

发布紧急采购,3分钟左右您将得到回复。