- 您现在的位置:买卖IC网 > PDF目录16601 > ISL6443IR (Intersil)IC CTRLR SGL/STEP DOWN PWM 28QFN PDF资料下载

参数资料

| 型号: | ISL6443IR |

| 厂商: | Intersil |

| 文件页数: | 11/18页 |

| 文件大小: | 0K |

| 描述: | IC CTRLR SGL/STEP DOWN PWM 28QFN |

| 标准包装: | 60 |

| 应用: | 电源 |

| 电流 - 电源: | 50µA |

| 电源电压: | 5.6 V ~ 24 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-VFQFN 裸露焊盘 |

| 供应商设备封装: | 28-QFN 裸露焊盘(5x5) |

| 包装: | 管件 |

�� �

�

�

�ISL6443�

�T� SOFT� =� 0.8V� ?� -----------� ?�

�V� OUTx� =� 0.8V� ?� ----------------------� ?�

�Functional� Description�

�General� Description�

�The� ISL6443� integrates� control� circuits� for� two� synchronous�

�buck� converters� and� one� linear� controller.� The� two�

�synchronous� bucks� operate� out� of� phase� to� substantially�

�reduce� the� input� ripple� and� thus� reduce� the� input� filter�

�requirements.� The� chip� has� four� control� lines� (SS1,� SD1,�

�SS2,� and� SD2),� which� provide� independent� control� for� each�

�of� the� synchronous� buck� outputs.�

�The� buck� PWM� controllers� employ� a� free-running� frequency�

�of� 300kHz.� The� current� mode� control� scheme� with� an� input�

�voltage� feed-forward� ramp� input� to� the� modulator� provides�

�excellent� rejection� of� input� voltage� variations� and� provides�

�simplified� loop� compensations.�

�The� linear� controller� can� drive� either� a� PNP� or� PFET� to� provide�

�ultra� low-dropout� regulation� with� programmable� voltages.�

�Internal� 5V� Linear� Regulator� (VCC_5V)�

�All� ISL6443� functions� are� internally� powered� from� an� on-�

�chip,� low� dropout� 5V� regulator.� The� maximum� regulator� input�

�voltage� is� 24V.� Bypass� the� regulator� ’s� output� (VCC_5V)� with�

�a� 4.7μF� capacitor� to� ground.� The� dropout� voltage� for� this�

�LDO� is� typically� 600mV,� so� when� VCC_5V� is� greater� than�

�5.6V,� VCC_5V� is� typically� 5V.� The� ISL6443� also� employs� an�

�undervoltage� lockout� circuit� that� disables� both� regulators�

�when� VCC_5V� falls� below� 4.4V.�

�The� internal� LDO� can� source� over� 60mA� to� supply� the� IC,�

�power� the� low� side� gate� drivers,� charge� the� external� boot�

�capacitor� and� supply� small� external� loads.� When� driving�

�large� FETs� especially� at� 300kHz� frequency,� little� or� no�

�regulator� current� may� be� available� for� external� loads.�

�For� example,� a� single� large� FET� with� 15nC� total� gate� charge�

�requires� 15nC� x� 300kHz� =� 4.5mA.� Also,� at� higher� input�

�voltages� with� larger� FETs,� the� power� dissipation� across� the�

�internal� 5V� will� increase.� Excessive� dissipation� across� this�

�regulator� must� be� avoided� to� prevent� junction� temperature�

�rise.� Larger� FETs� can� be� used� with� 5V� ±10%� input�

�applications.� The� thermal� overload� protection� circuit� will� be�

�triggered,� if� the� VCC_5V� output� is� short� circuited.� Connect�

�VCC_5V� to� V� IN� for� 5V� ±10%� input� applications.�

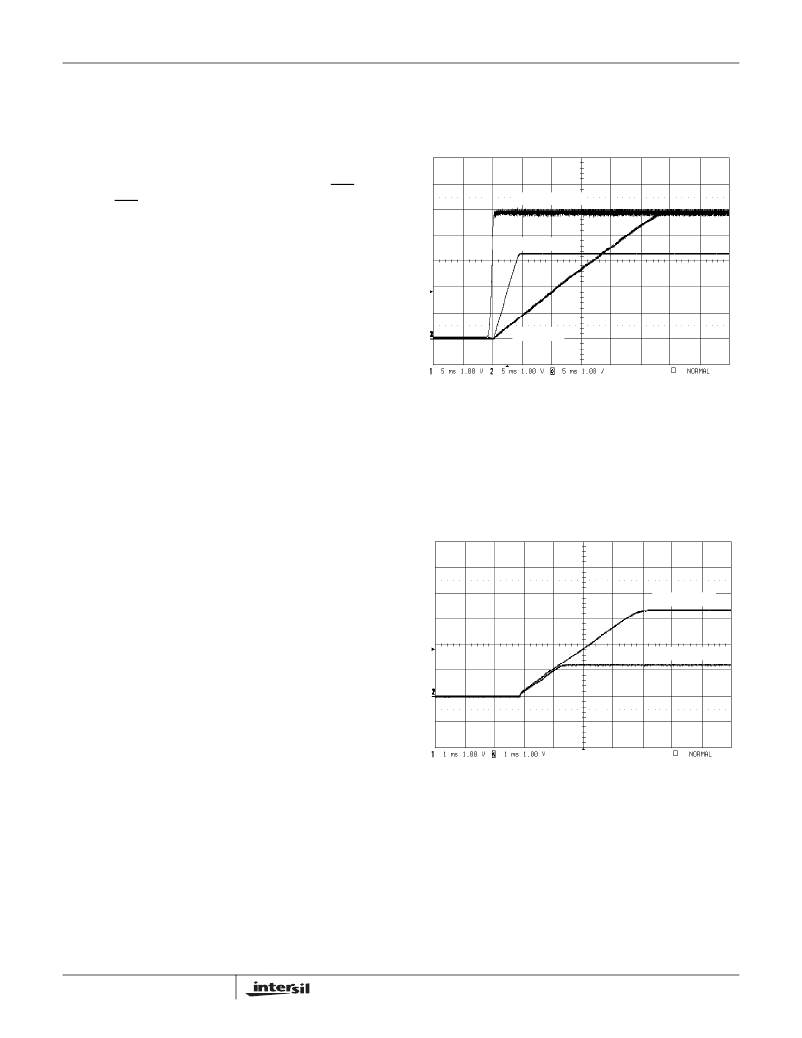

�Soft-Start� Operation�

�When� soft-start� is� initiated,� the� voltage� on� the� SS� pin� of� the�

�enabled� PWM� channels� starts� to� ramp� gradually,� due� to� the�

�5� μ� A� current� sourced� into� the� external� capacitor.� The� output�

�voltage� follows� the� soft-start� voltage.�

�When� the� SS� pin� voltage� reaches� 0.8V,� the� output� voltage� of�

�the� enabled� PWM� channel� reaches� the� regulation� point,� and�

�the� soft-start� pin� voltage� continues� to� rise.� At� this� point� the�

�PGOOD� and� fault� circuitry� is� enabled.� This� completes� the�

�soft-start� sequence.� Any� further� rise� of� SS� pin� voltage� does�

�not� affect� the� output� voltage.� By� varying� the� values� of� the�

�soft-start� capacitors,� it� is� possible� to� provide� sequencing� of� the�

�11�

�main� outputs� at� start-up.� The� soft-start� time� can� be� obtained�

�from� the� following� equation:�

�C� SS�

�?� 5� μ� A� ?�

�VCC_5V 1V/DIV�

�V� OUT1� 1V/DIV�

�SS1 1V/DIV�

�FIGURE� 13.� SOFT-START� OPERATION�

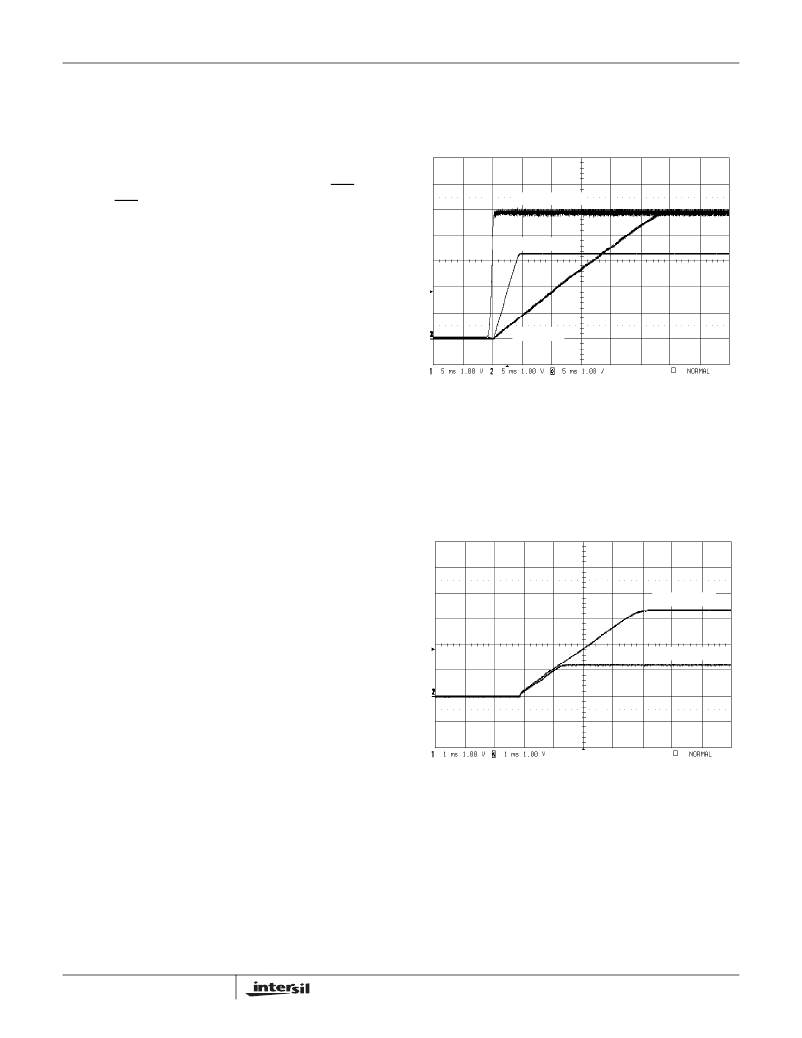

�The� soft-start� capacitors� can� be� chosen� to� provide� startup�

�tracking� for� the� two� PWM� outputs.� This� can� be� achieved� by�

�choosing� the� soft-start� capacitors� such� that� the� soft-start�

�capacitor� ration� equals� the� respective� PWM� output� voltage�

�ratio.� For� example,� if� I� use� PWM1� =� 1.2V� and� PWM2� =� 3.3V�

�then� the� soft-start� capacitor� ratio� should� be,� C� SS1� /C� SS1� =�

�1.2/3.3� =� 0.364.� Figure� 14� shows� that� soft-start� waveform�

�with� C� SS1� =� 0.01μF� and� C� SS2� =� 0.027μF.�

�V� OUT1� 1V/DIV�

�V� OUT2� 1V/DIV�

�FIGURE� 14.� PWM1� AND� PWM2� OUTPUT� TRACKING� DURING�

�STARTUP�

�Output� Voltage� Programming�

�A� resistive� divider� from� the� output� to� ground� sets� the� output�

�voltage� of� either� PWM� channel.� The� center� point� of� the�

�divider� shall� be� connected� to� FBx� pin.� The� output� voltage�

�value� is� determined� by� the� following� equation.�

�R1� +� R2�

�?� R2� ?�

�where� R1� is� the� top� resistor� of� the� feedback� divider� network�

�and� R2� is� the� resistor� connected� from� FBx� to� ground.�

�FN9044.2�

�August� 9,� 2006�

�相关PDF资料 |

PDF描述 |

|---|---|

| IMCSN-3000-25-U | HEAT SHRINK IMCSN 3000 BK 25FT |

| ISL6441IR | IC CTRLR SGL/STEP DOWN PWM 28QFN |

| M2MXH-1040K | IDC CABLE - MDM10H/MC10F/X |

| ISL6271ACR | IC REG PMIC 1BUCK 2LDO 20-QFN |

| GEM18DRTF | CONN EDGECARD 36POS DIP .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6443IR-T | 功能描述:IC CTRLR PWM DUAL 300KHZ 28-QFN RoHS:否 类别:集成电路 (IC) >> PMIC - 电源管理 - 专用 系列:- 应用说明:Ultrasound Imaging Systems Application Note 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:37 系列:- 应用:医疗用超声波成像,声纳 电流 - 电源:- 电源电压:2.37 V ~ 6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:56-WFQFN 裸露焊盘 供应商设备封装:56-TQFN-EP(8x8) 包装:管件 |

| ISL6443IR-TK | 功能描述:IC CTRLR PWM DUAL 300KHZ 28-QFN RoHS:否 类别:集成电路 (IC) >> PMIC - 电源管理 - 专用 系列:- 应用说明:Ultrasound Imaging Systems Application Note 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:37 系列:- 应用:医疗用超声波成像,声纳 电流 - 电源:- 电源电压:2.37 V ~ 6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:56-WFQFN 裸露焊盘 供应商设备封装:56-TQFN-EP(8x8) 包装:管件 |

| ISL6443IRZ | 功能描述:IC CTRLR SGL/STEP DOWN PWM 28QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 电源管理 - 专用 系列:- 应用说明:Ultrasound Imaging Systems Application Note 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:37 系列:- 应用:医疗用超声波成像,声纳 电流 - 电源:- 电源电压:2.37 V ~ 6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:56-WFQFN 裸露焊盘 供应商设备封装:56-TQFN-EP(8x8) 包装:管件 |

| ISL6443IRZS2698 | 制造商:Intersil Corporation 功能描述:LEAD-FREE DUAL PWM CONTROLLER + LINEAR CONTROLLER, 300KHZ, Q - Rail/Tube |

| ISL6443IRZ-T | 功能描述:IC CTRLR PWM DUAL 300KHZ 28-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 电源管理 - 专用 系列:- 应用说明:Ultrasound Imaging Systems Application Note 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:37 系列:- 应用:医疗用超声波成像,声纳 电流 - 电源:- 电源电压:2.37 V ~ 6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:56-WFQFN 裸露焊盘 供应商设备封装:56-TQFN-EP(8x8) 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。