参数资料

| 型号: | ISL6568CRZR5184 |

| 厂商: | Intersil |

| 文件页数: | 16/30页 |

| 文件大小: | 0K |

| 描述: | IC CTRLR PWM 2PHASE BUCK 32-QFN |

| 标准包装: | 60 |

| 应用: | 控制器,Intel VRM9,VRM10,AMD Hammer 应用 |

| 输入电压: | 3 V ~ 12 V |

| 输出数: | 1 |

| 输出电压: | 0.84 V ~ 1.6 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-VFQFN 裸露焊盘 |

| 供应商设备封装: | 32-QFN(5x5) |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页

�� �

�

�

�ISL6568�

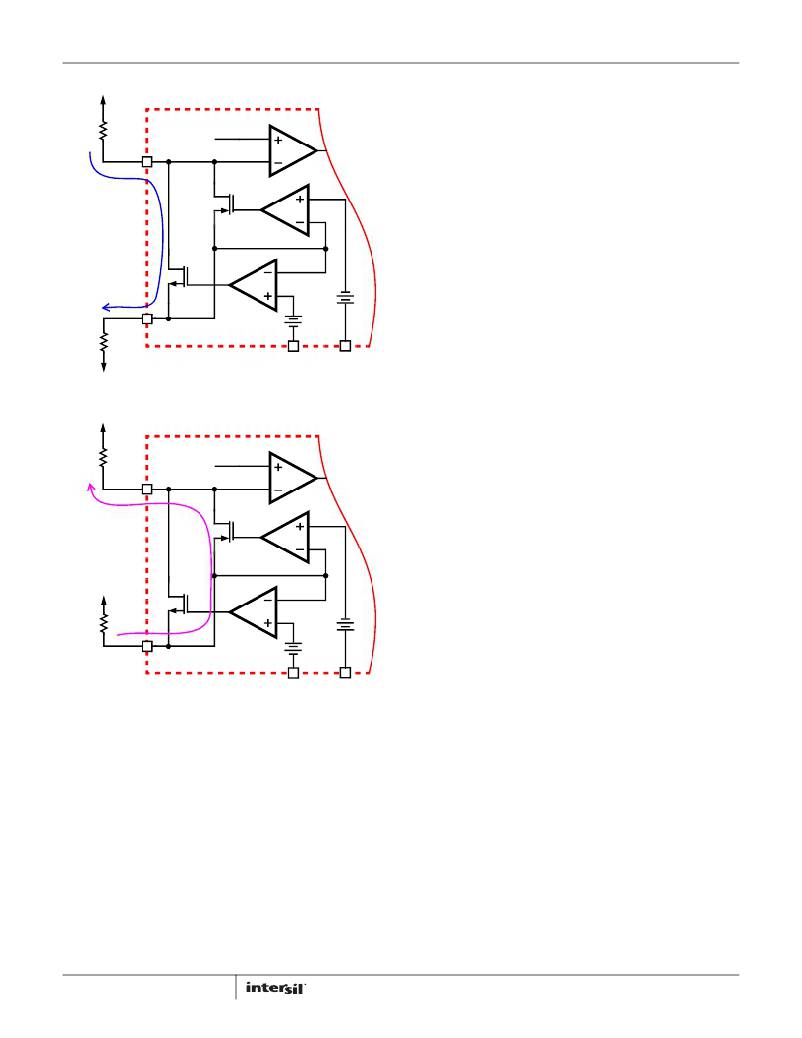

�VDIFF�

�regulator� to� do� this� by� making� changes� to� the� VID� inputs.� The�

�core-voltage� regulator� is� required� to� monitor� the� DAC� inputs� and�

�+�

�V� OFS�

�-�

�R� FB�

�FB�

�I� OFS�

�VREF�

�E/A�

�respond� to� on-the-fly� VID� changes� in� a� controlled� manner,�

�supervising� a� safe� output� voltage� transition� without�

�discontinuity� or� disruption.�

�The� DAC� mode� the� ISL6568� is� operating� in� determines� how� the�

�controller� responds� to� a� dynamic� VID� change.� When� in� VRM10�

�mode� the� ISL6568� checks� the� VID� inputs� six� times� every�

�switching� cycle.� If� a� new� code� is� established� and� it� stays� the�

�same� for� 3� consecutive� readings,� the� ISL6568� recognizes� the�

�change� and� increments� the� reference.� Specific� to� VRM10,� the�

�processor� controls� the� VID� transitions� and� is� responsible� for�

�incrementing� or� decrementing� one� VID� step� at� a� time.� In�

�VRM10� setting,� the� ISL6568� will� immediately� change� the�

�R� OFS�

�OFS�

�ISL6568�

�+�

�-�

�0.5V�

�-�

�+�

�1.5V�

�reference� to� the� new� requested� value� as� soon� as� the� request� is�

�validated;� in� cases� where� the� reference� step� is� too� large,� the�

�sudden� change� can� trigger� overcurrent� or� overvoltage� events.�

�In� order� to� ensure� the� smooth� transition� of� output� voltage�

�GND�

�GND�

�VCC�

�during� a� VRM10� VID� change,� a� VID� step� change� smoothing�

�network� is� required� for� an� ISL6568� based� voltage� regulator.�

�FIGURE� 8.� POSITIVE� OFFSET� OUTPUT� VOLTAGE� PROGRAMMING�

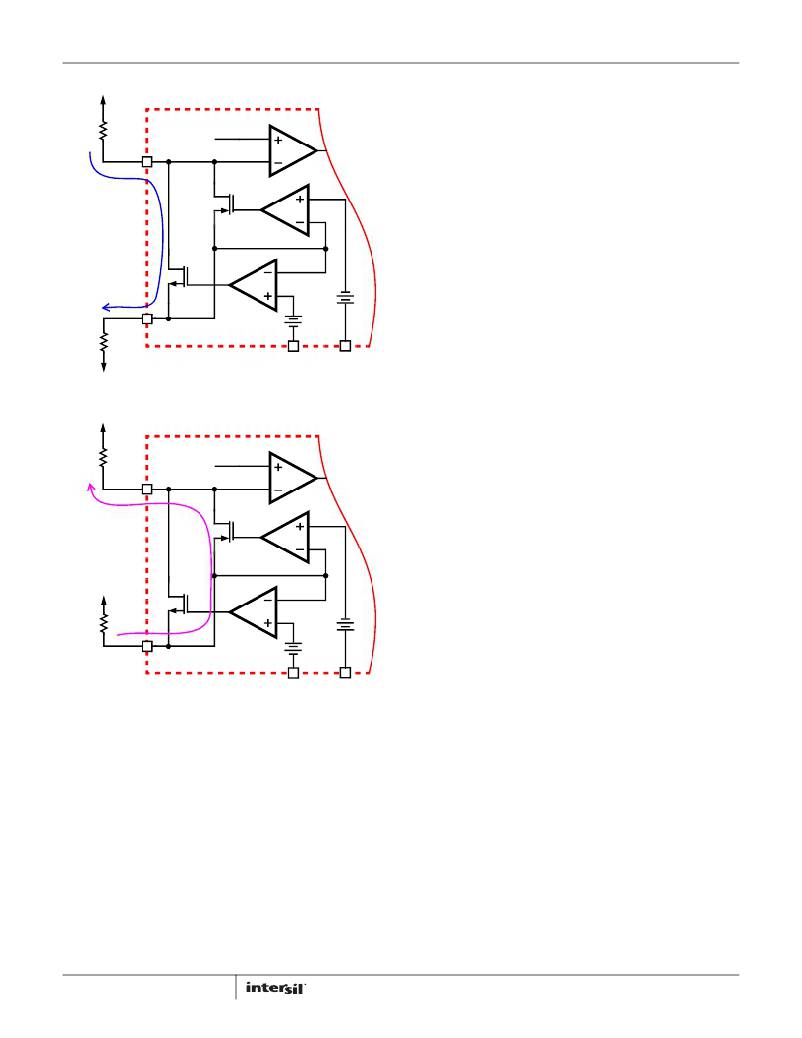

�VDIFF�

�This� network� is� composed� of� a� 1k� Ω� internal� resistor� between�

�the� output� of� DAC� and� the� capacitor� C� REF� ,� between� the� REF� pin�

�and� ground.� The� selection� of� C� REF� is� based� on� the� time�

�duration� for� 1-bit� VID� change� and� the� allowable� delay� time.�

�-�

�V� OFS�

�+�

�R� FB�

�FB�

�VREF�

�E/A�

�Assuming� the� microprocessor� controls� the� VID� change� at� 1-bit�

�every� T� VID� ,� the� relationship� between� C� REF� and� T� VID� is� given� by�

�Equation� 10.�

�C� REF� =� 0.004X� T� VID�

�(EQ.� 10)�

�I� OFS�

�VCC�

�As� an� example,� for� a� VID� step� change� rate� of� 5μs� per� bit,� the�

�value� of� C� REF� is� 22nF� based� on� Equation� 10.�

�When� running� in� VRM9� or� AMD� Hammer� operation,� the� ISL6568�

�responds� slightly� differently� to� a� dynamic� VID� change� than� when�

�in� VRM10� mode.� In� these� modes� the� VID� code� can� be� changed�

�R� OFS�

�+�

�-�

�+�

�1.5V�

�by� more� than� a� 1-bit� step� at� a� time.� Once� the� controller� receives�

�the� new� VID� code� it� waits� half� of� a� phase� cycle� and� then� begins�

�slewing� the� DAC� 12.5mV� every� phase� cycle,� until� the� VID� and�

�OFS�

�0.5� � R� FB�

�R� OFS� =� --------------------------�

�t� DVID� =� -----� ?� ------------------� +� 1.5� ?�

�1� Δ� V� VID�

�f� S� ?� 0.0125�

�?�

�0.5V�

�-�

�ISL6568�

�GND� VCC�

�FIGURE� 9.� NEGATIVE� OFFSET� OUTPUT� VOLTAGE� PROGRAMMING�

�Once� the� desired� output� offset� voltage� has� been� determined,�

�use� formulas� in� Equations� 8� and� 9� to� set� R� OFS� :�

�For� Positive� Offset� (connect� R� OFS� to� GND):�

�(EQ.� 8)�

�V� OFFSET�

�DAC� are� equal.� Thus,� the� total� time� required� for� a� VID� change,�

�t� DVID� ,� is� dependent� on� the� switching� frequency� (f� S� ),� the� size� of�

�the� change� (� Δ� V� VID� ),� and� the� time� required� to� register� the� VID�

�change.� The� one-cycle� addition� in� the� t� DVID� equation� is� due� to� the�

�possibility� that� the� VID� code� change� may� occur� up� to� one� full�

�switching� cycle� before� being� recognized.� The� approximate� time�

�required� for� a� ISL6568-based� converter� in� AMD� Hammer�

�configuration� running� at� f� S� =� 335kHz� to� make� a� 1.1V� to� 1.5V�

�reference� voltage� change� is� about� 100μs,� as� calculated� using�

�Equation� 11.�

�(EQ.� 11)�

�R� OFS� =� --------------------------�

�For� Negative� Offset� (connect� R� OFS� to� VCC):�

�1.5� � R� FB�

�V� OFFSET�

�(EQ.� 9)�

�Advanced� Adaptive� Zero� Shoot-Through�

�Deadtime� Control� (Patent� Pending)�

�The� integrated� drivers� incorporate� a� unique� adaptive� deadtime�

�Dynamic� VID�

�Modern� microprocessors� need� to� make� changes� to� their� core�

�voltage� as� part� of� normal� operation.� They� direct� the� core-voltage�

�16�

�control� technique� to� minimize� deadtime,� resulting� in� high�

�efficiency� from� the� reduced� freewheeling� time� of� the� lower�

�MOSFET� body-diode� conduction,� and� to� prevent� the� upper� and�

�lower� MOSFETs� from� conducting� simultaneously.� This� is�

�FN9187.5�

�January� 12,� 2012�

�相关PDF资料 |

PDF描述 |

|---|---|

| ISL6334ACRZR5368 | IC CTRLR PWM 4PHASE BUCK 40QFN |

| NCP4640H020T1G | IC REG LDO 2V 50MA SOT89-5 |

| ISL6334ACRZ-TR5368 | IC CTRLR PWM 4PHASE BUCK 40QFN |

| LT3015IMSE#PBF | IC REG LDO NEG ADJ 1.5A 12MSOP |

| LT3015ET#PBF | IC REG LDO NEG ADJ 1.5A 5-TO220 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6568CRZ-T | 功能描述:IC CTLR PWM BUCK 2PHASE 32-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,000 系列:- 应用:电源,ICERA E400,E450 输入电压:4.1 V ~ 5.5 V 输出数:10 输出电压:可编程 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:42-WFBGA,WLCSP 供应商设备封装:42-WLP 包装:带卷 (TR) |

| ISL6568CRZ-TKR5184 | 功能描述:IC CTRLR PWM 2PHASE BUCK 32-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 标准包装:43 系列:- 应用:控制器,Intel VR11 输入电压:5 V ~ 12 V 输出数:1 输出电压:0.5 V ~ 1.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘 供应商设备封装:48-QFN(7x7) 包装:管件 |

| ISL6568CRZ-TR5184 | 功能描述:IC CTRLR PWM 2PHASE BUCK 32-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 标准包装:2,000 系列:- 应用:控制器,DSP 输入电压:4.5 V ~ 25 V 输出数:2 输出电压:最低可调至 1.2V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:30-TFSOP(0.173",4.40mm 宽) 供应商设备封装:30-TSSOP 包装:带卷 (TR) |

| ISL6568IR | 功能描述:IC CTRLR PWM BUCK 2PHASE 32-QFN RoHS:否 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,000 系列:- 应用:电源,ICERA E400,E450 输入电压:4.1 V ~ 5.5 V 输出数:10 输出电压:可编程 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:42-WFBGA,WLCSP 供应商设备封装:42-WLP 包装:带卷 (TR) |

| ISL6568IR-T | 功能描述:IC CTRLR PWM BUCK 2PHASE 32-QFN RoHS:否 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,000 系列:- 应用:电源,ICERA E400,E450 输入电压:4.1 V ~ 5.5 V 输出数:10 输出电压:可编程 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:42-WFBGA,WLCSP 供应商设备封装:42-WLP 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。