- 您现在的位置:买卖IC网 > PDF目录20373 > ISL6612IR-T (Intersil)IC MOSFET DRVR SYNC BUCK 10-DFN PDF资料下载

参数资料

| 型号: | ISL6612IR-T |

| 厂商: | Intersil |

| 文件页数: | 9/12页 |

| 文件大小: | 0K |

| 描述: | IC MOSFET DRVR SYNC BUCK 10-DFN |

| 标准包装: | 6,000 |

| 配置: | 高端和低端,同步 |

| 输入类型: | PWM |

| 延迟时间: | 10ns |

| 电流 - 峰: | 1.25A |

| 配置数: | 1 |

| 输出数: | 2 |

| 高端电压 - 最大(自引导启动): | 36V |

| 电源电压: | 10.8 V ~ 13.2 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 10-VFDFN 裸露焊盘 |

| 供应商设备封装: | 10-DFN(3x3) |

| 包装: | 带卷 (TR) |

�� �

�

�

�ISL6612,� ISL6613�

�is� approximately� 800mW� at� room� temperature,� while� the�

�power� dissipation� capacity� in� the� EPSOIC� and� DFN�

�packages,� with� an� exposed� heat� escape� pad,� is� more� than� 2W�

�and� 1.5W,� respectively.� Both� EPSOIC� and� DFN� packages� are�

�UVCC�

�BOOT�

�C� GD�

�D�

�more� suitable� for� high� frequency� applications.� See� “Layout�

�Considerations”� on� page� 9� for� thermal� transfer� improvement�

�suggestions.� When� designing� the� driver� into� an� application,� it�

�is� recommended� that� the� following� calculation� is� used� to�

�ensure� safe� operation� at� the� desired� frequency� for� the�

�R� HI1�

�R� LO1�

�G�

�R� G1�

�R� GI1�

�C� GS�

�S�

�C� DS�

�Q� 1�

�selected� MOSFETs.� The� total� gate� drive� power� losses� due� to�

�the� gate� charge� of� MOSFETs� and� the� driver’s� internal� circuitry�

�and� their� corresponding� average� driver� current� can� be�

�estimated� using� Equation� 2� and� Equation� 3,� respectively,�

�PHASE�

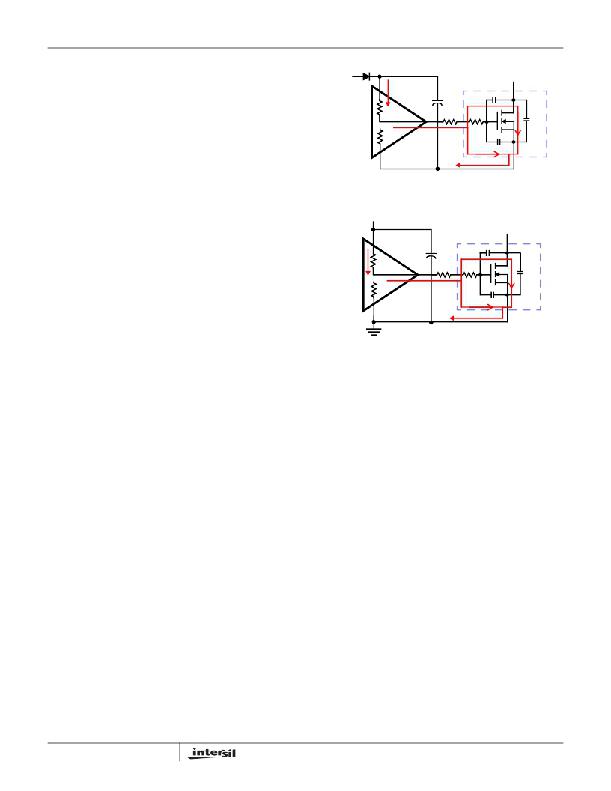

�FIGURE� 3.� TYPICAL� UPPER-GATE� DRIVE� TURN-ON� PATH�

�P� Qg_TOT� =� P� Qg_Q1� +� P� Qg_Q2� +� I� Q� ?� VCC�

�(EQ.� 2)�

�LVCC�

�D�

�Q� G1� ?� UVCC� 2�

�P� Qg_Q1� =� ---------------------------------------� ?� F� SW� ?� N� Q1�

�Q� G2�

�P� Qg_Q2� =� --------------------------------------� ?� F� SW� ?� N� Q2�

�V� GS1�

�?� LVCC� 2�

�V� GS2�

�R� HI2�

�R� LO2�

�G�

�R� G2�

�C� GD�

�R� GI2�

�C� GS�

�C� DS�

�Q� 2�

�?� Q� G1� ?� UVCC� ?� N� Q1� Q� G2� ?� LVCC� ?� N� Q2� ?�

�I� DR� =� ?� ------------------------------------------------------� +� -----------------------------------------------------� ?� ?� F� SW� +� I� Q�

�P� DR_UP� =� ?� --------------------------------------� +� ----------------------------------------� ?� ?� ---------------------�

�R� HI1� +� R� EXT1� R� LO1� +� R� EXT1� ?�

�?�

�P� DR_LOW� =� ?� --------------------------------------� +� ----------------------------------------� ?� ?� ---------------------�

�?� R� HI2� +� R� EXT2� R� LO2� +� R� EXT2� ?�

�?� V� GS1� V� GS2� ?�

�(EQ.� 3)�

�where� the� gate� charge� (Q� G1� and� Q� G2� )� is� defined� at� a�

�particular� gate� to� source� voltage� (V� GS1� and� V� GS2� )� in� the�

�corresponding� MOSFET� data� sheet;� I� Q� is� the� driver� ’s� total�

�quiescent� current� with� no� load� at� both� drive� outputs;� N� Q1�

�and� N� Q2� are� number� of� upper� and� lower� MOSFETs,�

�respectively;� UVCC� and� LVCC� are� the� drive� voltages� for�

�both� upper� and� lower� FETs,� respectively.� The� I� Q*� VCC�

�product� is� the� quiescent� power� of� the� driver� without�

�capacitive� load� and� is� typically� 116mW� at� 300kHz.�

�The� total� gate� drive� power� losses� are� dissipated� among� the�

�resistive� components� along� the� transition� path.� The� drive�

�resistance� dissipates� a� portion� of� the� total� gate� drive� power�

�losses,� the� rest� will� be� dissipated� by� the� external� gate�

�resistors� (R� G1� and� R� G2� )� and� the� internal� gate� resistors� (R� GI1�

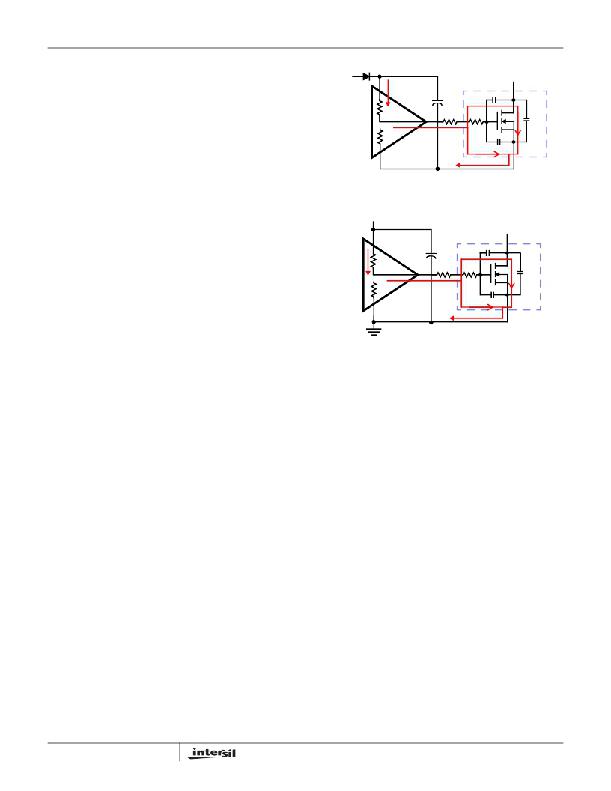

�and� R� GI2� )� of� MOSFETs.� Figures� 3� and� 4� show� the� typical�

�upper� and� lower� gate� drives� turn-on� transition� path.� The�

�power� dissipation� on� the� driver� can� be� roughly� estimated� as:�

�P� DR� =� P� DR_UP� +� P� DR_LOW� +� I� Q� ?� VCC�

�?� R� HI1� R� LO1� ?� P� Qg_Q1�

�2�

�?� R� HI2� R� LO2� ?� P� Qg_Q2�

�2�

�S�

�FIGURE� 4.� TYPICAL� LOWER-GATE� DRIVE� TURN-ON� PATH�

�Layout� Considerations�

�For� heat� spreading,� place� copper� underneath� the� IC� whether�

�it� has� an� exposed� pad� or� not.� The� copper� area� can� be�

�extended� beyond� the� bottom� area� of� the� IC� and/or�

�connected� to� buried� copper� plane(s)� with� thermal� vias.� This�

�combination� of� vias� for� vertical� heat� escape,� extended�

�copper� plane,� and� buried� planes� for� heat� spreading� allows�

�the� IC� to� achieve� its� full� thermal� potential.�

�Place� each� channel� power� component� as� close� to� each�

�other� as� possible� to� reduce� PCB� copper� losses� and� PCB�

�parasitics:� shortest� distance� between� DRAINs� of� upper� FETs�

�and� SOURCEs� of� lower� FETs;� shortest� distance� between�

�DRAINs� of� lower� FETs� and� the� power� ground.� Thus,� smaller�

�amplitudes� of� positive� and� negative� ringing� are� on� the�

�switching� edges� of� the� PHASE� node.� However,� some� space�

�in� between� the� power� components� is� required� for� good�

�airflow.� The� traces� from� the� drivers� to� the� FETs� should� be�

�kept� short� and� wide� to� reduce� the� inductance� of� the� traces�

�and� to� promote� clean� drive� signals.�

�N�

�R� GI1�

�R� EXT1� =� R� G1� +� -------------�

�Q1�

�N�

�R� GI2�

�R� EXT2� =� R� G2� +� -------------�

�Q2�

�(EQ.� 4)�

�9�

�FN9153.9�

�June� 15,� 2010�

�相关PDF资料 |

PDF描述 |

|---|---|

| R2S-123.3 | CONV DC/DC 2W 12VIN 3.3VOUT |

| SDR1005-822KL | INDUCTOR POWER 8200UH SMD |

| ECA10DTAN | CONN EDGECARD 20POS R/A .125 SLD |

| MLG0603S30NJ | INDUCTOR MULTILAYER 30NH 0201 |

| ISL6612IR | IC MOSFET DRVR SYNC BUCK 10-DFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6612IRZ | 功能描述:IC MOSFET DRVR SYNC BUCK 10-DFN RoHS:是 类别:集成电路 (IC) >> PMIC - MOSFET,电桥驱动器 - 外部开关 系列:- 标准包装:6,000 系列:* |

| ISL6612IRZR5238 | 功能描述:IC MOSFET DRVR SYNC BUCK 10-DFN RoHS:是 类别:集成电路 (IC) >> PMIC - MOSFET,电桥驱动器 - 外部开关 系列:- 标准包装:6,000 系列:* |

| ISL6612IRZ-T | 功能描述:IC MOSFET DRVR SYNC BUCK 10-DFN RoHS:是 类别:集成电路 (IC) >> PMIC - MOSFET,电桥驱动器 - 外部开关 系列:- 标准包装:6,000 系列:* |

| ISL6612IRZ-TR5238 | 功能描述:IC MOSFET DRVR SYNC BUCK 10-DFN RoHS:是 类别:集成电路 (IC) >> PMIC - MOSFET,电桥驱动器 - 外部开关 系列:- 标准包装:6,000 系列:* |

| ISL6613ACB | 功能描述:IC MOSFET DRVR SYNC BUCK 8-SOIC RoHS:否 类别:集成电路 (IC) >> PMIC - MOSFET,电桥驱动器 - 外部开关 系列:- 标准包装:50 系列:- 配置:低端 输入类型:非反相 延迟时间:40ns 电流 - 峰:9A 配置数:1 输出数:1 高端电压 - 最大(自引导启动):- 电源电压:4.5 V ~ 35 V 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:TO-263-6,D²Pak(5 引线+接片),TO-263BA 供应商设备封装:TO-263 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。