参数资料

| 型号: | ISL6726AAZ-T7A |

| 厂商: | Intersil |

| 文件页数: | 2/20页 |

| 文件大小: | 0K |

| 描述: | IC REG CTRLR ISO PWM CM 20-QSOP |

| 标准包装: | 250 |

| PWM 型: | 电流模式 |

| 输出数: | 1 |

| 频率 - 最大: | 2MHz |

| 占空比: | 100% |

| 电源电压: | 9 V ~ 16 V |

| 降压: | 无 |

| 升压: | 无 |

| 回扫: | 无 |

| 反相: | 无 |

| 倍增器: | 无 |

| 除法器: | 无 |

| Cuk: | 无 |

| 隔离: | 是 |

| 工作温度: | -40°C ~ 105°C |

| 封装/外壳: | 20-SSOP(0.154",3.90mm 宽) |

| 包装: | 带卷 (TR) |

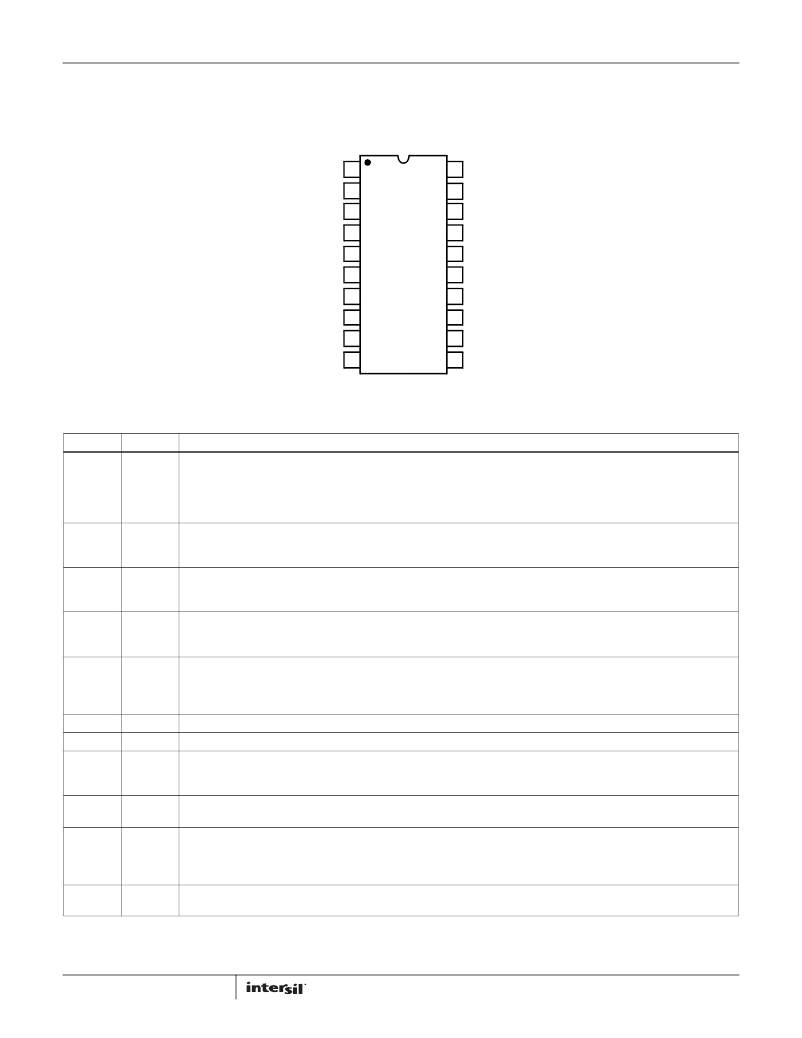

�� �

�

�

�ISL6726�

�Pin� Configuration�

�ISL6726�

�(20� LD� QSOP)�

�TOP� VIEW�

�SYNC�

�DCLIM�

�UV�

�ENABLE�

�RTC�

�CT�

�ISET�

�VERR�

�FB�

�1�

�2�

�3�

�4�

�5�

�6�

�7�

�8�

�9�

�20�

�19�

�18�

�17�

�16�

�15�

�14�

�13�

�12�

�SS�

�MODE�

�DELAY�

�VREF�

�GND�

�OUTM�

�VDD�

�OUTAC�

�SLOPE�

�Pin� Descriptions�

�CS� 10�

�11�

�IOUT�

�PIN� #�

�1�

�2�

�3�

�4�

�5�

�6�

�7�

�8�

�9�

�10�

�11�

�SYMBOL�

�SYNC�

�DCLIM�

�UV�

�ENABLE�

�RTC�

�CT�

�ISET�

�VERR�

�FB�

�CS�

�IOUT�

�DESCRIPTION�

�A� bi-directional� edge-sensitive� signal� used� to� synchronize� multiple� devices� together.� If� the� SYNC� pins� of� two� units� are� connected,� they�

�will� synchronize� 180� degrees� out� of� phase� with� each� other.� This� feature� facilitates� the� design� of� interleaved� topologies.� If� more� than�

�two� units� are� connected,� one� will� be� the� master� unit� and� the� rest� will� be� slave� units.� All� of� the� slave� units� will� synchronize� 180� degrees�

�out-of-phase� with� the� master.� The� master� designation� is� not� fixed� or� predetermined� and� is� self-arbitrating.� The� master� is� determined�

�by� the� fastest� running� oscillator� on� a� dynamic� basis.� SYNC� may� also� be� used� to� synchronize� to� an� external� clock.�

�Used� in� conjunction� with� UV,� DCLIM� creates� a� duty� cycle� clamp� that� is� dependent� on� the� input� voltage.� As� the� input� voltage� increases,�

�the� maximum� allowed� duty� cycle� decreases.� This� feature� is� necessary� in� the� active� clamp� forward� to� help� prevent� transformer� core�

�saturation� during� transients.� A� resistor� divider� from� VREF� sets� the� threshold� of� DCLIM.�

�Sets� the� user� programmable� undervoltage� threshold.� Placing� a� resistor� divider� from� the� input� voltage� to� ground� and� set� to� 1.00V�

�determines� the� minimum� operating� voltage.� The� amount� of� hysteresis� is� determined� by� an� internal� current� source� and� set� by� the�

�external� impedance� of� the� divider.� The� current� source� is� active� when� UV� is� below� 1V.�

�A� logic� level� signal� used� to� enable� the� IC.� When� the� input� is� open,� the� IC� is� enabled� and� a� soft-start� cycle� begins� if� no� fault� conditions�

�are� present.� When� pulled� low,� the� outputs� are� disabled� and� the� IC� enters� a� low� power� sleep� state.� If� soft-stop� is� enabled,� a� logic� “0”�

�on� ENABLE� forces� a� soft-stop� prior� to� entering� the� low� power� sleep� state.�

�The� oscillator� timing� capacitor� charge/discharge� current� control� pin.� A� resistor� is� connected� between� this� pin� and� GND� and�

�determines� the� magnitude� of� the� charge� and� discharge� current.� The� charge� current� is� nominally� 2x� the� current� flowing� into� the�

�resistor.� The� discharge� current� is� nominally� 8x� the� current� flowing� into� the� resistor.� The� ratio� of� the� charge� to� discharge� current� is�

�fixed� and� sets� the� maximum� duty� cycle� at� 80%.�

�The� oscillator� timing� capacitor� is� connected� between� this� pin� and� GND.�

�Controls� the� peak� and� average� current� limit� thresholds.� A� voltage� up� to� 1.0V� may� be� applied� to� ISET.�

�The� error� voltage� input� to� the� PWM� comparator� and� the� compensation� connection� for� the� average� current� loop� control.� VERR�

�requires� an� external� pull-up� resistor� to� VREF.� A� typical� application� connects� the� photo-transistor� output� of� an� opto-coupler� between�

�VERR� and� GND.�

�FB� is� the� inverting� input� to� the� average� current� error� amplifier� (IEA).� The� amplifier� is� used� as� the� error� amplifier� for� the� average�

�current� limit� control� loop.� If� the� amplifier� is� not� used,� FB� should� be� grounded.� The� amplifier� is� normally� configured� as� an� integrator.�

�The� current� sense� input� to� the� IC.� Provides� information� to� the� PWM,� the� peak� overcurrent� protection� comparators,� and� the� average�

�current� limit� circuitry.� The� CS� pin� is� shorted� to� GND� when� the� PWM� output� pulse� terminates.� Depending� on� the� current� sensing�

�source� impedance,� a� series� input� resistor� may� be� required� due� to� the� delay� between� the� internal� logic� and� the� turn� off� of� the� external�

�power� switch.�

�Output� of� the� sample� and� hold� buffer� amplifier� that� captures� and� averages� the� CS� signal.� With� a� nominal� 4x� multiplier� and� the� ability�

�to� scale� the� signal� externally� with� a� resistor� divider,� the� average� current� limit� can� be� set� independently� of� the� peak� current� limit.�

�2�

�FN7654.0�

�January� 31,� 2011�

�相关PDF资料 |

PDF描述 |

|---|---|

| ISL6729IU-T | IC REG CTRLR BST FLYBK ISO 8MSOP |

| ISL6740AIVZA | IC REG CTRLR PWM VM 16-TSSOP |

| ISL6741IV-T | IC REG CTRLR PWM CM 16-TSSOP |

| ISL6742AAZA-T | IC REG CTRLR PWM CM/VM 16-QSOP |

| ISL6744AABZ | IC REG CTRLR PWM VM 8-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6726EVAL1Z | 制造商:Intersil Corporation 功能描述:ISL6726 EVALUATION BOARD 1 - 20 LD QSOP - ROHS COMPLIAN - Bulk 制造商:Intersil Corporation 功能描述:BOARD EVAL FOR ISL6726 制造商:Intersil Corporation 功能描述:ISL6726 EVALUATION BOARD 1 - 20 Ld QSOP - ROHS COMPLIAN |

| ISL6729IB | 功能描述:IC REG CTRLR BST FLYBK ISO 8SOIC RoHS:否 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:500kHz 占空比:100% 电源电压:8.2 V ~ 30 V 降压:无 升压:无 回扫:是 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:0°C ~ 70°C 封装/外壳:8-DIP(0.300",7.62mm) 包装:管件 产品目录页面:1316 (CN2011-ZH PDF) |

| ISL6729IB-T | 功能描述:IC REG CTRLR BST FLYBK ISO 8SOIC RoHS:否 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:500kHz 占空比:100% 电源电压:8.2 V ~ 30 V 降压:无 升压:无 回扫:是 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:0°C ~ 70°C 封装/外壳:8-DIP(0.300",7.62mm) 包装:管件 产品目录页面:1316 (CN2011-ZH PDF) |

| ISL6729IBZ | 功能描述:IC REG CTRLR BST FLYBK ISO 8SOIC RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

| ISL6729IBZ-T | 功能描述:IC REG CTRLR BST FLYBK ISO 8SOIC RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。