- 您现在的位置:买卖IC网 > PDF目录20673 > ISL870XEVAL1 (Intersil)EVAL BOARD 1 FOR ISL870X PDF资料下载

参数资料

| 型号: | ISL870XEVAL1 |

| 厂商: | Intersil |

| 文件页数: | 9/13页 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD 1 FOR ISL870X |

| 标准包装: | 1 |

| 系列: | * |

�� �

�

�

�ISL8700,� ISL8701,� ISL8702�

�Applications� Usage�

�Using� the� ISL870xEVAL1� Platform�

�The� ISL870xEVAL1� platform� is� the� primary� evaluation� board�

�for� this� family� of� sequencers.� See� Figure� 15� for� a� photograph�

�and� schematic.The� evaluation� board� is� shipped� with� an�

�ISL8702� mounted� in� the� left� position� and� with� the� other�

�device� variants� loosely� packed.� In� the� following� discussion,�

�test� points� names� are� bold� on� initial� occurrence� for�

�identification.�

�The� V� IN� test� point� is� the� chip� bias� and� can� be� biased� from�

�2.5V� to� 24V.� The� VHI� test� point� is� for� the� ENABLE� and�

�FAULT� pull-up� voltage� which� are� limited� to� a� maximum� of�

�24V� independent� of� V� IN� .� The� UV/OV� resistor� divider� is� set� so�

�that� a� nominal� 12V� on� the� VMONITOR� test� point� is� compliant�

�and� with� a� rising� OV� set� at� 13.2V� and� a� falling� UV� set� at�

�10.7V.� These� three� test� points� (V� IN� ,VHI� and� VMONITOR)�

�are� brought� out� separately� for� maximum� flexibility� in�

�evaluation.�

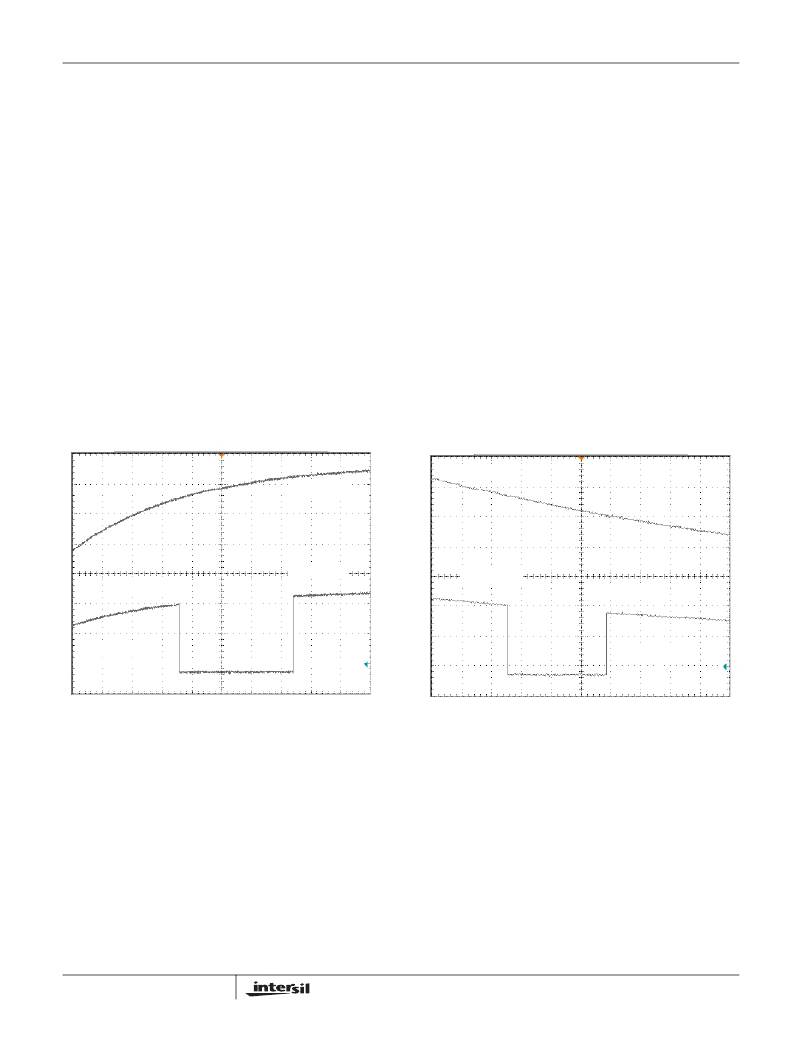

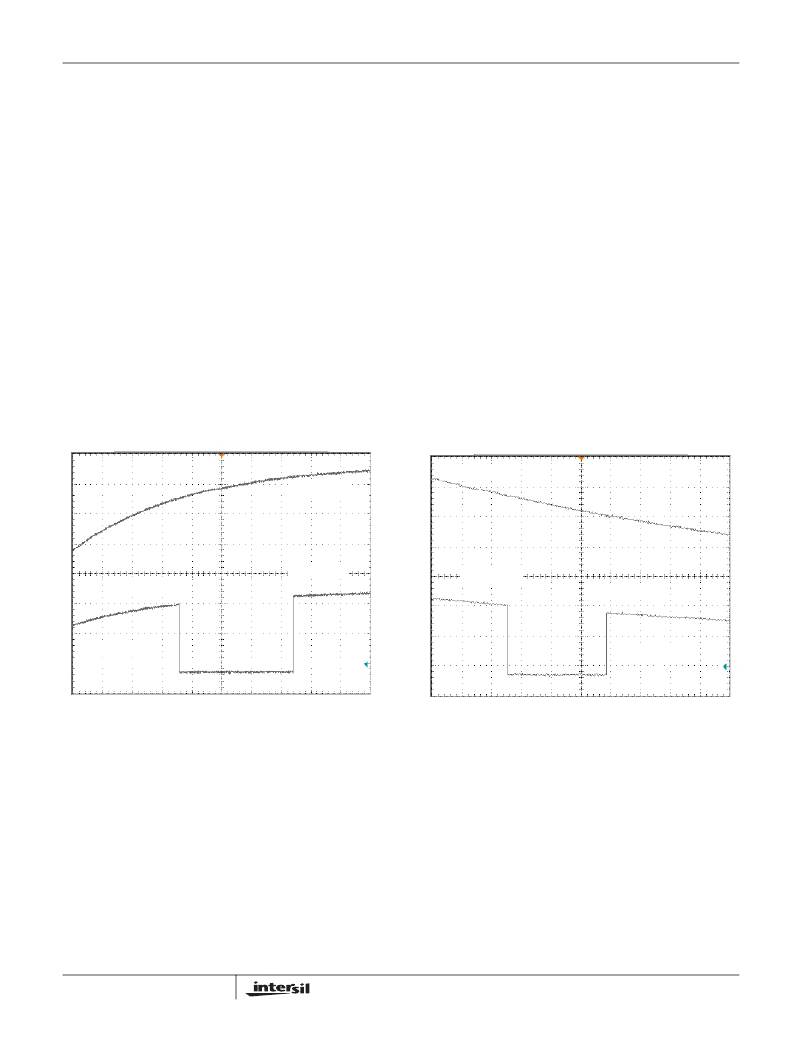

�VMONITOR� ramping� up� and� down� through� the� UV� and� OV�

�levels� will� result� in� the� FAULT� output� signaling� the� out� of�

�bound� conditions� by� being� released� to� pull� high� to� the� VHI�

�voltage� as� shown� in� Figures� 6� and� 7.�

�Once� the� voltage� monitoring� FAULT� is� resolved� and� where�

�applicable,� the� SEQ_EN� (#)� is� satisfied,� sequencing� of� the�

�ENABLE_X(#)� outputs� begins.� When� sequence� enabled� the�

�ENABLE_A� ,� ENABLE_B� ,� ENABLE_C� and� lastly�

�ENABLE_D� are� asserted� in� that� order� and� when� SEQ_EN� is�

�disabled,� the� order� is� reversed.� See� Figures� 8� and� 9�

�demonstrating� the� sequenced� enabling� and� disabling� of� the�

�ENABLE� outputs.� The� timing� between� ENABLE� outputs� is�

�set� by� the� resistor� values� on� the� TB,� TC,� TD� pins� as� shown.�

�Figure� 10� illustrates� the� timing� from� either� SEQ_EN� and/or�

�VMONITOR� being� valid� to� ENABLE_A� being� asserted� with� a�

�10nF� TIME� capacitor.� Figure� 11� shows� that� ENABLE_X�

�outputs� are� pulled� low� even� before� V� IN� =� 1V.� This� is� critical�

�to� ensure� that� a� false� enable� is� not� signaled.� Figure� 12�

�shows� the� time� from� SEQ_EN� transition� with� the� voltage�

�ramping� across� the� TIME� capacitor� to� TIME� Vth� being� met.�

�This� results� in� the� immediate� pull� down� of� the� TIME� pin� and�

�simultaneous� ENABLE_A� enabling.� Figure� 13� illustrates� the�

�immunity� of� the� UV� and� OV� inputs� to� transients.�

�VMON� FALLING�

�VMON� RISING�

�VMON� >� UV�

�LEVEL�

�VMON� >� OV�

�LEVEL�

�VMON� >� OV�

�LEVEL�

�VMON� >� UV�

�LEVEL�

�FAULT� OUTPUT�

�FIGURE� 6.� VMONITOR� RISING� TO� FAULT�

�9�

�FAULT� OUTPUT�

�FIGURE� 7.� VMONITOR� FALLING� TO� FAULT�

�FN9250.2�

�March� 21,� 2008�

�相关PDF资料 |

PDF描述 |

|---|---|

| T95Z106K035CZAL | CAP TANT 10UF 35V 10% 2910 |

| ISL6754DBEVAL1Z | BOARD DEMO FOR ISL6754 |

| C0603C0G1E6R2D | CAP CER 6.2PF 25V NP0 0201 |

| VI-J63-CX-F4 | CONVERTER MOD DC/DC 24V 75W |

| ISL6612ACBZA-T | IC MOSFET DRVR SYNC BUCK 8-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL8723EVAL1 | 功能描述:EVAL BOARD 1 FOR ISL8723 RoHS:否 类别:编程器,开发系统 >> 评估演示板和套件 系列:* 标准包装:1 系列:PSoC® 主要目的:电源管理,热管理 嵌入式:- 已用 IC / 零件:- 主要属性:- 次要属性:- 已供物品:板,CD,电源 |

| ISL8723IRZ | 功能描述:IC POWER SUPPLY SEQUENCER 24QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 电源控制器,监视器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 应用:多相控制器 输入电压:- 电源电压:9 V ~ 14 V 电流 - 电源:- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:40-WFQFN 裸露焊盘 供应商设备封装:40-TQFN-EP(5x5) 包装:带卷 (TR) |

| ISL8723IRZR5369 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Intersil Corporation 功能描述: |

| ISL8723IRZ-T | 功能描述:IC POWER SUPPLY SEQUENCER 24QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 电源控制器,监视器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 应用:多相控制器 输入电压:- 电源电压:9 V ~ 14 V 电流 - 电源:- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:40-WFQFN 裸露焊盘 供应商设备封装:40-TQFN-EP(5x5) 包装:带卷 (TR) |

| ISL8723IRZ-TR5369 | 制造商:Intersil Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。