- 您现在的位置:买卖IC网 > PDF目录20648 > ISL89412IPZ (Intersil)IC DVR MOSFET DUAL-CH 8-PDIP PDF资料下载

参数资料

| 型号: | ISL89412IPZ |

| 厂商: | Intersil |

| 文件页数: | 8/10页 |

| 文件大小: | 0K |

| 描述: | IC DVR MOSFET DUAL-CH 8-PDIP |

| 标准包装: | 50 |

| 配置: | 高端和低端,同步 |

| 输入类型: | 反相和非反相 |

| 延迟时间: | 18ns |

| 电流 - 峰: | 2A |

| 配置数: | 1 |

| 输出数: | 2 |

| 电源电压: | 4.5 V ~ 18 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 通孔 |

| 封装/外壳: | 8-DIP(0.300",7.62mm) |

| 供应商设备封装: | 8-PDIP |

| 包装: | 管件 |

�� �

�

�

�ISL89410,� ISL89411,� ISL89412�

�.subckt� comp1� out� inp� inm� vss�

�e1� out� vss� table� {� (v(inp)� v(inm))*� 5000}� (0,0)� (3.2,3.2)�

�Rout� out� vss� 10meg�

�V+�

�Rinp� inp� vss� 10meg�

�Rinm� inm� vss� 10meg�

�.ends� comp1�

�Application� Guidelines�

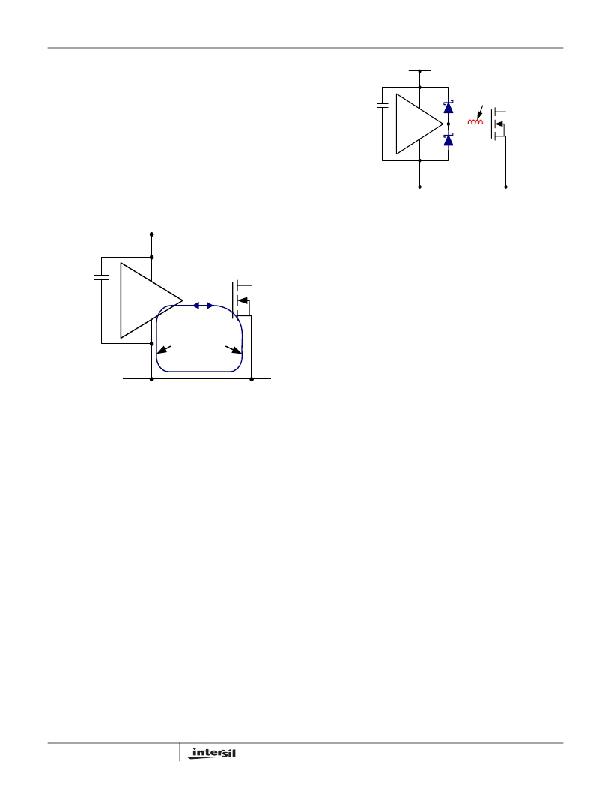

�It� is� important� to� minimize� inductance� to� the� power� FET� by�

�keeping� the� output� drive� current� loop� as� short� as� possible.�

�Also,� the� decoupling� capacitor,� Cq,� should� be� a� high� quality�

�ceramic� capacitor� with� a� Q� that� should� be� a� least� 10x� the�

�gate� Q� of� the� power� FET.� A� ground� plane� under� this� circuit� is�

�C� q�

�GND�

�PARASITIC� LEAD�

�INDUCTANCE�

�also� recommended.�

�C� q�

�V+�

�C� q� SHOULD� BE� AS� CLOSE� AS�

�POSSIBLE� TO� THE� V+� AND�

�GND� PINS�

�LOOP� AS�

�FIGURE� 15.� SUGGESTED� CONFIGURATION� FOR� DRIVING�

�INDUCTIVE� LOADS�

�Where� high� supply� voltage� operation� is� required� (15V� to�

�18V),� input� signals� with� a� minimum� of� 3.3V� input� drive� is�

�suggested� and� a� minimum� rise/fall� time� of� 100ns.� This� is�

�recommended� to� minimize� the� internal� bias� current� power�

�dissipation.�

�Excessive� power� dissipation� in� the� driver� can� result� when�

�driving� highly� capacitive� FET� gates� at� high� frequencies.�

�These� gate� power� losses� are� defined� by� Equation� 1:�

�SHORT� AS�

�POSSIBLE�

�GND�

�FIGURE� 14.� RECOMMENDED� LAYOUT� METHODS�

�P� =� 2� ?� Q� C� ?� V� gs� ?� f� SW�

�where:�

�P� =� Power�

�Q� c� =� Charge� of� the� Power� FET� at� V� gs�

�(EQ.� 1)�

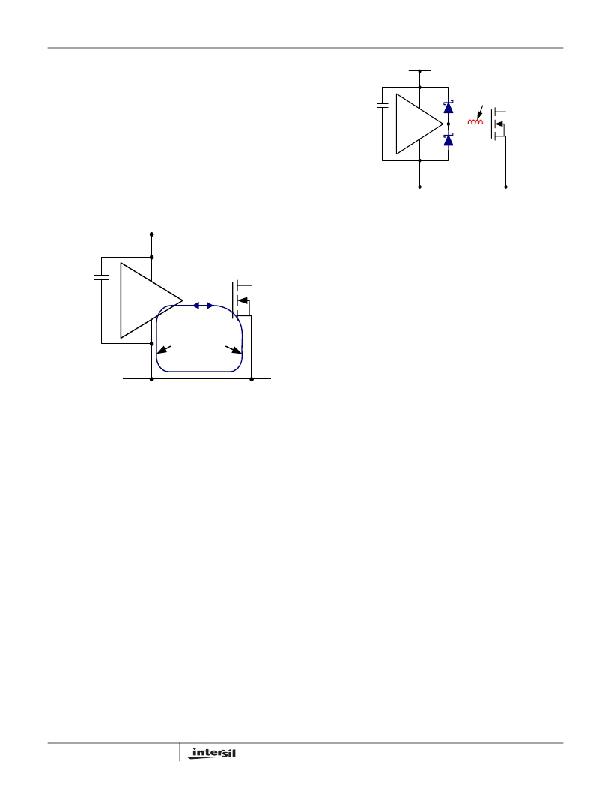

�In� applications� where� it� is� difficult� to� place� the� driver� very�

�close� to� the� power� FET� (which� may� result� with� excessive�

�parasitic� inductance),� it� then� may� be� necessary� to� add� an�

�external� gate� resistor� to� dampen� the� inductive� ring.� If� this�

�resistor� must� be� too� large� in� value� to� be� effective,� then� as� an�

�alternative,� Schottky� diodes� can� be� added� to� clamp� the� ring�

�voltage� to� V+� or� GND.�

�8�

�V� gs� =� Gate� drive� voltage� (V+)�

�f� SW� =� switching� Frequency�

�Adding� a� gate� resistor� to� the� output� of� the� driver� will� transfer�

�some� of� the� driver� dissipation� to� the� resistor.� Another�

�possible� solution� is� to� lower� the� gate� driver� voltage� which�

�also� lowers� Q� c� .�

�FN6798.1�

�July� 1,� 2009�

�相关PDF资料 |

PDF描述 |

|---|---|

| VE-J6V-CX-F2 | CONVERTER MOD DC/DC 5.8V 75W |

| 0834219039 | 9POS CMD TO 9 SKT DSUB 18" CBL |

| VE-BNV-EU-F2 | CONVERTER MOD DC/DC 5.8V 200W |

| EMC05DRTH-S13 | CONN EDGECARD 10POS .100 EXTEND |

| VE-BNT-EU-F4 | CONVERTER MOD DC/DC 6.5V 200W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL9000 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Dual LDO with Low Noise, Very High PSRR, and Low IQ |

| ISL9000_06 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Dual LDO with Low Noise, Very High PSRR, and Low IQ |

| ISL9000A | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Dual LDO with Low Noise, Very High PSRR and Low IQ |

| ISL9000AIRBBZ | 功能描述:IC REG LDO 1.5V .3A 10-DFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 线性 系列:- 标准包装:1 系列:- 稳压器拓扑结构:正,可调式 输出电压:1.25 V ~ 10 V 输入电压:2.9 V ~ 12 V 电压 - 压降(标准):- 稳压器数量:1 电流 - 输出:700mA 电流 - 限制(最小):- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:10-VFDFN 裸露焊盘 供应商设备封装:10-DFN(3x3) 包装:Digi-Reel® 其它名称:NCV8535MNADJR2GOSDKR |

| ISL9000AIRBBZ-T | 功能描述:IC REG LDO 1.5V .3A 10-DFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 线性 系列:- 标准包装:1 系列:- 稳压器拓扑结构:正,可调式 输出电压:1.25 V ~ 10 V 输入电压:2.9 V ~ 12 V 电压 - 压降(标准):- 稳压器数量:1 电流 - 输出:700mA 电流 - 限制(最小):- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:10-VFDFN 裸露焊盘 供应商设备封装:10-DFN(3x3) 包装:Digi-Reel® 其它名称:NCV8535MNADJR2GOSDKR |

发布紧急采购,3分钟左右您将得到回复。