- 您现在的位置:买卖IC网 > PDF目录20048 > ISL9011IRMNZ (Intersil)IC REG LDO 3V/3.3V 10-DFN PDF资料下载

参数资料

| 型号: | ISL9011IRMNZ |

| 厂商: | Intersil |

| 文件页数: | 9/11页 |

| 文件大小: | 0K |

| 描述: | IC REG LDO 3V/3.3V 10-DFN |

| 标准包装: | 100 |

| 稳压器拓扑结构: | 正,固定式 |

| 输出电压: | 3V,3.3V |

| 输入电压: | 2.3 V ~ 6.5 V |

| 电压 - 压降(标准): | 0.125V @ 150mA,0.2V @ 300mA |

| 稳压器数量: | 2 |

| 电流 - 输出: | 150mA(最小),300mA(最小) |

| 电流 - 限制(最小): | 350mA |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 10-VFDFN 裸露焊盘 |

| 供应商设备封装: | 10-DFN(3x3) |

| 包装: | 管件 |

�� �

�

�

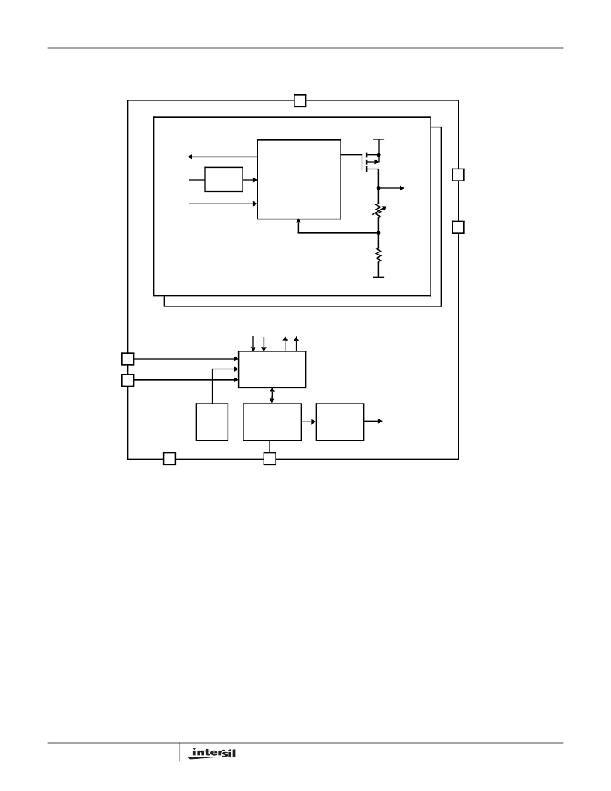

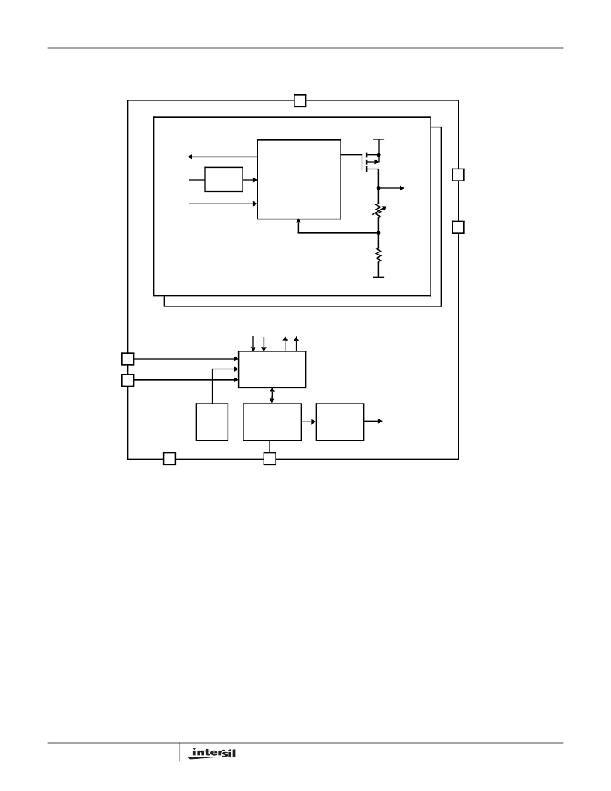

�ISL9011�

�Block� Diagram�

�VIN�

�IS1�

�1V�

�VREF�

�TRIM�

�LDO�

�ERROR�

�AMPLIFIER�

�VO1�

�VO1�

�QEN1�

�LDO-1�

�LDO-2�

�~1.0V�

�VO2�

�EN1�

�EN2�

�CONTROL�

�LOGIC�

�BANDGAP� AND�

�VOLTAGE�

�UVLO�

�TEMPERATURE�

�SENSOR�

�REFERENCE�

�GENERATOR�

�1.00V�

�GND�

�Functional� Description�

�CBYP�

�mode.� During� this� condition,� all� on-chip� circuits� are� off,� and�

�The� ISL9011� contains� all� circuitry� required� to� implement� two�

�high� performance� LDO’s.� High� performance� is� achieved�

�through� a� circuit� that� delivers� fast� transient� response� to�

�varying� load� conditions.� In� a� quiescent� condition,� the�

�ISL9011� adjusts� its� biasing� to� achieve� the� lowest� standby�

�current� consumption.�

�The� device� also� integrates� current� limit� protection,� smart�

�thermal� shutdown� protection,� staged� turn-on� and� soft-start.�

�Smart� Thermal� shutdown� protects� the� device� against�

�overheating.� Staged� turn-on� and� soft-start� minimize� start-up�

�input� current� surges� without� causing� excessive� device�

�turn-on� time.�

�Power� Control�

�The� ISL9011� has� two� separate� enable� pins� (EN1� and� EN2)�

�to� individually� control� power� to� each� of� the� LDO� outputs.�

�When� both� EN1� and� EN2� are� low,� the� device� is� in� shutdown�

�9�

�the� device� draws� minimum� current,� typically� less� than� 0.1μA.�

�When� one� or� both� of� the� enable� pins� are� asserted,� the�

�device� first� polls� the� output� of� the� UVLO� detector� to� ensure�

�that� VIN� voltage� is� at� least� about� 2.1V.� Once� verified,� the�

�device� initiates� a� start-up� sequence.� During� the� start-up�

�sequence,� trim� settings� are� first� read� and� latched.� Then,�

�sequentially,� the� bandgap,� reference� voltage� and� current�

�generation� circuitry� power-up.� Once� the� references� are�

�stable,� a� fast-start� circuit� quickly� charges� the� external�

�reference� bypass� capacitor� (connected� to� the� CBYP� pin)� to�

�the� proper� operating� voltage.� After� the� bypass� capacitor� has�

�been� charged,� the� LDO’s� power-up.�

�If� EN1� is� brought� high,� and� EN2� goes� high� before� the� VO1�

�output� stabilizes,� the� ISL9011� delays� the� VO2� turn-on� until�

�the� VO1� output� reaches� its� target� level.�

�FN9219.5�

�March� 10,� 2008�

�相关PDF资料 |

PDF描述 |

|---|---|

| EEC08DREH-S734 | CONN EDGECARD 16POS .100 EYELET |

| ECA10DTKI-S288 | CONN EDGECARD 20POS .125 EXTEND |

| MENB1060A1203N01 | POWER SUPPLY SWITCHER 60W 12V |

| EBM15DSES-S243 | CONN EDGECARD 30POS .156 EYELET |

| NCP694DSAN25T1G | IC REG LDO 2.5V 1A 6HSON |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL9011IRMNZ-T | 功能描述:IC REG LDO 3V/3.3V 10-DFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 线性 系列:- 标准包装:2,000 系列:- 稳压器拓扑结构:正,可调式 输出电压:1.2 V ~ 5 V 输入电压:2.5 V ~ 7 V 电压 - 压降(标准):0.24V @ 800mA 稳压器数量:1 电流 - 输出:800mA 电流 - 限制(最小):1.2A 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:TO-261-5,TO-261AB 供应商设备封装:SOT-223-5 包装:带卷 (TR) 其它名称:*LP3964EMPX-ADJLP3964EMPX-ADJLP3964EMPX-ADJ-NDLP3964EMPX-ADJ/NOPBTR |

| ISL9011IRMSZ | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Dual LDO with Low Noise, Low IQ, and High PSRR |

| ISL9011IRMSZ-T | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Dual LDO with Low Noise, Low IQ, and High PSRR |

| ISL9011IRNCZ | 功能描述:IC REG LDO 3.3V/1.8V 10-DFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 线性 系列:- 标准包装:2,000 系列:- 稳压器拓扑结构:正,可调式 输出电压:1.2 V ~ 5 V 输入电压:2.5 V ~ 7 V 电压 - 压降(标准):0.24V @ 800mA 稳压器数量:1 电流 - 输出:800mA 电流 - 限制(最小):1.2A 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:TO-261-5,TO-261AB 供应商设备封装:SOT-223-5 包装:带卷 (TR) 其它名称:*LP3964EMPX-ADJLP3964EMPX-ADJLP3964EMPX-ADJ-NDLP3964EMPX-ADJ/NOPBTR |

| ISL9011IRNCZ-T | 功能描述:IC REG LDO 3.3V/1.8V 10-DFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 线性 系列:- 标准包装:2,000 系列:- 稳压器拓扑结构:正,可调式 输出电压:1.2 V ~ 5 V 输入电压:2.5 V ~ 7 V 电压 - 压降(标准):0.24V @ 800mA 稳压器数量:1 电流 - 输出:800mA 电流 - 限制(最小):1.2A 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:TO-261-5,TO-261AB 供应商设备封装:SOT-223-5 包装:带卷 (TR) 其它名称:*LP3964EMPX-ADJLP3964EMPX-ADJLP3964EMPX-ADJ-NDLP3964EMPX-ADJ/NOPBTR |

发布紧急采购,3分钟左右您将得到回复。