参数资料

| 型号: | ISL98001CQZ-240 |

| 厂商: | Intersil |

| 文件页数: | 10/31页 |

| 文件大小: | 0K |

| 描述: | IC TRPL VIDEO DIGITIZER 128-MQFP |

| 标准包装: | 66 |

| 类型: | 视频数字转换器 |

| 应用: | 数字电视,显示器,数字 KVM,图形处理 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 128-BFQFP |

| 供应商设备封装: | 128-MQFP(14x20) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页当前第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页

18

FN6148.5

September 21, 2010

Technical Highlights

The ISL98001 provides all the features of traditional triple

channel video AFEs, but adds several next-generation

enhancements, bringing performance and ease of use to

new levels.

DPLL

All video AFEs must phase lock to an HSYNC signal,

supplied either directly or embedded in the video stream

(Sync On Green). Historically this has been implemented as

a traditional analog PLL. At SXGA and lower resolutions, an

analog PLL solution has proven adequate, if somewhat

troublesome (due to the need to adjust charge pump

currents, VCO ranges and other parameters to find the

optimum trade-off for a wide range of pixel rates).

As display resolutions and refresh rates have increased,

however, the pixel period has shrunk. An XGA pixel at a

60Hz refresh rate has 15.4ns to change and settle to its new

value. But at UXGA 75Hz, the pixel period is 4.9ns. Most

consumer graphics cards (even the ones with “350MHz”

DACs) spend most of that time slewing to the new pixel

value. The pixel may settle to its final value with 1ns or less

before it begins slewing to the next pixel. In many cases it

rings and never settles at all. So precision, low-jitter

sampling is a fundamental requirement at these speeds, and

a difficult one for an analog PLL to meet.

The ISL98001's DPLL has less than 250ps of jitter, peak to

peak, and independent of the pixel rate. The DPLL generates

64-phase steps per pixel (vs the industry standard 32), for

fine, accurate positioning of the sampling point. The crystal-

locked NCO inside the DPLL completely eliminates drift due to

charge pump leakage, so there is inherently no frequency or

phase change across a line. An intelligent all-digital loop

filter/controller eliminates the need for the user to have to

program or change anything (except for the number of pixels)

to lock over a range from interlaced video (10MHz or higher)

to UXGA 60Hz (170MHz, with the ISL98001-170).

The DPLL eliminates much of the performance limitations and

complexity associated with noise-free digitization of high

speed signals.

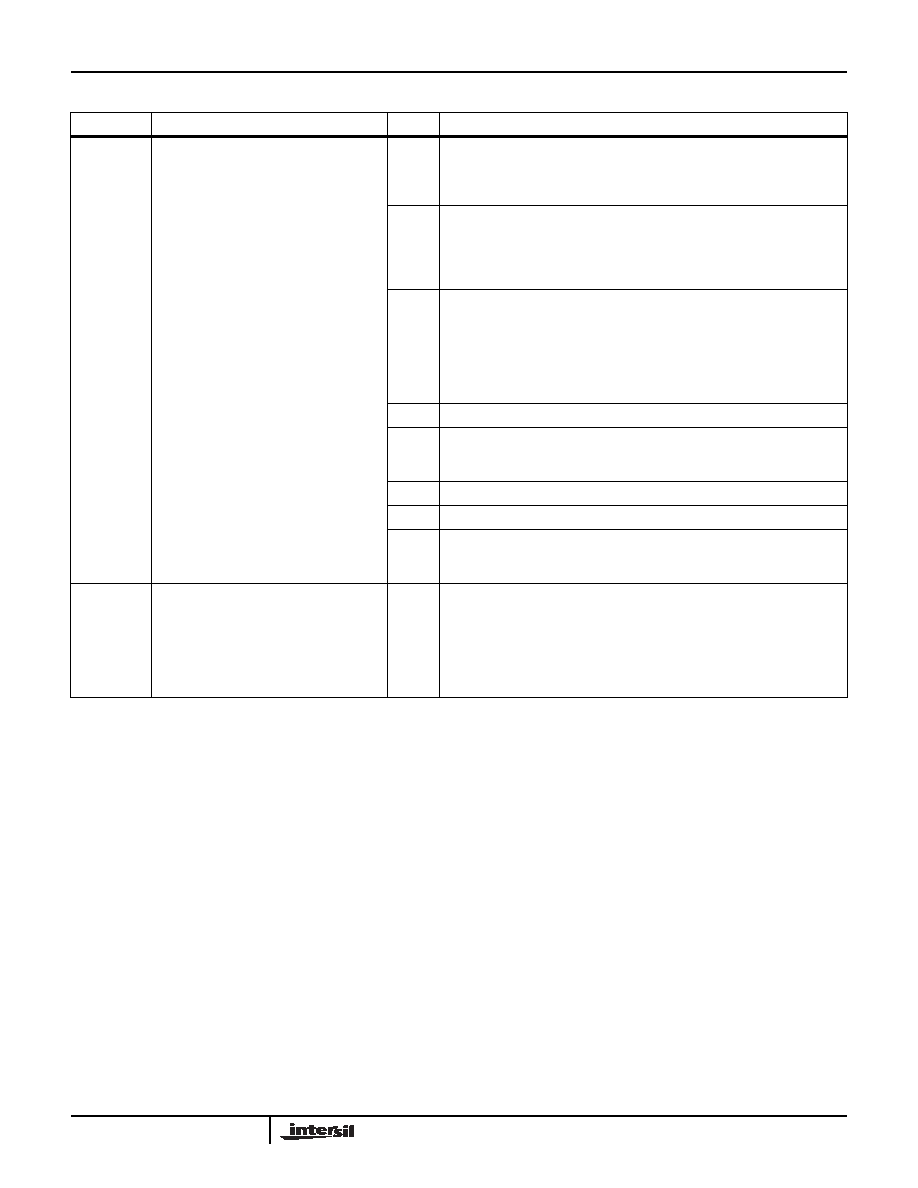

0x25

Sync Separator Control (0x00)

0

Three-state Sync

Outputs

0: VSYNCOUT, HSYNCOUT, VSOUT, HSOUT are

active (default).

1: VSYNCOUT, HSYNCOUT, VSOUT, HSOUT are in

three-state.

1

COAST Polarity

0: Coast active high (default)

1: Coast active low

Set to 0 for internal VSYNC extracted from CSYNC.

Set to 0 or 1 as appropriate to match external VSYNC

or external COAST.

2HSOUT Lock Edge

0: HSOUT's trailing edge is locked to selected

HSYNCIN's lock edge. Leading edge moves

backward in time as HSOUT width is increased

(X980xx default).

1: HSOUT's leading edge is locked to selected

HSYNCIN's lock edge. Trailing edge moves forward in

time as HSOUT width is increased.

3

Reserved

Set to 0

4

VSYNCOUT Mode

0: VSYNCOUT is aligned to HSYNCOUT edge,

providing “perfect” VSYNC signal (default).

1: VSYNCOUT is “raw” integrator output.

5

Reserved

Set to 0

6

Reserved

Set to 0

7VSOUT Mode

0: VSOUT is output on VSOUT pin (default).

1: COAST (including pre- and post-coast COAST) is

output on VSOUT pin.

0x2B

Crystal Multiplier (0x14)

7:0

Crystal Multiplier

When using the ISL98001-275, the value in this

register must need to be changed to achieve the

maximum conversion rate (see “Initialization” on

page 26. This register may also be adjusted to lower

power consumption at slower pixel rates (see the

information).

Register Listing (Continued)

ADDRESS

REGISTER (DEFAULT VALUE)

BIT(S)

FUNCTION NAME

DESCRIPTION

ISL98001

相关PDF资料 |

PDF描述 |

|---|---|

| ISL99201IRTDZ-T | IC AMP AUDIO 1.5W MONO D 8TDFN |

| ISL99202IRTAZ-TK | IC AMP STEREO 60MW 12-TQFN |

| ISL99203IIZ-T | IC AMP AUDIO 5.5W MONO D 20WLCSP |

| ISPPAC-CLK5320S-01T64I | IC BUFFER FANOUT ISP UNIV 64TQFP |

| KA2901DMTF | IC COMPARATOR QUAD 14-SOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL98001CQZ-275 | 功能描述:IC TRPL VIDEO DIGITIZER 128-MQFP RoHS:是 类别:集成电路 (IC) >> 线性 - 视频处理 系列:- 产品变化通告:Product Discontinuation 07/Mar/2011 标准包装:3,000 系列:OMNITUNE™ 类型:调谐器 应用:移动电话,手机,视频显示器 安装类型:表面贴装 封装/外壳:65-WFBGA 供应商设备封装:PG-WFSGA-65 包装:带卷 (TR) 其它名称:SP000365064 |

| ISL98001CQZ-EVALZ | 功能描述:EVALUATION BOARD ISL98001CQZ RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PCI Express® (PCIe) 主要目的:接口,收发器,PCI Express 嵌入式:- 已用 IC / 零件:DS80PCI800 主要属性:- 次要属性:- 已供物品:板 |

| ISL98001CQZ-R5296 | 制造商:Intersil Corporation 功能描述:ISL98001CQZ PB-FREE TRIPLE VIDEO DIGITIZER W/ DIGITAL PLL, T - Trays |

| ISL98001IQZ-140 | 功能描述:IC TRPL VIDEO DIGITIZER 128-MQFP RoHS:是 类别:集成电路 (IC) >> 线性 - 视频处理 系列:- 标准包装:250 系列:- 类型:电平移位器 应用:LCD 电视机/监控器 安装类型:表面贴装 封装/外壳:28-WFQFN 裸露焊盘 供应商设备封装:28-WQFN(4x4)裸露焊盘 包装:带卷 (TR) 其它名称:296-32523-2TPS65198RUYT-ND |

| ISL98002CRZ-140 | 功能描述:IC VID DIGITIZER 3CHN AFE 72-QFN RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。