- 您现在的位置:买卖IC网 > PDF目录10742 > ISL98003CNZ-110 (Intersil)IC AFE 3CH 8BIT 110MHZ 80EPTQFP PDF资料下载

参数资料

| 型号: | ISL98003CNZ-110 |

| 厂商: | Intersil |

| 文件页数: | 5/31页 |

| 文件大小: | 0K |

| 描述: | IC AFE 3CH 8BIT 110MHZ 80EPTQFP |

| 标准包装: | 119 |

| 位数: | 8 |

| 通道数: | 3 |

| 功率(瓦特): | 1.1W |

| 电压 - 电源,模拟: | 1.8V,3.3V |

| 电压 - 电源,数字: | 1.65 V ~ 2 V |

| 封装/外壳: | 80-TQFP 裸露焊盘 |

| 供应商设备封装: | 80-TQFP-EP(12x12) |

| 包装: | 托盘 |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页

13

FN6760.0

September 12, 2008

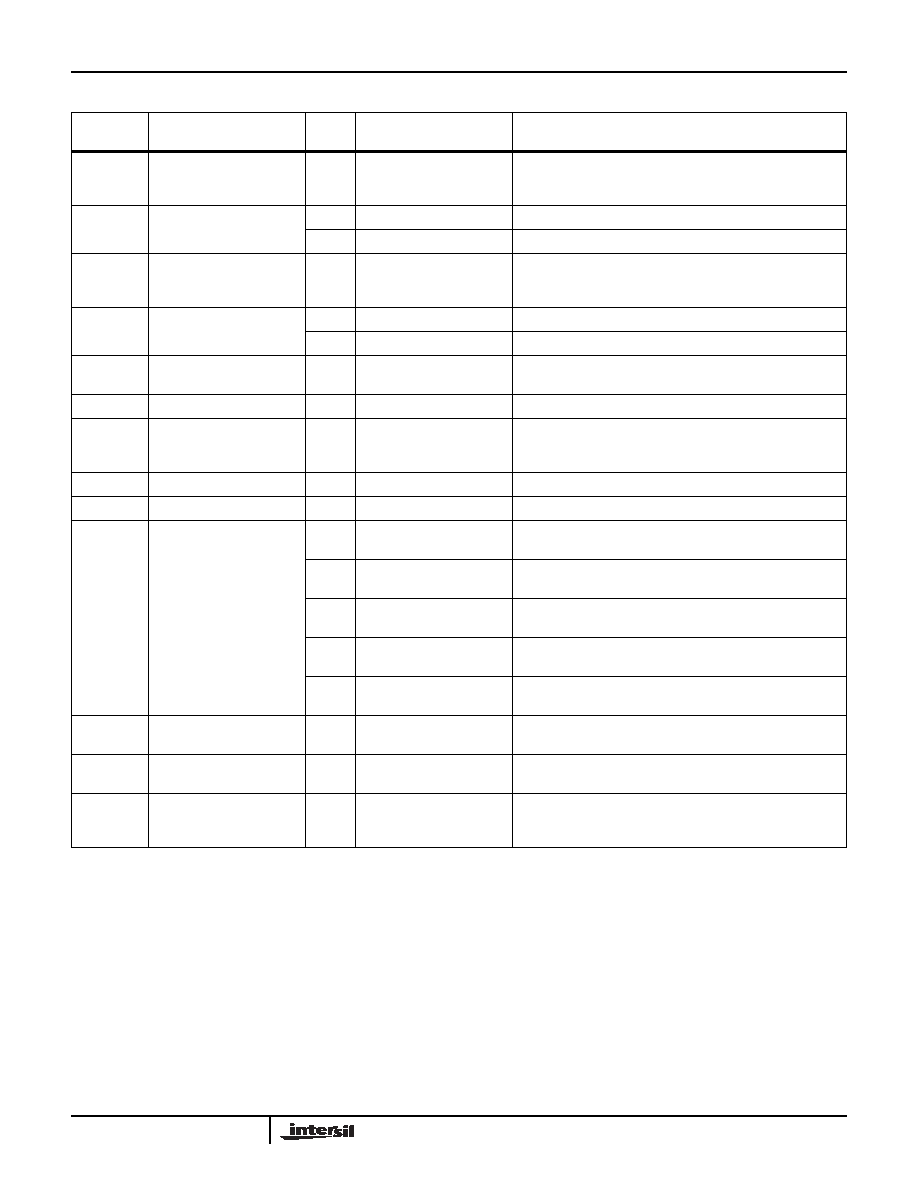

0x1A

Green Offset MSB, (0x80)

7:0

Green Offset MSB

ABLC off: upper 8 bits to Green offset DAC

ABLC enabled: Green digital offset

(See Red Offset)

0x1B

Green Offset LSB, (0x00)

5:0

N/A

7:6

Green Offset LSB

See Red Offset

0x1C

Blue Offset MSB, (0x80)

7:0

Blue Offset MSB

ABLC off: upper 8 bits to Blue offset DAC

ABLC enabled: Blue digital offset

(See Red Offset)

0x1D

Blue Offset LSB, (0x00)

5:0

N/A

7:6

Blue Offset LSB

See Red Offset

0x1E

PLL HTOTAL MSB, (0x06)

5:0

PLL HTOTAL MSB

14-bit HTOTAL

PLL updated on LSB write only.

0x1F

PLL HTOTAL LSB, (0x98)

7:0

PLL HTOTAL LSB

PLL updated on LSB write only. SXGA default

0x20

PLL Phase, (0x00)

5:0

PLL Sampling Phase

Used to control the phase of the ADC’s sample point relative

to the period of a pixel. Adjust to obtain optimum image quality.

One step = 5.625° (1.56% of pixel period).

0x21

PLL Pre-coast, (0x04)

7:0

Pre-coast

Number of lines the PLL will coast prior to the start of VSYNC.

0x22

PLL Post-coast, (0x04)

7:0

Post-coast

Number of lines the PLL will coast after the end of VSYNC.

0x23

PLL Misc, (0x00)

0

PLL Lock Edge HSYNC

0: PLL locks to trailing edge of selected HSYNC (default)

1: PLL locks to leading edge of selected HSYNC

1

CLKINV ENABLE

0: CLKINV input ignored

1: CLKINV input enabled

2

Ext Coast SEL

0: Internal COAST generation

1: External COAST source

3

Ext Coast POL

0: Active high external COAST

1: Active low external COAST

4

EXT CLOCK

0: Internal pixel clock from DPLL

1: External pixel clock from EXTCLKin pin

0x24

DC-Restore and ABLC

starting pixel MSB, (0x00)

5:0

DC-Restore and ABLC

starting pixel (MSB)

Pixel after Raw HSYNC trailing edge to begin DC-restore and

ABLC. 14 bits.

0x25

DC-Restore and ABLC

starting pixel LSB, (0x02)

7:0

DC-Restore and ABLC

starting pixel (LSB)

0x26

DC-Restore Clamp Width,

(0x10)

7:0

DC-Restore clamp width

Only applies to DC-restore clamp used for AC-coupled

configurations. A value of 0x00 means the clamp DAC is never

connected to the input.

Register Listing (Continued)

ADDRESS

REGISTER

(DEFAULT VALUE)

BITS

FUNCTION NAME

DESCRIPTION

ISL98003

相关PDF资料 |

PDF描述 |

|---|---|

| MAX907ESA+ | IC COMPAR HS DUAL 8-SOIC |

| MAX923CPA+ | IC COMPARATOR W/REF 8-DIP |

| VE-JNM-MY-F1 | CONVERTER MOD DC/DC 10V 50W |

| VE-JNL-MY-F1 | CONVERTER MOD DC/DC 28V 50W |

| VE-JNL-MY-F4 | CONVERTER MOD DC/DC 28V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL98003CNZ-150 | 功能描述:IC AFE 3CH 8BIT 150MHZ 80EPTQFP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| ISL98003CNZ-165 | 功能描述:IC AFE 3CH 8BIT 165MHZ 80EPTQFP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| ISL98003CNZ-165S2733 | 制造商:Intersil Corporation 功能描述:TANGTOP ISL98003CNZ-T165 W/BUSINESS TRACKING REQUIREMENTS - Trays |

| ISL98003CNZ-EVALZ | 功能描述:EVAL BOARD FOR ISL98003CNZ RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:* 标准包装:1 系列:PCI Express® (PCIe) 主要目的:接口,收发器,PCI Express 嵌入式:- 已用 IC / 零件:DS80PCI800 主要属性:- 次要属性:- 已供物品:板 |

| ISL98003INZ-110 | 功能描述:IC AFE 3CH 8BIT 110MHZ 80EPTQFP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。