- 您现在的位置:买卖IC网 > PDF目录67723 > ISP1181BBS,518 (ST-ERICSSON) UNIVERSAL SERIAL BUS CONTROLLER, PQCC48 PDF资料下载

参数资料

| 型号: | ISP1181BBS,518 |

| 厂商: | ST-ERICSSON |

| 元件分类: | 总线控制器 |

| 英文描述: | UNIVERSAL SERIAL BUS CONTROLLER, PQCC48 |

| 封装: | 7 X 7 MM, 0.85 MM HEIGHT, PLASTIC, MO-220, SOT-619-2, HVQFN-48 |

| 文件页数: | 8/71页 |

| 文件大小: | 351K |

| 代理商: | ISP1181BBS,518 |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页

Philips Semiconductors

ISP1181B

Full-speed USB peripheral controller

Product data

Rev. 02 — 07 December 2004

15 of 70

9397 750 13958

Koninklijke Philips Electronics N.V. 2004. All rights reserved.

10. DMA transfer

Direct Memory Access (DMA) is a method to transfer data from one location to

another in a computer system, without intervention of the central processor (CPU).

Many different implementations of DMA exist. The ISP1181B supports two methods:

8237 compatible mode: based on the DMA subsystem of the IBM personal

computers (PC, AT and all its successors and clones); this architecture uses the

Intel 8237 DMA controller and has separate address spaces for memory and I/O

DACK-only mode: based on the DMA implementation in some embedded RISC

processors, which has a single address space for both memory and I/O.

The ISP1181B supports DMA transfer for all 14 congurable endpoints (see Table 4).

Only one endpoint at a time can be selected for DMA transfer. The DMA operation of

the ISP1181B can be interleaved with normal I/O mode access to other endpoints.

The following features are supported:

Single-cycle or burst transfers (up to 16 bytes per cycle)

Programmable transfer direction (read or write)

Multiple End-Of-Transfer (EOT) sources: external pin, internal conditions,

short/empty packet

Programmable signal levels on pins DREQ, DACK and EOT.

10.1 Selecting an endpoint for DMA transfer

The target endpoint for DMA access is selected via bits EPDIX[3:0] in the DMA

Conguration Register, as shown in Table 7. The transfer direction (read or write) is

automatically set by bit EPDIR in the associated ECR, to match the selected endpoint

type (OUT endpoint: read; IN endpoint: write).

Asserting input DACK automatically selects the endpoint specied in the DMA

Conguration Register, regardless of the current endpoint used for I/O mode access.

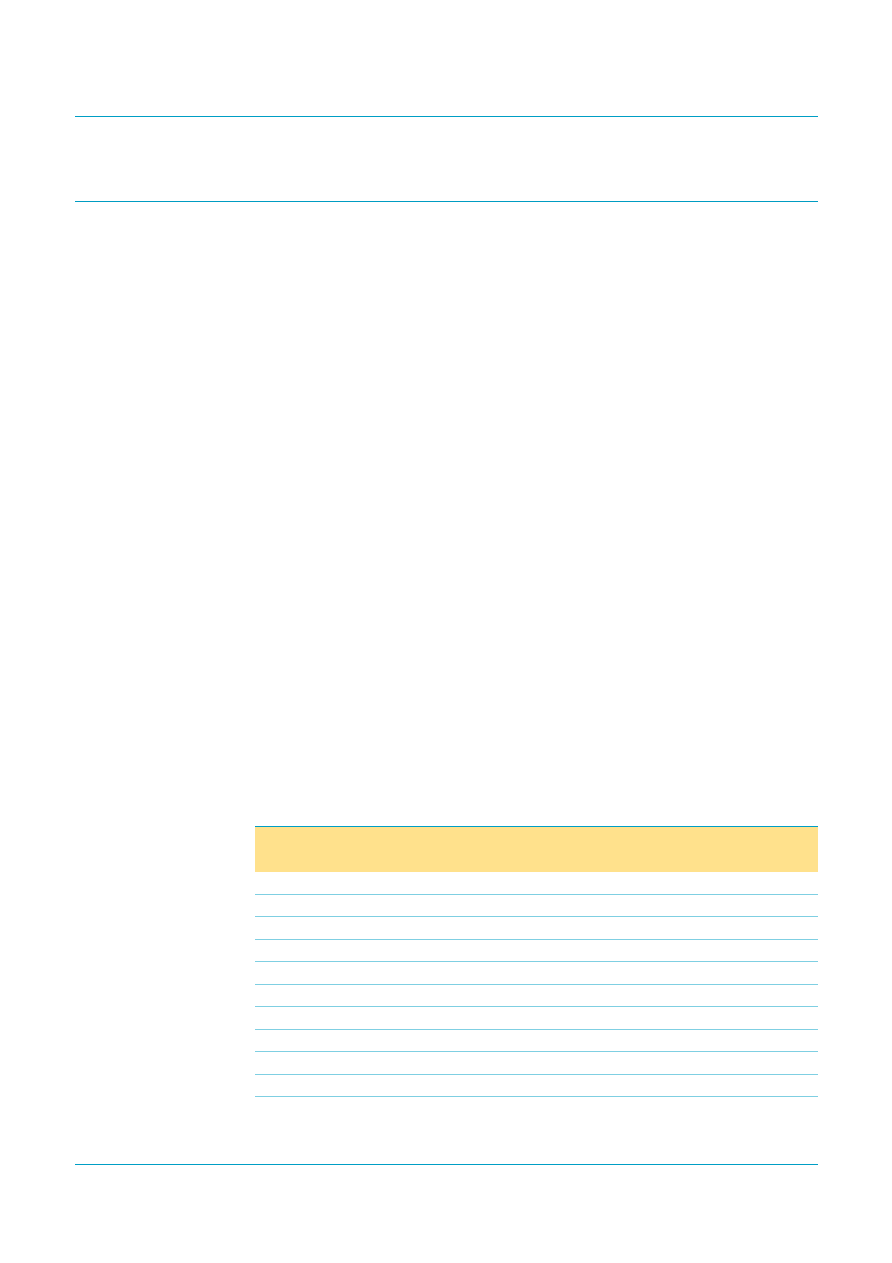

Table 7:

Endpoint selection for DMA transfer

Endpoint

identier

EPIDX[3:0]

Transfer direction

EPDIR = 0

EPDIR = 1

1

0010

OUT: read

IN: write

2

0011

OUT: read

IN: write

3

0100

OUT: read

IN: write

4

0101

OUT: read

IN: write

5

0110

OUT: read

IN: write

6

0111

OUT: read

IN: write

7

1000

OUT: read

IN: write

8

1001

OUT: read

IN: write

9

1010

OUT: read

IN: write

10

1011

OUT: read

IN: write

11

1100

OUT: read

IN: write

相关PDF资料 |

PDF描述 |

|---|---|

| ISP1181BDGG,112 | UNIVERSAL SERIAL BUS CONTROLLER, PDSO48 |

| ISP1183BS,157 | UNIVERSAL SERIAL BUS CONTROLLER, PQCC32 |

| ISP1362EE,551 | UNIVERSAL SERIAL BUS CONTROLLER, PBGA64 |

| ISP1520BD,557 | UNIVERSAL SERIAL BUS CONTROLLER, PQFP64 |

| ISP1520BD,557 | UNIVERSAL SERIAL BUS CONTROLLER, PQFP64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISP1181BBSGE | 功能描述:IC USB CNTRLR FULL-SPD 48-HVQFN RoHS:是 类别:集成电路 (IC) >> 接口 - 控制器 系列:- 标准包装:4,900 系列:- 控制器类型:USB 2.0 控制器 接口:串行 电源电压:3 V ~ 3.6 V 电流 - 电源:135mA 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:36-VFQFN 裸露焊盘 供应商设备封装:36-QFN(6x6) 包装:* 其它名称:Q6396337A |

| ISP1181BBS-S | 功能描述:IC USB HOST CTRL FLL-SPD 48HVQFN RoHS:是 类别:集成电路 (IC) >> 接口 - 控制器 系列:- 标准包装:4,900 系列:- 控制器类型:USB 2.0 控制器 接口:串行 电源电压:3 V ~ 3.6 V 电流 - 电源:135mA 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:36-VFQFN 裸露焊盘 供应商设备封装:36-QFN(6x6) 包装:* 其它名称:Q6396337A |

| ISP1181BBS-T | 功能描述:USB 接口集成电路 USB 1.1 DEVICE CONTROLLER RoHS:否 制造商:Cypress Semiconductor 产品:USB 2.0 数据速率: 接口类型:SPI 工作电源电压:3.15 V to 3.45 V 工作电源电流: 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:WLCSP-20 |

| ISP1181BBSUM | 功能描述:IC USB HOST CTRL FLL-SPD 48HVQFN RoHS:是 类别:集成电路 (IC) >> 接口 - 控制器 系列:- 标准包装:4,900 系列:- 控制器类型:USB 2.0 控制器 接口:串行 电源电压:3 V ~ 3.6 V 电流 - 电源:135mA 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:36-VFQFN 裸露焊盘 供应商设备封装:36-QFN(6x6) 包装:* 其它名称:Q6396337A |

| ISP1181BDGG | 功能描述:USB 接口集成电路 USB CNTRLR FULL-SPD RoHS:否 制造商:Cypress Semiconductor 产品:USB 2.0 数据速率: 接口类型:SPI 工作电源电压:3.15 V to 3.45 V 工作电源电流: 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:WLCSP-20 |

发布紧急采购,3分钟左右您将得到回复。