参数资料

| 型号: | KAD5512P-17Q72 |

| 厂商: | Intersil |

| 文件页数: | 17/36页 |

| 文件大小: | 0K |

| 描述: | IC ADC 12BIT 170MSPS SGL 72-QFN |

| 产品培训模块: | High-Speed Analog-to-Digital Converters |

| 标准包装: | 1 |

| 系列: | FemtoCharge™ |

| 位数: | 12 |

| 采样率(每秒): | 170M |

| 数据接口: | 串行,SPI? |

| 转换器数目: | 1 |

| 功率耗散(最大): | 253mW |

| 电压电源: | 单电源 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 72-VFQFN 裸露焊盘 |

| 供应商设备封装: | 72-QFN(10x10) |

| 包装: | 托盘 |

| 输入数目和类型: | 1 个差分,单极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

KAD5512P

24

FN6807.4

October 1, 2010

Serial Peripheral Interface

A serial peripheral interface (SPI) bus is used to

facilitate configuration of the device and to optimize

performance. The SPI bus consists of chip select (CSB),

serial clock (SCLK) serial data output (SDO), and serial

data input/output (SDIO). The maximum SCLK rate is

equal to the ADC sample rate (fSAMPLE) divided by 16

for write operations and fSAMPLE divided by 66 for

reads. At fSAMPLE = 250MHz, maximum SCLK is

15.63MHz for writing and 3.79MHz for read operations.

There is no minimum SCLK rate.

The following sections describe various registers that

are used to configure the SPI or adjust performance or

functional parameters. Many registers in the available

address space (0x00 to 0xFF) are not defined in this

document. Additionally, within a defined register there

may be certain bits or bit combinations that are

reserved. Undefined registers and undefined values

within defined registers are reserved and should not be

selected. Setting any reserved register or value may

produce indeterminate results.

SPI Physical Interface

The serial clock pin (SCLK) provides synchronization for

the data transfer. By default, all data is presented on the

serial data input/output (SDIO) pin in three-wire mode.

The state of the SDIO pin is set automatically in the

communication protocol (described below). A dedicated

serial data output pin (SDO) can be activated by setting

0x00[7] high to allow operation in four-wire mode.

SDO should always be connected to OVDD with a 4.7kΩ

resistor even if not used. If the 4.7kΩ resistor is not

present the ADC will not exit the reset state.

The SPI port operates in a half duplex master/slave

configuration, with the KAD5512P functioning as a slave.

Multiple slave devices can interface to a single master in

three-wire mode only, since the SDO output of an

unaddressed device is asserted in four-wire mode.

The chip-select bar (CSB) pin determines when a slave

device is being addressed. Multiple slave devices can be

written to concurrently, but only one slave device can be

read from at a given time (again, only in three-wire

mode). If multiple slave devices are selected for reading

at the same time, the results will be indeterminate.

The communication protocol begins with an

instruction/address phase. The first rising SCLK edge

following a high to low transition on CSB determines the

beginning of the two-byte instruction/address command;

SCLK must be static low before the CSB transition. Data

can be presented in MSB-first order or LSB-first order.

The default is MSB-first, but this can be changed by

appropriate bit ordering for the MSB-first and LSB-first

modes, respectively. In MSB-first mode the address is

incremented for multi-byte transfers, while in LSB-first

mode it’s decremented.

In the default mode, the MSB is R/W, which determines if

the data is to be read (active high) or written. The next

two bits, W1 and W0, determine the number of data

bytes to be read or written (see Table 6). The lower 13

bits contain the first address for the data transfer. This

relationship is illustrated in Figure 37, and timing values

are given in “Switching Specifications” on page 14.

After the instruction/address bytes have been read, the

appropriate number of data bytes are written to or read

from the ADC (based on the R/W bit status). The data

transfer will continue as long as CSB remains low and

SCLK is active. Stalling of the CSB pin is allowed at any

byte boundary (instruction/address or data) if the

number of bytes being transferred is three or less. For

transfers of four bytes or more, CSB is allowed stall in

the middle of the instruction/address bytes or before the

first data byte. If CSB transitions to a high state after

that point the state machine will reset and terminate the

data transfer.

2-byte and N-byte transfers, respectively. The operation for

a 3-byte transfer can be inferred from these diagrams.

SPI Configuration

ADDRESS 0X00: CHIP_PORT_CONFIG

Bit ordering and SPI reset are controlled by this register. Bit

order can be selected as MSB to LSB (MSB first) or LSB to

MSB (LSB first) to accommodate various microcontrollers.

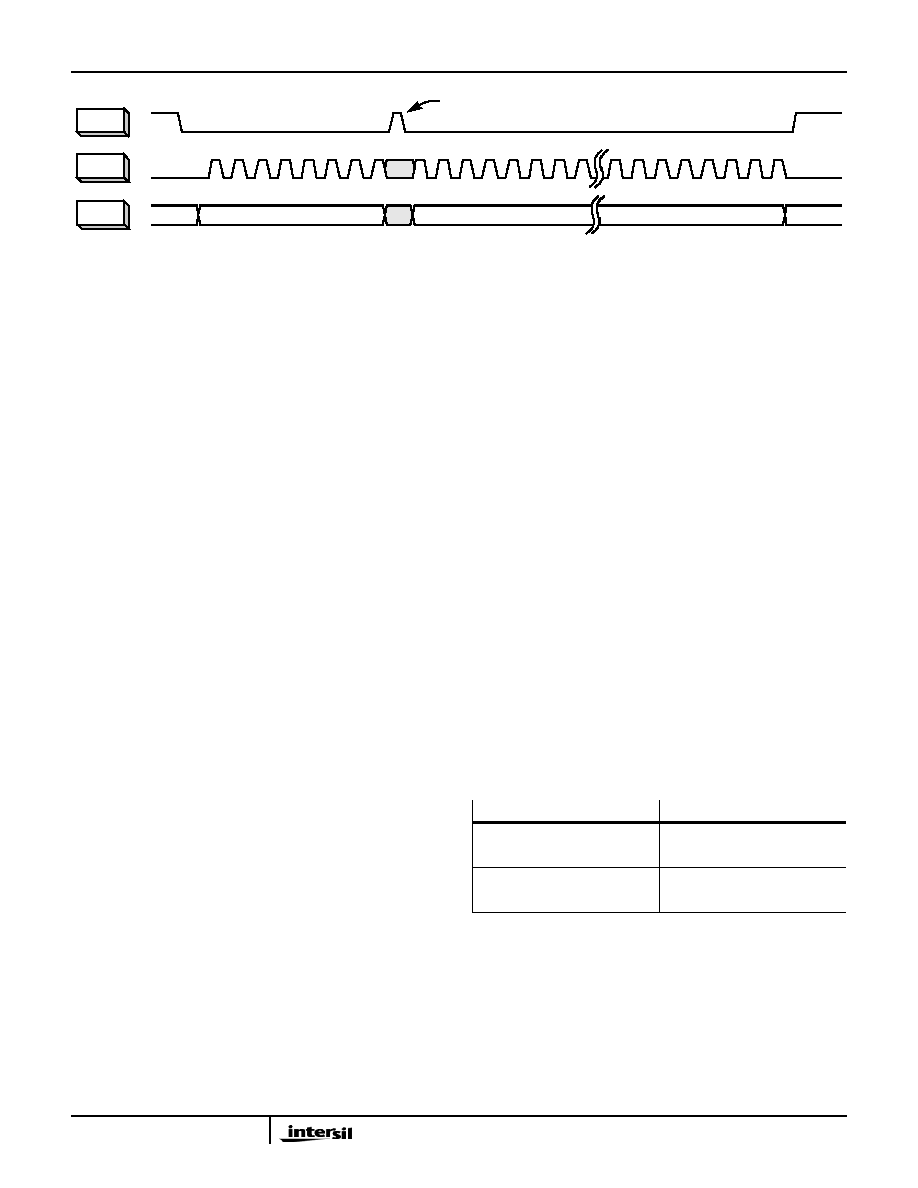

FIGURE 40. N-BYTE TRANSFER

CSB

SCLK

SDIO

INSTRUCTION/ADDRESS

DATA WORD 1

DATA WORD N

LAST LEGAL

CSB STALLING

TABLE 6. BYTE TRANSFER SELECTION

[W1:W0]

BYTES TRANSFERRED

00

1

01

2

10

3

11

4 or more

相关PDF资料 |

PDF描述 |

|---|---|

| KAD5514P-12Q72 | IC ADC 14BIT 125MSPS SGL 72-QFN |

| KAD5610P-25Q72 | IC ADC 10BIT 250MSPS DUAL 72-QFN |

| KAD5612P-17Q72 | IC ADC 12BIT 170MSPS DUAL 72-QFN |

| LA72715NV-TLM-E | IC AUDIO DECODER JPN MTS 24SSOP |

| LICAL-DEC-LS001 | IC DECODER LOW SECURITY 8DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| KAD5512P-21Q48 | 功能描述:模数转换器 - ADC 12-BIT 210MSPS SINGL ADC PROG LVDS/LVCMOS RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| KAD5512P-21Q72 | 功能描述:模数转换器 - ADC 12-BIT 210MSPS SINGL ADC PROG LVDS/LVCMOS RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| KAD5512P-25Q48 | 功能描述:模数转换器 - ADC 12-BIT 250MSPS SINGL PROG LVDS/LVCMOS RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| KAD5512P-25Q72 | 功能描述:模数转换器 - ADC 12-BIT 250MSPS SINGL PROG LVDS/LVCMOS RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| KAD5512P-50 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:12-Bit, 500MSPS A/D Converter |

发布紧急采购,3分钟左右您将得到回复。