- 您现在的位置:买卖IC网 > PDF目录15934 > KS8695P-EVAL (Micrel Inc)BOARD EVAL EXPERIMENT KS8695P PDF资料下载

参数资料

| 型号: | KS8695P-EVAL |

| 厂商: | Micrel Inc |

| 文件页数: | 16/40页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL EXPERIMENT KS8695P |

| 标准包装: | 1 |

| 其它名称: | 576-1002 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

M9999-081805

23

August 2005

KS8695P

Micrel

Signal Descriptions by Group

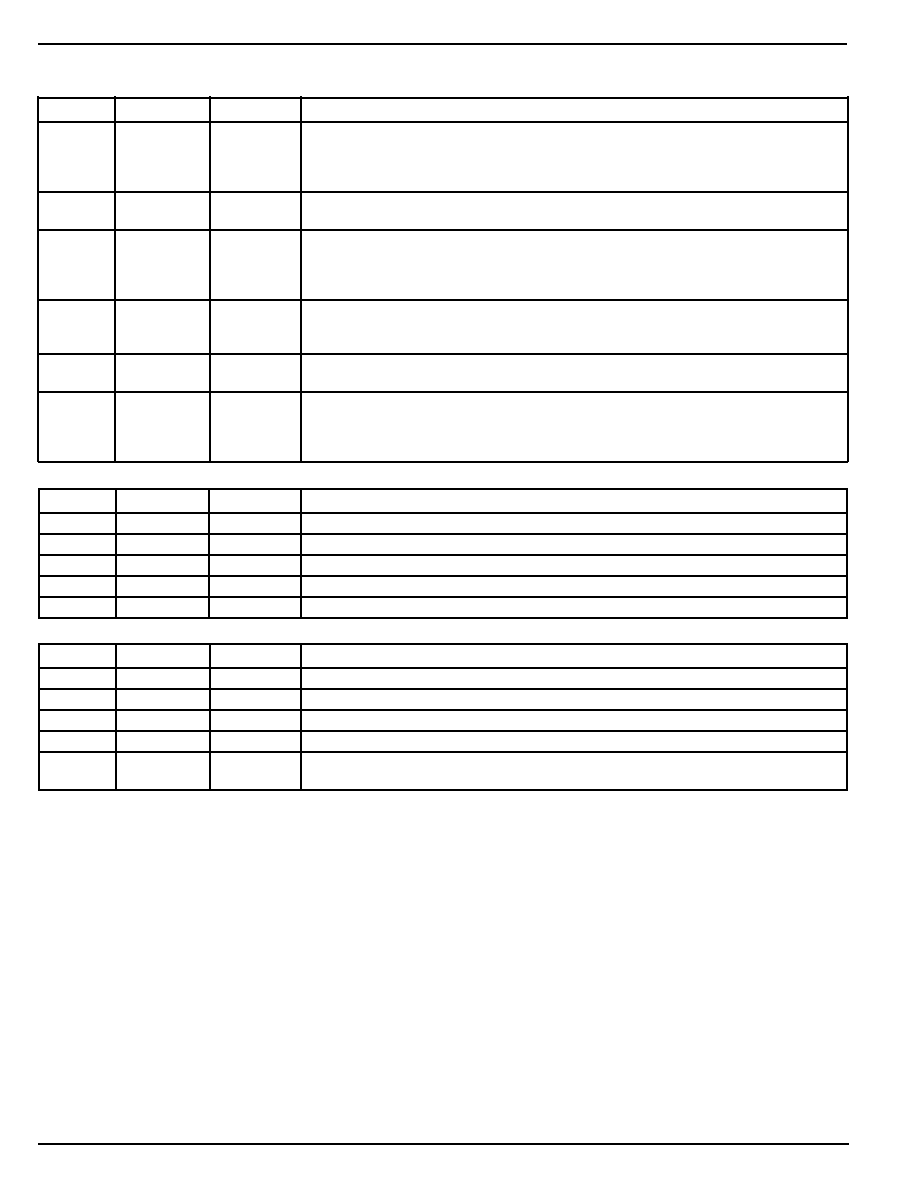

Clock and Reset Pins

Pin

Name

I/O Type(1)

Description

E1

XCLK1/

I

External Clock In. This signal is used as the source clock for the transmit clock of the

CPUCLK

internal MAC and PHY. The clock frequency is 25MHz ±50ppm. The XCLK1

signal is also used as the reference clock signal for the internal PLL to generate the

125MHz internal system clock.

E2

XCLK2

I

External Clock In. Used with XCLK1 pin when another polarity of crystal is needed.

This is unused for a normal clock input.

M15

URTSN/

O/I

Normal Mode: UART request to send. Active low output.

CPUCLKSEL

During reset: CPU clock select. Select CPU clock source. CPUCLKSEL=0 (normal

mode), the internal PLL clock output is used as the CPU clock source.

CPUCLKSEL=1 (factory reserved test signal).

A17

RESETN

I

KS8695P chip reset. Active low input asserted for at least 256 system clock (40ns)

cycles to reset the KS8695P. When in the reset state, all the output pins are tri-stated

and all open drain signals are oating.

U17

WRSTO

O

Watchdog timer reset output. This signal is asserted for at least 200ms if

RESETN is asserted or when the internal watchdog timer expires.

T17

EROEN/

O/I

Normal Mode: ROM/SRAM/FLASH and External I/O output enable. Active low. When

WRSTPLS

asserted, this signal controls the output enable port of the specied device.

During reset: Watchdog timer reset polarity setting. WRSTPLS=0, Active high;

WRSTPLS=1, Active low. No default.

JTAG Interface Pins

Pin

Name

I/O Type(1)

Description

G14

TCK

I

JTAG test clock.

G15

TMS

I

JTAG test mode select.

F14

TDI

I

JTAG test data in.

F15

TDO

O

JTAG test data out.

F16

TRSTN

I

JTAG test reset. Active low.

WAN Ethernet Physical Interface Pins

Pin

Name

I/O Type(1)

Description

G1

WANTXP

O

WAN PHY transmit signal + (differential).

G2

WANTXM

O

WAN PHY transmit signal – (differential).

G3

WANRXP

I

WAN PHY receive signal + (differential).

G4

WANRXM

I

WAN PHY receive signal – (differential).

G5

WANFXSD

I

WAN ber signal detect. Signal detect input when the WAN port is operated in

100BASE-FX 100Mb ber mode. See Application Note 10.

Note:

1. I = Input.

O = Output.

O/I = Output in normal mode; input pin during reset.

相关PDF资料 |

PDF描述 |

|---|---|

| RP10-1205SE/N/M1-HC | CONV DC/DC 10W 9-18VIN 05VOUT |

| GBC31DREN-S93 | CONN EDGECARD 62POS .100 EYELET |

| VE-JN0-EY-S | CONVERTER MOD DC/DC 5V 50W |

| RP15-4815DF-HC | CONV DC/DC 15W 36-75VIN +/-15V |

| GCC19DREI-S93 | CONN EDGECARD 38POS .100 EYELET |

相关代理商/技术参数 |

参数描述 |

|---|---|

| KS8695PI | 功能描述:IC ARM9 W/MMU 5PORT 289-PBGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| KS8695P-MDP-EVAL | 功能描述:EVAL KIT EXPERIMENTAL KS8695PMPD RoHS:否 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- 主要目的:电源管理,电池充电器 嵌入式:否 已用 IC / 零件:MAX8903A 主要属性:1 芯锂离子电池 次要属性:状态 LED 已供物品:板 |

| KS8695P-MMB-EVAL | 功能描述:BOARD EVAL MULTIMEDIA KS8695P RoHS:否 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- 主要目的:电源管理,电池充电器 嵌入式:否 已用 IC / 零件:MAX8903A 主要属性:1 芯锂离子电池 次要属性:状态 LED 已供物品:板 |

| KS8695PX | 功能描述:IC SWITCH 10/100 1PORT 289PBGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| KS8695PXA3 | 功能描述:IC ARM9 W/MMU 5PORT 289-PBGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

发布紧急采购,3分钟左右您将得到回复。