- 您现在的位置:买卖IC网 > PDF目录10803 > KSZ8001L (Micrel Inc)IC TXRX PHY 10/100 3.3V 48-LQFP PDF资料下载

参数资料

| 型号: | KSZ8001L |

| 厂商: | Micrel Inc |

| 文件页数: | 9/46页 |

| 文件大小: | 0K |

| 描述: | IC TXRX PHY 10/100 3.3V 48-LQFP |

| 标准包装: | 250 |

| 类型: | 收发器 |

| 规程: | MII,RMII,SMII |

| 电源电压: | 1.8V, 3.3V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-LQFP |

| 供应商设备封装: | 48-LQFP(7x7) |

| 包装: | 托盘 |

| 产品目录页面: | 1080 (CN2011-ZH PDF) |

| 配用: | 576-1620-ND - BOARD EVALUATION FOR KSZ8001L |

| 其它名称: | 576-1508 576-1508-5 576-1508-5-ND KSZ8001L-ND |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页

Micrel

KSZ8001

June 2009

Revision 1.04

17

SMII Signal Definition

SMII is composed of two signals per port, a global synchronization signal, and a global 125MHz reference clock. All signals are

synchronous to the clock. All SMII I/F uses a common 125MHz reference clock and SYNC signals that are synchronous to the

reference clock. There are two signals in SMII from MAC-to-PHY for each port (TXD and TxSYNC), and one signal per port from

PHY-to-MAC (RXD).

The Serial Media Independent Interface (SMII) is designed to satisfy the following requirements:

Convey complete MII information between a 10/100 PHY and MAC with two pins per port.

Allow a multi-port MAC/PHY communication with one system clock.

Operate in both half and full duplex.

Per packet switching between 10Mbit and 100Mbit data rates.

Allow direct MAC-to-MAC communication.

SMII Signals

Signal Name

From

To

Use

RX

PHY

MAC

Receive Data and Control

TX

MAC

PHY

Transmit Data and Control

SYNC

MAC

PHY

Synchronization

Clock

System

MAC&PHY

Synchronization

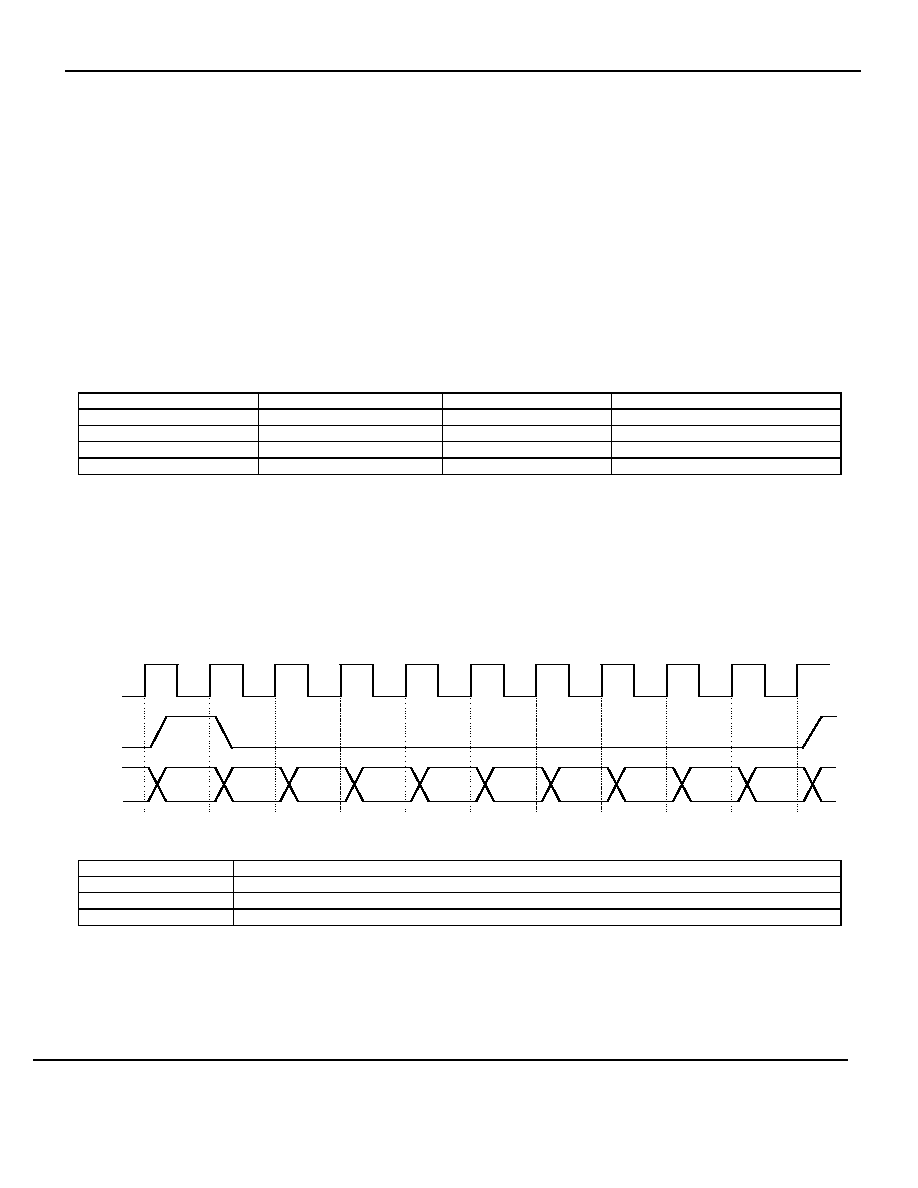

Receive Path

Receive data and control information are signaled in ten bit segments. In 100Mbit mode, each segment represents a new byte of

data. In 10Mbit mode, each segment is repeated ten times; therefore, every ten segments represent a new byte of data. The MAC

can simply any one of every 10 segment ion 10Mbit mode.

Segment boundaries are delimited by SYNC. The MAC continuously generates a pulse on SYNC every 10 clocks.

Receive Sequence Diagram

C R S

R X _ D V

R XD 0

R XD 1

R XD 2

R XD 3

R XD 4

R XD 5

R XD 6

R X D 7

R X _C LK

RX _ S Y N C

RX

RX contains all of the information found on the receive path of the standard MII.

Bits

Purpose

CRS

Carrier Sense – identical to MII, except that it is not an asynchronous signal

RX_DV

Receive Data Valid – identical to MII

RXD7-0

Encoded Data, see the RXD0-7 Encoding table

RX – Bit Description

RXD7-0 are used to convey packet data, RX_ER, and PHY status. The MAC can infer the meaning of RXD on a segment-by-basis

by encoding the two control bits.

相关PDF资料 |

PDF描述 |

|---|---|

| KSZ8001SL | TXRX 10/100 LINKMD 3.3V 48-SSOP |

| LTC1482CS8#PBF | IC TXRX RS485 LOWPWR 8-SOIC |

| BU7251SG-TR | IC COMPARATOR SGL 5.5V SSOP-5 |

| LT1785CS8#PBF | IC TXRX RS485/RS422 60V 8-SOIC |

| AD664KN-UNI | IC DAC 12BIT QUAD UNIPOL 28-DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| KSZ8001L TR | 功能描述:以太网 IC 10/100 BASE-TX/FX Physical Layer Transceiver with LinkMD cable diagnostics, Single 3.3V Supply, 48-LQFP, Lead Free RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

| KSZ8001LA2 | 功能描述:TXRX 10/100 LINKMD 3.3V 48-LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:1,140 系列:AU 类型:收发器 驱动器/接收器数:1/1 规程:CAN 电源电压:5.3 V ~ 27 V 安装类型:表面贴装 封装/外壳:14-SOIC(0.154",3.90mm 宽) 供应商设备封装:14-SO 包装:管件 其它名称:935267940512AU5790D14AU5790D14-ND |

| KSZ8001LA2TR | 功能描述:TXRX 10/100 LINKMD 3.3V 48-LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:1,140 系列:AU 类型:收发器 驱动器/接收器数:1/1 规程:CAN 电源电压:5.3 V ~ 27 V 安装类型:表面贴装 封装/外壳:14-SOIC(0.154",3.90mm 宽) 供应商设备封装:14-SO 包装:管件 其它名称:935267940512AU5790D14AU5790D14-ND |

| KSZ8001LA3 | 功能描述:TXRX 10/100 LINKMD 3.3V 48-LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:1,140 系列:AU 类型:收发器 驱动器/接收器数:1/1 规程:CAN 电源电压:5.3 V ~ 27 V 安装类型:表面贴装 封装/外壳:14-SOIC(0.154",3.90mm 宽) 供应商设备封装:14-SO 包装:管件 其它名称:935267940512AU5790D14AU5790D14-ND |

| KSZ8001LA3TR | 功能描述:TXRX 10/100 LINKMD 3.3V 48-LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:1,140 系列:AU 类型:收发器 驱动器/接收器数:1/1 规程:CAN 电源电压:5.3 V ~ 27 V 安装类型:表面贴装 封装/外壳:14-SOIC(0.154",3.90mm 宽) 供应商设备封装:14-SO 包装:管件 其它名称:935267940512AU5790D14AU5790D14-ND |

发布紧急采购,3分钟左右您将得到回复。