- 您现在的位置:买卖IC网 > PDF目录16561 > KSZ8721BL-EVAL (Micrel Inc)BOARD EVALUATION FOR KSZ8721BL PDF资料下载

参数资料

| 型号: | KSZ8721BL-EVAL |

| 厂商: | Micrel Inc |

| 文件页数: | 5/35页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION FOR KSZ8721BL |

| 标准包装: | 1 |

| 主要目的: | 接口,以太网 PHY |

| 嵌入式: | 否 |

| 已用 IC / 零件: | KSZ8721BL |

| 主要属性: | 1 个端口,100BASE-TX/100BASE-FX/10BASE-T |

| 次要属性: | MII,RMII,HP 自动 MDI,MDI-X 自动极性校正 |

| 已供物品: | 板 |

| 相关产品: | 576-1028-6-ND - IC TXRX PHY 10/100 3.3V 48LQFP 576-1026-6-ND - IC TXRX PHY 10/100 2.5V 48SSOP KSZ8721BLIA4 TR-ND - TRANSCEIVER 10/100 3.3V 48-LQFP KSZ8721BLI TR-ND - TXRX PHY 10/100 2.3.3/5V 48-LQFP KSZ8721BI TR-ND - TXRX PHY 10/100 2.3.3/5V 48-SSOP KSZ8721BLA4 TR-ND - TXRX 10/100 3.3V 48-SSOP KSZ8721BLA4-ND - TXRX 10/100 3.3V 48-SSOP KSZ8721BA4 TR-ND - TXRX 10/100 3.3V 48-SSOP KSZ8721BA4-ND - TXRX 10/100 3.3V 48-SSOP 576-1028-1-ND - IC TXRX PHY 10/100 3.3V 48LQFP 更多... |

| 其它名称: | 576-1626 |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页

Micrel, Inc.

KS8721BL/SL

June 2009

13

M9999-062509-1.3

receive clock is recovered from the line while carrier is active, and operates from the master input clock when the line is

idle. The KS8721BL/SL synchronizes the receive data and control signals on the falling edge of RXC in order to

stabilize the signals at the rising edge of the clock with 10ns setup and hold times.

Transmit Enable

The MAC must assert TXEN at the same time as the rst nibble of the preamble, and de-assert TXEN after the last bit

of the packet.

Receive Data Valid

The KS8721BL/SL asserts RXDV when it receives a valid packet. Line operating speed and MII mode will determine

timing changes in the following way:

For 100BASE-TX links with the MII in 4B mode, RXDV is asserted from the rst nibble of the preamble to the

last nibble of the data packet.

For 10BASE-T links, the entire preamble is truncated. RXDV is asserted with the rst nibble of the SFD “5D”

and remains asserted until the end of the packet.

Error Signals

Whenever the KS8721BL/SL receives an error symbol from the network, it asserts RXER and drives “1110” (4B) on the

RXD pins. When the MAC asserts TXER, the KS8721BL/SL will drive “H” symbols (a Transmit Error dened in the IEEE

802.3 4B/5B code group) out on the line to force signaling errors.

Carrier Sense (CRS)

For 100BASE-TX links, a start-of-stream delimiter, or /J/K symbol pair causes assertion of Carrier Sense (CRS). An

end-of-stream delimiter, or /T/R symbol pair, causes de-assertion of CRS. The PMA layer will also de-assert CRS if

IDLE symbols are received without /T/R, yet in this case RXER will be asserted for one clock cycle when CRS is de-

asserted. For 10BASE-T links, CRS assertion is based on reception of valid preamble, and de-assertion on reception of

an end-of-frame (EOF) marker.

Collision

Whenever the line state is half-duplex and the transmitter and receiver are active at the same time, the KS8721BL/SL

asserts its collision signal, which is asynchronous to any clock.

RMII (Reduced MII) Data Interface

RMII interface species a low-pin count, Reduced Media Independent Interface (RMII) intended for use between

Ethernet PHYs and Switch or Repeater ASICs. It is fully compliant with IEEE 802.3u [2].

This interface has the following characteristics:

It is capable of supporting 10Mbps and 100Mbps data rates.

A single clock reference is sourced from the MAC to PHY (or from an external source).

It provides independent 2-bit wide (di-bit) transmit and receive data paths.

It uses TTL signal levels compatible with common digital CMOS ASIC processes.

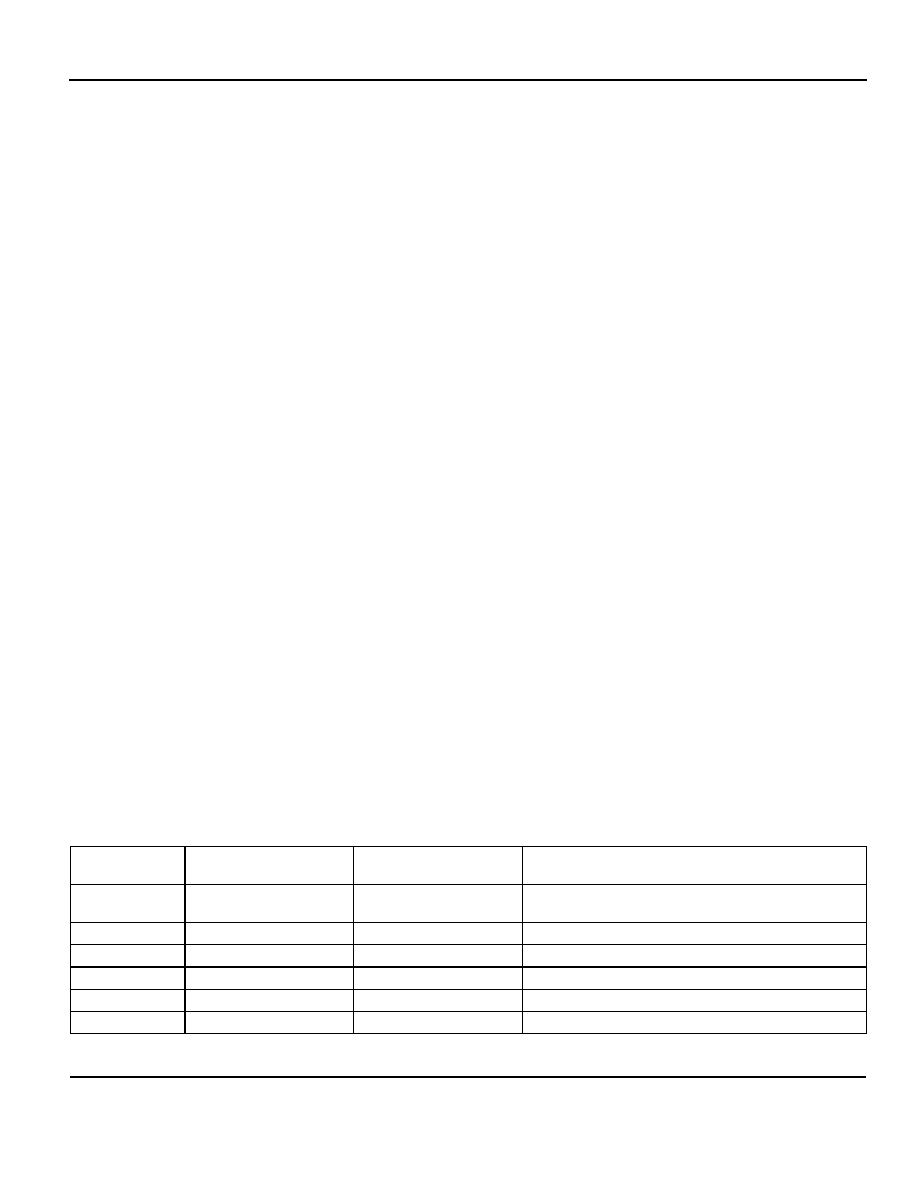

RMII Signal Denition

Signal Name

Direction

(w/respect to the PHY)

Direction

(w/respect to the MAC)

Use

REF_CLK

Input

Input or Output

Synchronous clock reference for receive, transmit and

control interface

CRS_DV

Output

Input

Carrier Sense/Receive Data Valid

RXD[1:0]

Output

Input

Receive Data

TX_EN

Input

Output

Transmit Enable

TXD[1:0]

Input

Output

Transmit Data

RX_ER

Output

Input (Not Required)

Receive Error

相关PDF资料 |

PDF描述 |

|---|---|

| H3BKH-2618M | IDC CABLE - HSR26H/AE26M/HPK26H |

| H1CXH-6436G | IDC CABLE - HKC64H/AE64G/X |

| REC5-243.3DRWZ/H6/C | CONV DC/DC 5W 9-36VIN +/-3.3V |

| EV-ADF4360-6EB1Z | BOARD EVAL FOR ADS4360-6EBIZ |

| MAX15061ATE+T | IC BOOST CONV/CURR MON 16-TQFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| KSZ8721BLI | 功能描述:以太网 IC 10/100 BASE-TX/FX Physical Layer Transceiver, Single 3.3V Supply, 48-LQFP, Indus (Lead Free) RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

| KSZ8721BLI TR | 功能描述:以太网 IC 10/100 BASE-TX/FX Physical Layer Transceiver, Single 3.3V Supply, 48-LQFP, Indus (Lead Free) RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

| KSZ8721BLIA4 TR | 功能描述:TRANSCEIVER 10/100 3.3V 48-LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:1,140 系列:AU 类型:收发器 驱动器/接收器数:1/1 规程:CAN 电源电压:5.3 V ~ 27 V 安装类型:表面贴装 封装/外壳:14-SOIC(0.154",3.90mm 宽) 供应商设备封装:14-SO 包装:管件 其它名称:935267940512AU5790D14AU5790D14-ND |

| KSZ8721BLTR | 制造商:Micrel Inc 功能描述:Physical Layer Transceiver 1-Ch 100Mbps |

| KSZ8721BL-TR | 功能描述:1/1 Transceiver Full MII, RMII 48-LQFP (7x7) 制造商:microchip technology 系列:- 包装:剪切带(CT) 零件状态:有效 类型:收发器 协议:MII,RMII 驱动器/接收器数:1/1 双工:全 接收器滞后:- 数据速率:- 电压 - 电源:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:48-LQFP 供应商器件封装:48-LQFP(7x7) 标准包装:1 |

发布紧急采购,3分钟左右您将得到回复。