- 您现在的位置:买卖IC网 > PDF目录19691 > LC4256B-5FTN256BI (Lattice Semiconductor Corporation)IC CPLD 256MACROCELLS 256FTBGA PDF资料下载

参数资料

| 型号: | LC4256B-5FTN256BI |

| 厂商: | Lattice Semiconductor Corporation |

| 文件页数: | 29/99页 |

| 文件大小: | 0K |

| 描述: | IC CPLD 256MACROCELLS 256FTBGA |

| 标准包装: | 90 |

| 系列: | ispMACH® 4000B |

| 可编程类型: | 系统内可编程 |

| 最大延迟时间 tpd(1): | 5.0ns |

| 电压电源 - 内部: | 2.3 V ~ 2.7 V |

| 逻辑元件/逻辑块数目: | 16 |

| 宏单元数: | 256 |

| 输入/输出数: | 160 |

| 工作温度: | -40°C ~ 105°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 256-LBGA |

| 供应商设备封装: | 256-FTBGA(17x17) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页当前第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页

�� �

�

Lattice� Semiconductor�

�ispMACH� 4000V/B/C/Z� Family� Data� Sheet�

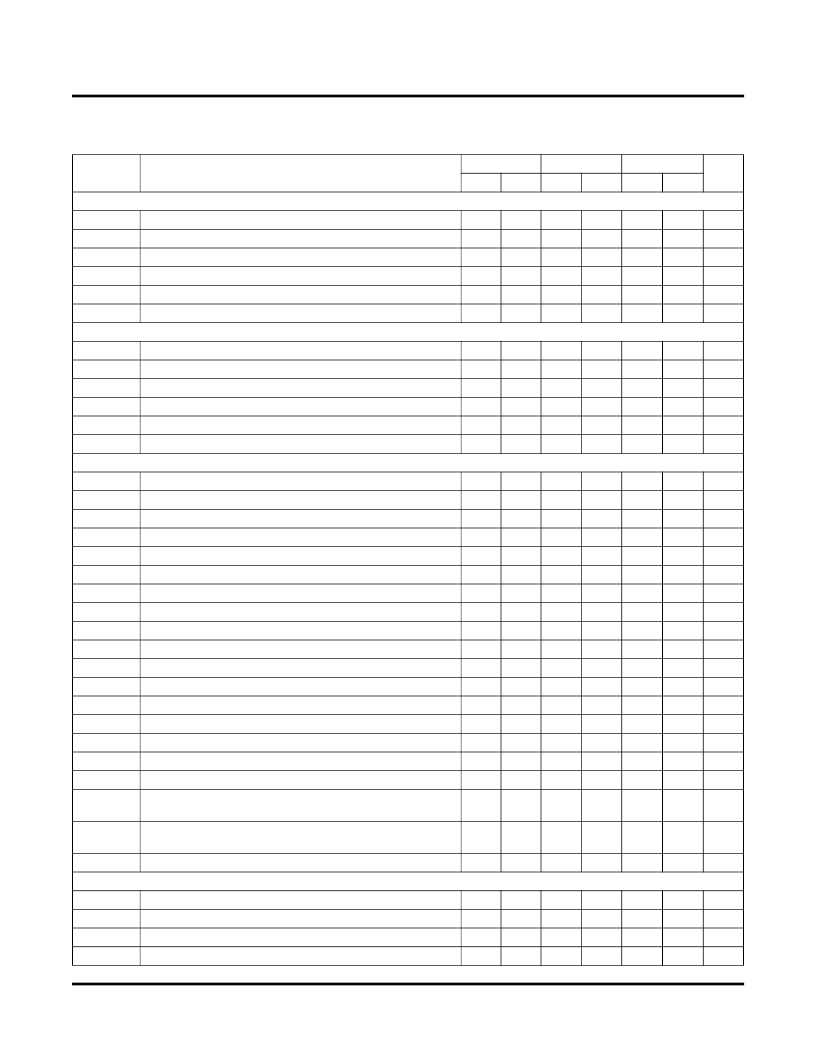

�ispMACH� 4000V/B/C� Internal� Timing� Parameters�

�Over� Recommended� Operating� Conditions�

�-5�

�-75�

�-10�

�Parameter�

�Description�

�Min.�

�Max.�

�Min.�

�Max.�

�Min.�

�Max.�

�Units�

�In/Out� Delays�

�t� IN�

�t� GOE�

�t� GCLK_IN�

�t� BUF�

�t� EN�

�t� DIS�

�Input� Buffer� Delay�

�Global� OE� Pin� Delay�

�Global� Clock� Input� Buffer� Delay�

�Delay� through� Output� Buffer�

�Output� Enable� Time�

�Output� Disable� Time�

�—�

�—�

�—�

�—�

�—�

�—�

�0.95�

�4.04�

�1.83�

�1.00�

�0.96�

�0.96�

�—�

�—�

�—�

�—�

�—�

�—�

�1.50�

�6.04�

�2.28�

�1.50�

�0.96�

�0.96�

�—�

�—�

�—�

�—�

�—�

�—�

�2.00�

�7.04�

�3.28�

�1.50�

�0.96�

�0.96�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�Routing/GLB� Delays�

�t� ROUTE�

�t� MCELL�

�t� INREG�

�t� FBK�

�t� PDb�

�t� PDi�

�Delay� through� GRP�

�Macrocell� Delay�

�Input� Buffer� to� Macrocell� Register� Delay�

�Internal� Feedback� Delay�

�5-PT� Bypass� Propagation� Delay�

�Macrocell� Propagation� Delay�

�—�

�—�

�—�

�—�

�—�

�—�

�1.51�

�1.05�

�0.56�

�0.00�

�1.54�

�0.94�

�—�

�—�

�—�

�—�

�—�

�—�

�2.26�

�1.45�

�0.96�

�0.00�

�2.24�

�1.24�

�—�

�—�

�—�

�—�

�—�

�—�

�3.26�

�1.95�

�1.46�

�0.00�

�3.24�

�1.74�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�Register/Latch� Delays�

�t� S�

�t� S_PT�

�t� ST�

�t� ST_PT�

�t� H�

�t� HT�

�t� SIR�

�t� SIR_PT�

�t� HIR�

�t� HIR_PT�

�t� COi�

�t� CES�

�t� CEH�

�t� SL�

�t� SL_PT�

�t� HL�

�t� GOi�

�t� PDLi�

�t� SRi�

�t� SRR�

�D-Register� Setup� Time� (Global� Clock)�

�D-Register� Setup� Time� (Product� Term� Clock)�

�T-Register� Setup� Time� (Global� Clock)�

�T-Register� Setup� Time� (Product� Term� Clock)�

�D-Register� Hold� Time�

�T-Register� Hold� Time�

�D-Input� Register� Setup� Time� (Global� Clock)�

�D-Input� Register� Setup� Time� (Product� Term� Clock)�

�D-Input� Register� Hold� Time� (Global� Clock)�

�D-Input� Register� Hold� Time� (Product� Term� Clock)�

�Register� Clock� to� Output/Feedback� MUX� Time�

�Clock� Enable� Setup� Time�

�Clock� Enable� Hold� Time�

�Latch� Setup� Time� (Global� Clock)�

�Latch� Setup� Time� (Product� Term� Clock)�

�Latch� Hold� Time�

�Latch� Gate� to� Output/Feedback� MUX� Time�

�Propagation� Delay� through� Transparent� Latch� to� Output/�

�Feedback� MUX�

�Asynchronous� Reset� or� Set� to� Output/Feedback� MUX�

�Delay�

�Asynchronous� Reset� or� Set� Recovery� Time�

�1.32�

�1.32�

�1.52�

�1.32�

�1.68�

�1.68�

�1.52�

�1.45�

�0.68�

�0.68�

�—�

�2.25�

�1.88�

�1.32�

�1.32�

�1.17�

�—�

�—�

�0.28�

�1.67�

�—�

�—�

�—�

�—�

�—�

�—�

�—�

�—�

�—�

�—�

�0.52�

�—�

�—�

�—�

�—�

�—�

�0.33�

�0.25�

�—�

�—�

�1.57�

�1.32�

�1.77�

�1.32�

�2.93�

�2.93�

�1.57�

�1.45�

�1.18�

�1.18�

�—�

�2.25�

�1.88�

�1.57�

�1.32�

�1.17�

�—�

�—�

�0.28�

�1.67�

�—�

�—�

�—�

�—�

�—�

�—�

�—�

�—�

�—�

�—�

�0.67�

�—�

�—�

�—�

�—�

�—�

�0.33�

�0.25�

�—�

�—�

�1.57�

�1.32�

�1.77�

�1.32�

�3.93�

�3.93�

�1.57�

�1.45�

�1.18�

�1.18�

�—�

�2.25�

�1.88�

�1.57�

�1.32�

�1.17�

�—�

�—�

�0.28�

�1.67�

�—�

�—�

�—�

�—�

�—�

�—�

�—�

�—�

�—�

�—�

�1.17�

�—�

�—�

�—�

�—�

�—�

�0.33�

�0.25�

�—�

�—�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�Control� Delays�

�t� BCLK�

�t� PTCLK�

�t� BSR�

�t� PTSR�

�GLB� PT� Clock� Delay�

�Macrocell� PT� Clock� Delay�

�GLB� PT� Set/Reset� Delay�

�Macrocell� PT� Set/Reset� Delay�

�—�

�—�

�—�

�—�

�1.12�

�0.87�

�1.83�

�2.51�

�—�

�—�

�—�

�—�

�1.12�

�0.87�

�1.83�

�3.41�

�—�

�—�

�—�

�—�

�0.62�

�0.87�

�1.83�

�3.41�

�ns�

�ns�

�ns�

�ns�

�29�

�相关PDF资料 |

PDF描述 |

|---|---|

| NCP1216D100R2G | IC CTRLR PWM CM OTP HV 8SOIC |

| MIC5205-2.7BM5 TR | IC REG LDO 2.7V .15A SOT23-5 |

| MIC5203-5.0BM5 TR | IC REG LDO 5V 80MA SOT23-5 |

| V72A36E400BL3 | CONVERTER MOD DC/DC 36V 400W |

| MIC5205-3.1BM5 TR | IC REG LDO 3.1V .15A SOT23-5 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LC4256B-5T100C | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAMMABLE SUPER FAST HI DENSITY PLD RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| LC4256B-5T100I | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAMMABLE SUPER FAST HI DENSITY PLD RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| LC4256B-5T176C | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAMMABLE SUPER FAST HI DENSITY PLD RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| LC4256B-5T176I | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAMMABLE SUPER FAST HI DENSITY PLD RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| LC4256B-5TN100C | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAMMABLE SUPER FAST HI DENSITY PLD RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

发布紧急采购,3分钟左右您将得到回复。