- 您现在的位置:买卖IC网 > PDF目录177666 > LC5512MB-45Q208C (LATTICE SEMICONDUCTOR CORP) PDF资料下载

参数资料

| 型号: | LC5512MB-45Q208C |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 中文描述: | EE PLD, 5.7 ns, PQFP208 |

| 封装: | PLASTIC, QFP-208 |

| 文件页数: | 6/95页 |

| 文件大小: | 923K |

| 代理商: | LC5512MB-45Q208C |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页

Lattice Semiconductor

ispXPLD 5000MX Family Data Sheet

14

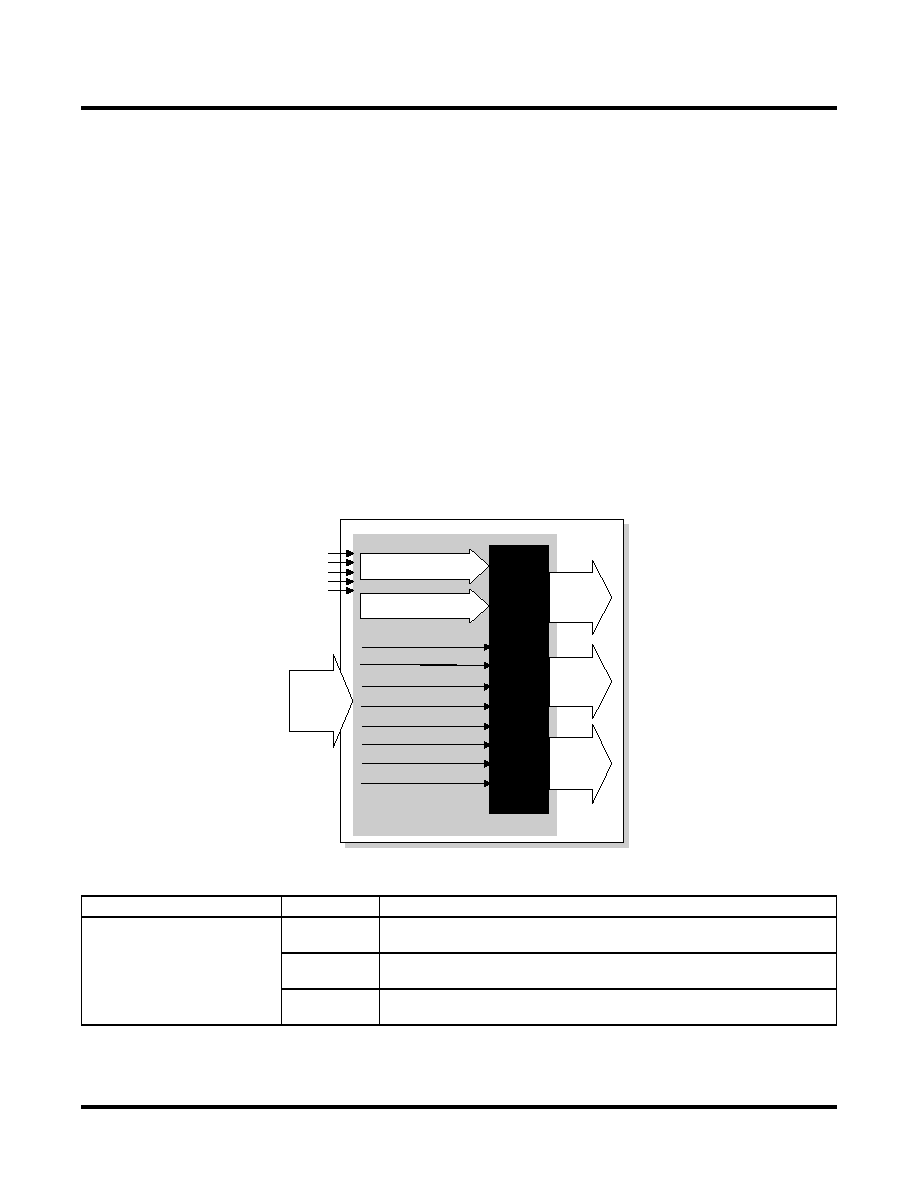

CAM Mode

In CAM Mode the multi-function array is configured as a Ternary Content Addressable Memory (CAM). CAM

behaves like a reverse memory where the input is data and the output is an address. It can be used to perform a

variety of high-performance look-up functions. As such, CAM has two modes of operation. In write or update mode

the CAM behaves as a RAM and data is written to the supplied address. In read or compare operations data is sup-

plied to the CAM and if this matches any of the data in the array the Match and Multiple Match (if there is more than

one match) flags are set to true and the lowest address with matching data is output. The CAM contains 128

entries of 48 bits. Figure 13 shows the block diagram of the CAM.

To further enhance the flexibility of the CAM a mask register is available. If enabled during updates, bits corre-

sponding with those set to 1 in the mask register are not updated. If enabled during compare operations, bits corre-

sponding to those set to 1 in the mask register are not included in the compare. A write don’t care signal allows

don’t cares to be programmed into the CAM if desired. Like other write operations the mask register controls this.

The write/comp data, write address, write enable, write chip select, and write don’t care signals are synchronous.

The CAM Output signals, match flag, and multimatch flag can be synchronous or asynchronous. The Enable mask

register input is not latched but must meet setup and hold times relative to the write clock. All inputs must use the

same clock and clock enable signals. All outputs must use the same clock and clock enable signals. Reset is com-

mon for both inputs and outputs. Table 9 shows the allowable sources for clock, clock enable, and reset for the var-

ious CAM registers.

Figure 13. CAM Mode

Table 9. Register Clocks, Clock Enables, and Initialization in CAM Mode

Register

Input

Source

Write data, Write address,

Enable mask register, Write

enable, write chip select, and

write don’t care, CAM Output,

Match, and Multimatch

Clock

CLK or one of the global clocks (CLK0 - CLK3). Each of these signals can

be inverted if required.

Clock Enable

WE or one of the global clocks (CLK1 - CLK 2). Each of these signals can

be inverted if required.

Reset

Created by the logical OR of the global reset signal and RST. RST is routed

by the multifunction array from GRP, with inversion if desired

‘

68 Inputs

From

Routing

Write Enable (WE)

En Mask Reg (EN_MASK)

Reset (RST)

Write Chip Sel (WCS[0:1])

CLK (CLK)

Clock Enable (CE)

Write/Comp Data

(WD[0:31])

128X48

CAM

Write Address

(WAD[0:6])

WR Mask Reg (WR_MASK)

WR don t care (WR_DC)

RESET

CLK0

CLK3

CLK1

CLK2

CAM

Output

CO[0:6]

Match

Out

MATCH

Multi-

match

Out

MUL_MATCH

相关PDF资料 |

PDF描述 |

|---|---|

| LC5768MC-75F256I | |

| LC5768MB-75F484C | |

| LC51024MC-52F484C | |

| LC5512MC-75F484I | |

| LC5512MB-75Q208I | |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LC5512MB-45Q208I | 制造商:LATTICE 制造商全称:Lattice Semiconductor 功能描述:3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5512MB-45Q256C | 制造商:LATTICE 制造商全称:Lattice Semiconductor 功能描述:3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5512MB-45Q256I | 制造商:LATTICE 制造商全称:Lattice Semiconductor 功能描述:3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5512MB-45Q484C | 制造商:LATTICE 制造商全称:Lattice Semiconductor 功能描述:3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5512MB-45Q484I | 制造商:LATTICE 制造商全称:Lattice Semiconductor 功能描述:3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

发布紧急采购,3分钟左右您将得到回复。